Method for mixing FPGA and CPU in rail

A hybrid loading and configuration file technology, applied in the field of communication, can solve the problems of reducing utilization rate, increasing space and cost, and achieving the effect of improving reliability, saving use space and cost, and improving anti-radiation ability.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] Hereinafter, the present invention will be described in detail based on the drawings.

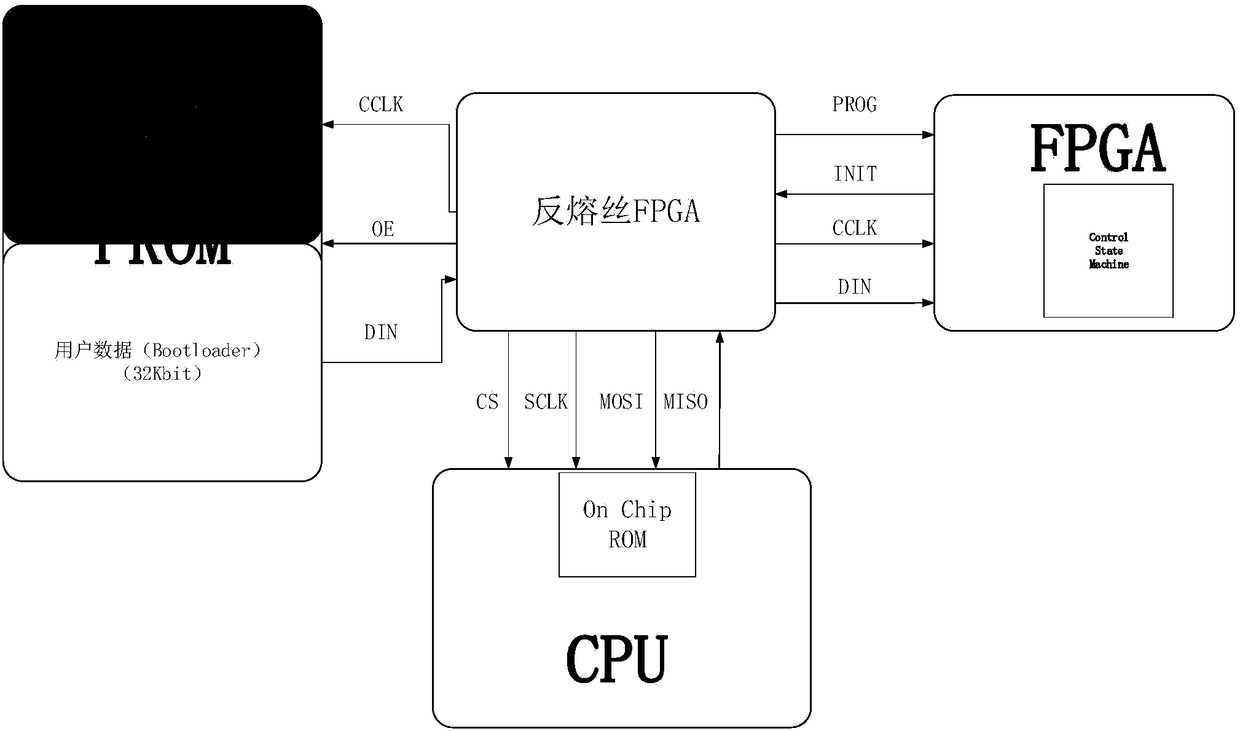

[0027] Such as figure 1 As shown, the present invention proposes a method for on-rail mixed loading of FPGA and CPU, and realizes the on-rail loading function of CPU and SRAM-type FPGA through the architecture of anti-fuse FPGA, SRAM-type FPGA, PROM, and CPU, and anti-fuse FPGA As the core of the architecture, the anti-fuse FPGA can flexibly choose to load CPU or SRAM type FPGA, and load the FPGA configuration file with the CPU configuration file.

[0028] The method of the present invention specifically comprises the steps:

[0029] Step 1. According to the requirements of SRAM-type FPGA, perform operations such as comprehensive compilation, layout and routing on FPGA through FPGA compiling software, and generate a configuration file for PROM storage and SRAM-type FPGA loading, such as *.mcs file.

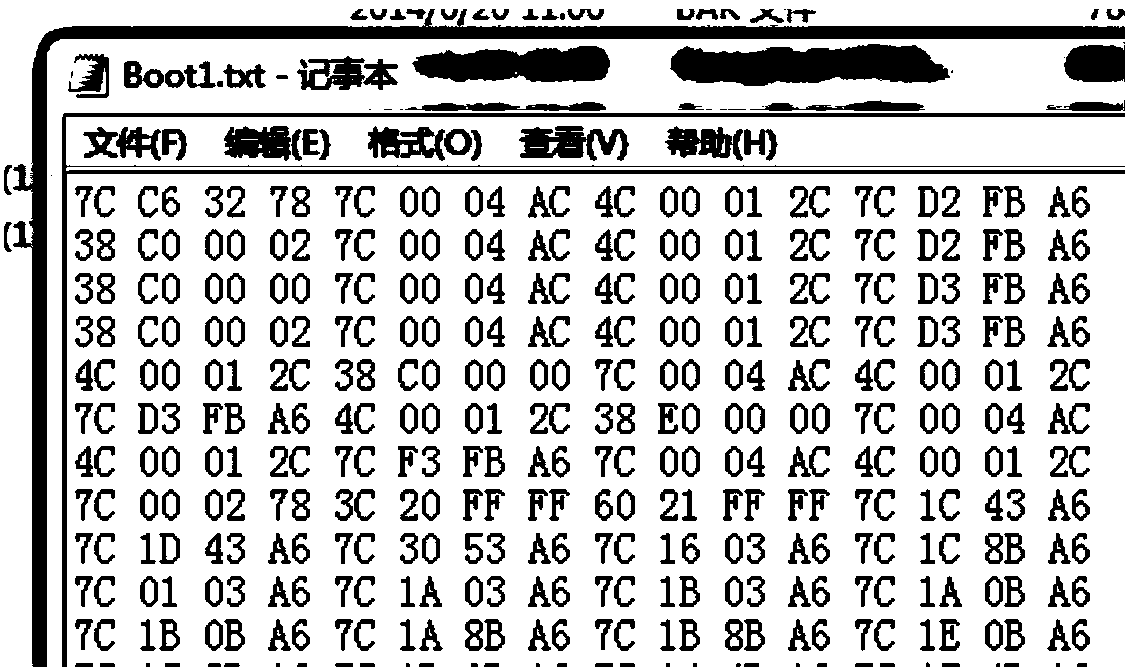

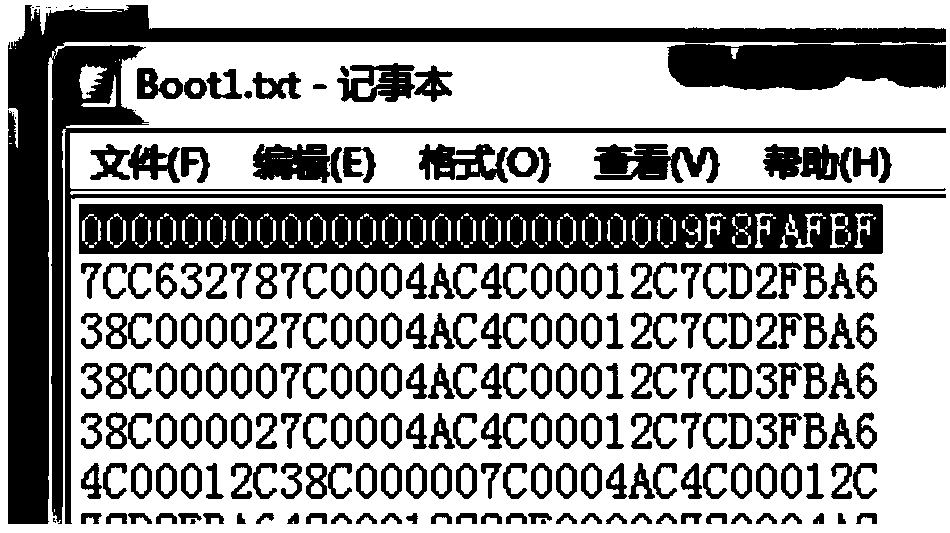

[0030] Step 2, add the synchronous word command to the generated CPU boot software...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More