A duty cycle stable and low jitter clock circuit

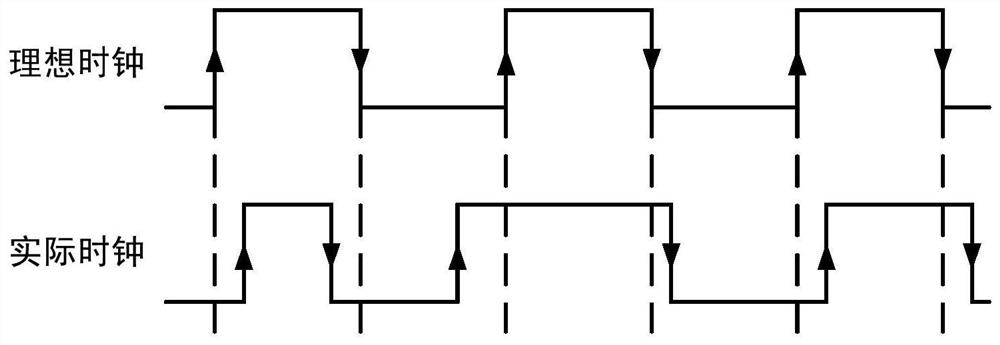

A clock circuit, low jitter technology, applied in electrical components, pulse technology, pulse processing, etc., can solve problems such as the inability to obtain duty cycle and accuracy stably, and cannot meet the requirements of the A/D converter system, so as to improve convergence speed, reduce jitter, reduce the effect of jitter

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

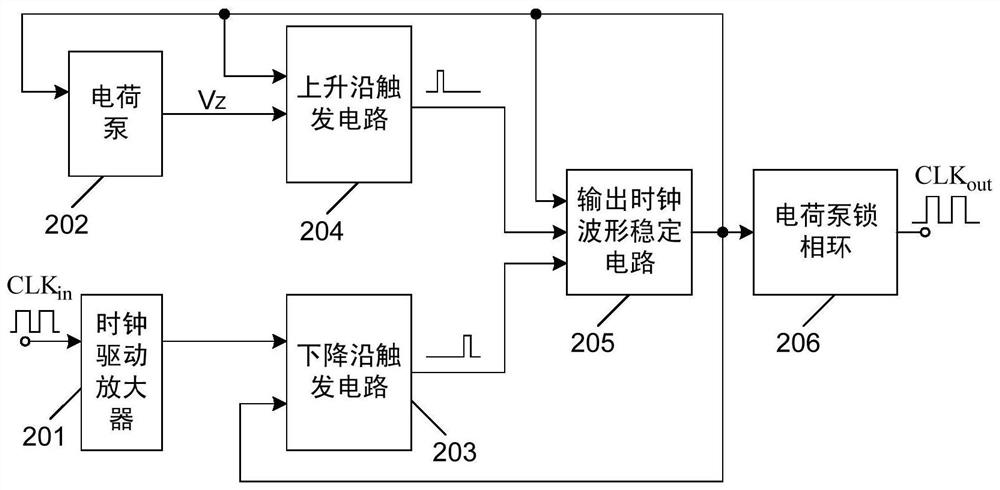

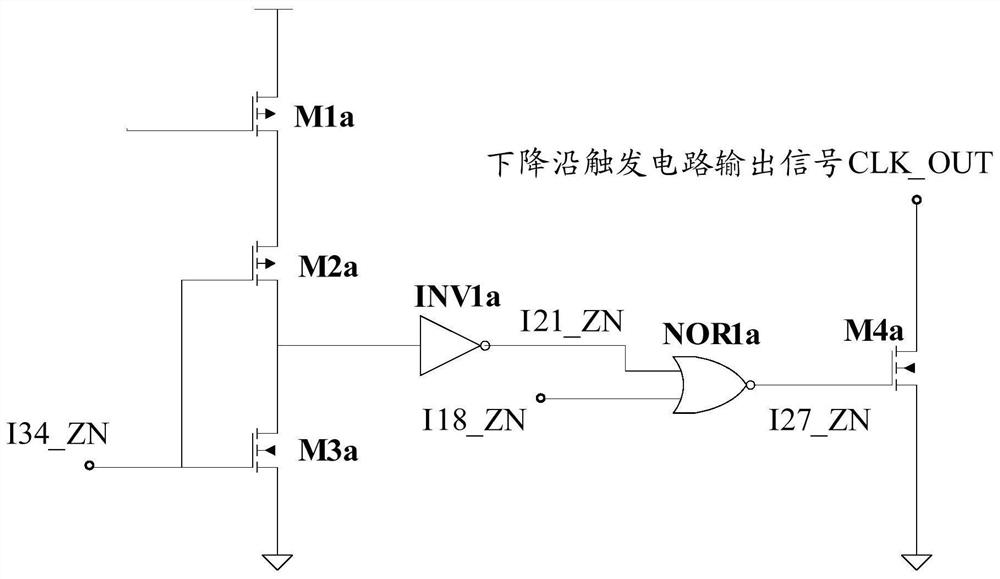

Method used

Image

Examples

Embodiment Construction

[0033] Exemplary embodiments of the present disclosure will be described in more detail below with reference to the accompanying drawings. Although exemplary embodiments of the present disclosure are shown in the drawings, it should be understood that the present disclosure may be embodied in various forms and should not be limited by the embodiments set forth herein. Rather, these embodiments are provided for more thorough understanding of the present disclosure and to fully convey the scope of the present disclosure to those skilled in the art. It should be noted that, in the case of no conflict, the embodiments of the present invention and the features in the embodiments can be combined with each other. The present invention will be described in detail below with reference to the accompanying drawings and examples.

[0034] As the demand for clock speed in communication systems has gradually expanded to the GHz range, certain performances of clocks, such as phase noise and...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More