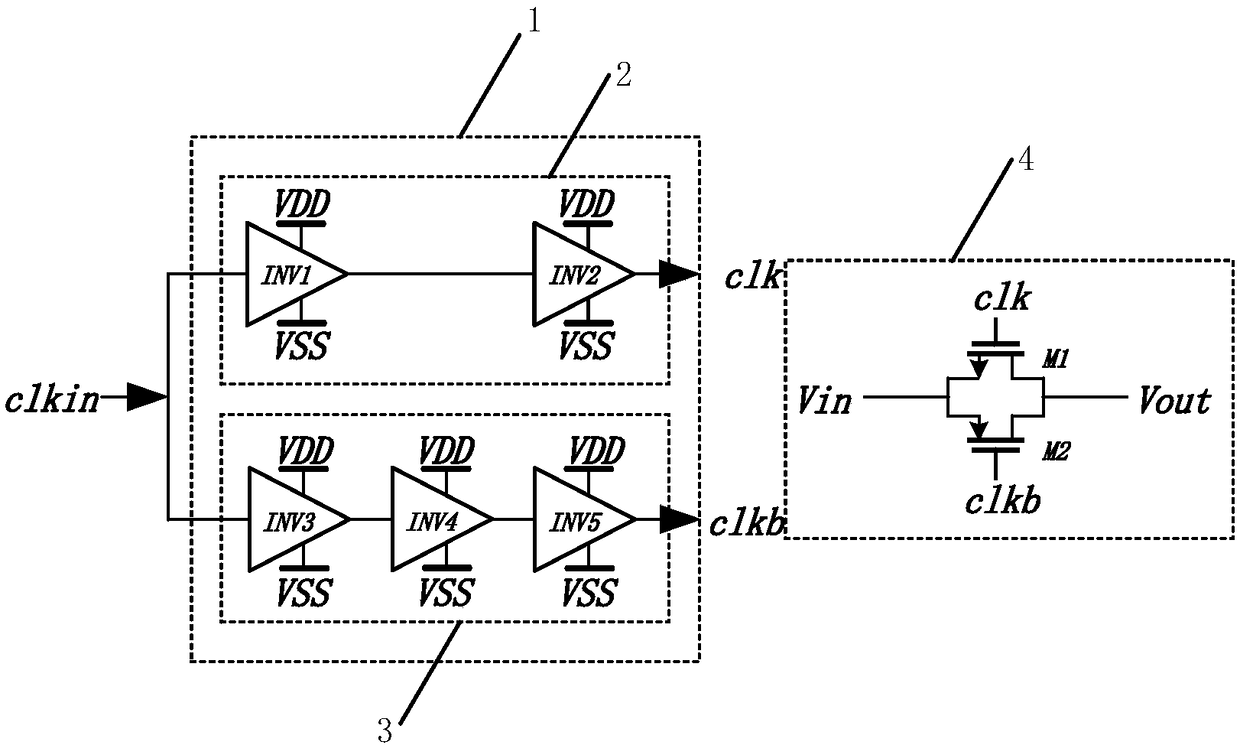

High-speed CMOS transmission gate switch circuit

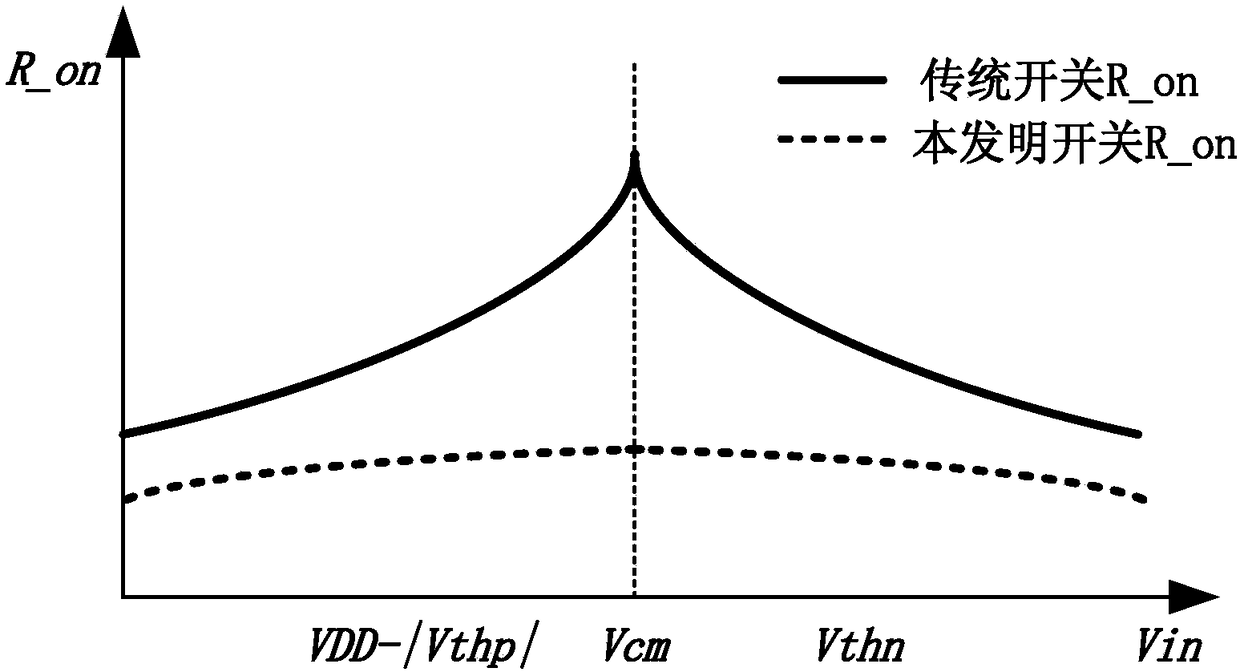

A switching circuit and transmission gate technology, applied in the field of high-speed CMOS transmission gate switching circuit, can solve the problems of increasing signal load, excessive conduction resistance, limiting signal transmission speed, etc. Effects of drive voltage, increased bandwidth, and linearity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

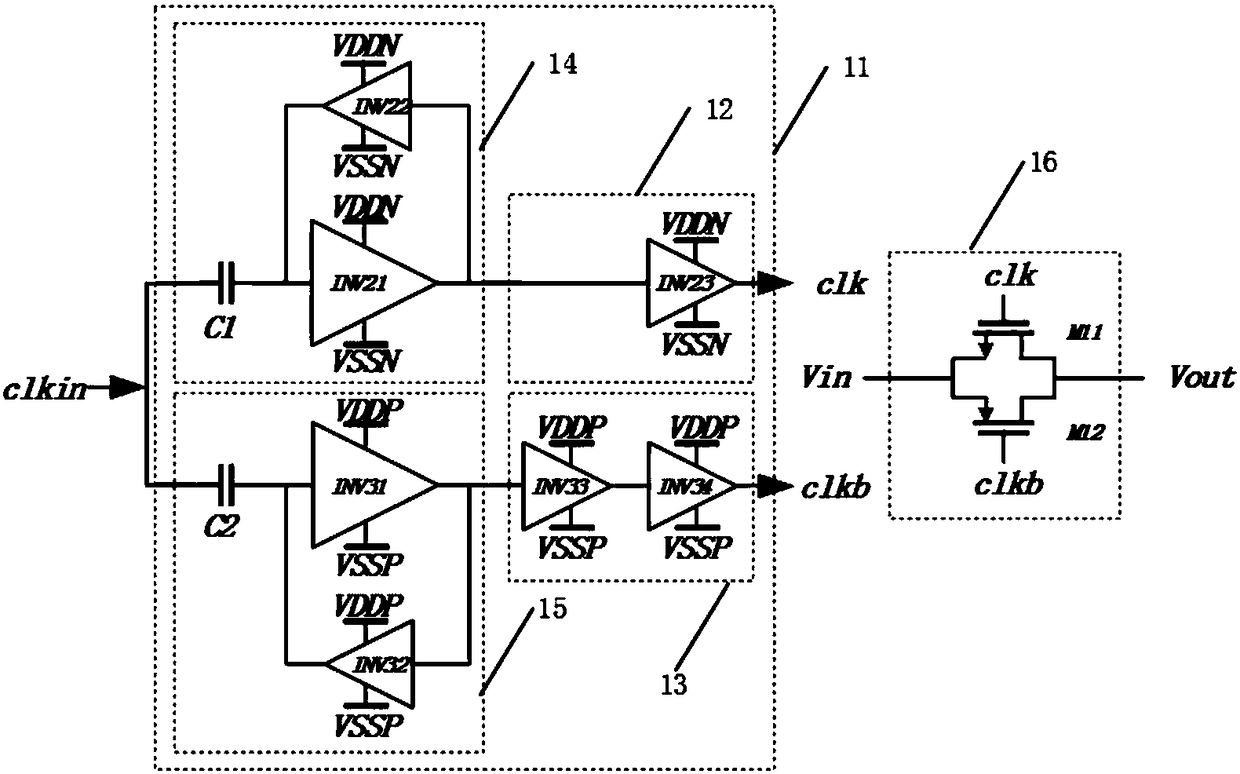

[0019] In order to make the object, technical solution and advantages of the present invention clearer, the implementation of the present invention will be further described in detail below in conjunction with the accompanying drawings.

[0020] The structure of the CMOS transmission gate switch circuit of the embodiment of the present invention is as follows figure 2 As shown, the circuit includes:

[0021] The clock control circuit 11 with level shifting includes two sub-channels, the signal input terminals of the two sub-channels are connected to the clock signal clkin at the same time; the first sub-channel is used to make the input voltage amplitude between [VDD, VSS] The clock signal clkin Shift up to become the same-phase clock signal clk with a voltage amplitude between [VDDN, VSSN], which is output from the signal output terminal of the first sub-channel; the second sub-channel is used to make the input voltage amplitude between [VDD, VSS] The clock signal clkin bet...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com