Capacitor array structure and manufacturing method thereof

An array structure and capacitor technology, which is applied in the direction of electric solid-state devices, circuits, electrical components, etc., can solve problems such as the decline in the storage capacity of capacitors, the increase in the leakage rate of capacitors, and the decrease in the stability of capacitor electrical connections, so as to improve the stability of electrical connections , reduce the leakage rate, and ensure the effect of charge storage capacity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

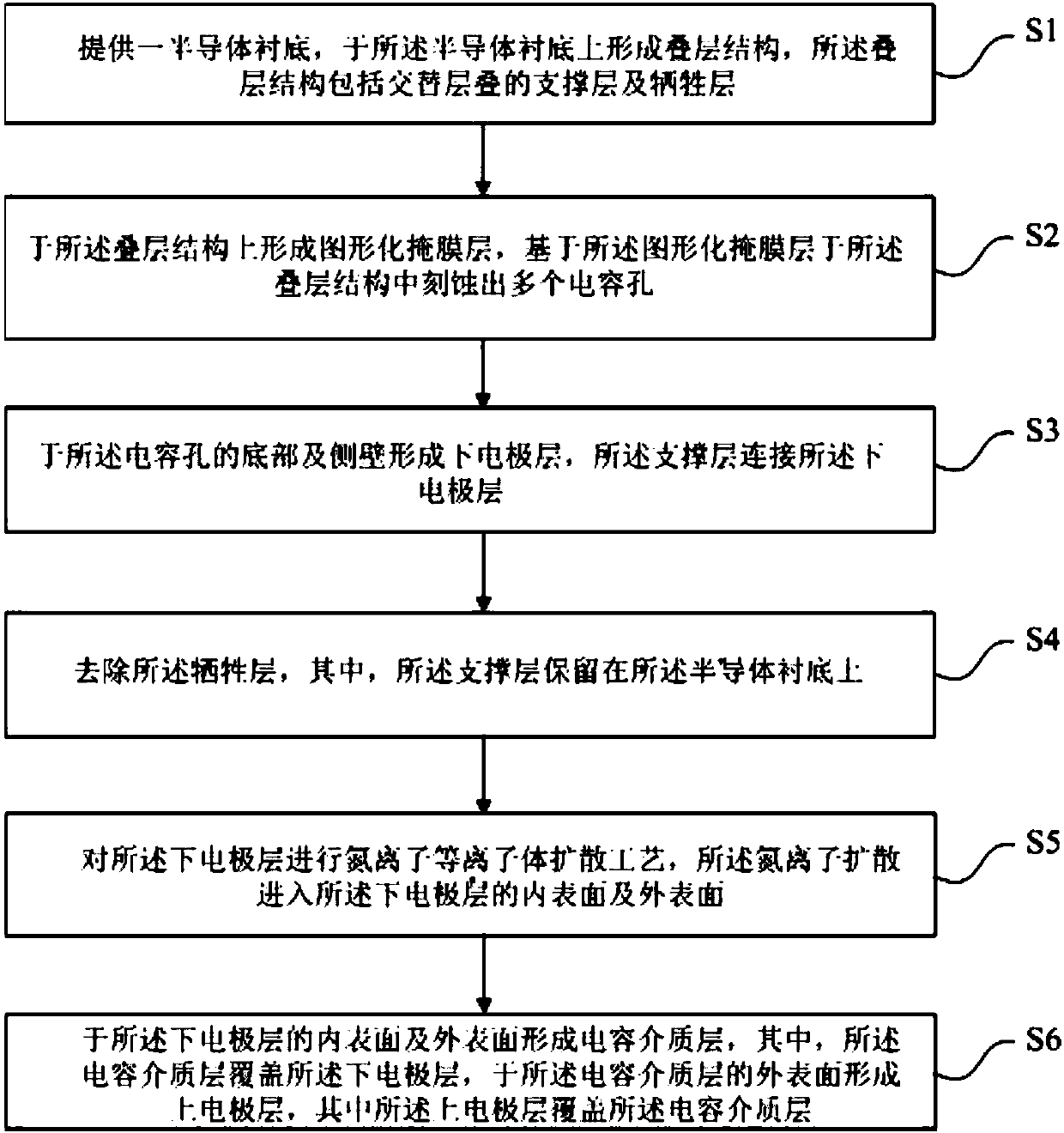

[0115] see figure 2 , the present embodiment provides a method for preparing a capacitor array structure, the method for preparing a capacitor array structure includes the following steps:

[0116] 1) A semiconductor substrate is provided, and a stacked structure is formed on the semiconductor substrate, the stacked structure comprising alternately stacked support layers and sacrificial layers;

[0117] 2) forming a patterned mask layer on the stacked structure, and etching a plurality of capacitance holes in the stacked structure based on the patterned mask layer;

[0118] 3) forming a lower electrode layer on the bottom and side walls of the capacitor hole, and the supporting layer is connected to the lower electrode layer;

[0119] 4) removing the sacrificial layer, wherein the support layer remains on the semiconductor substrate;

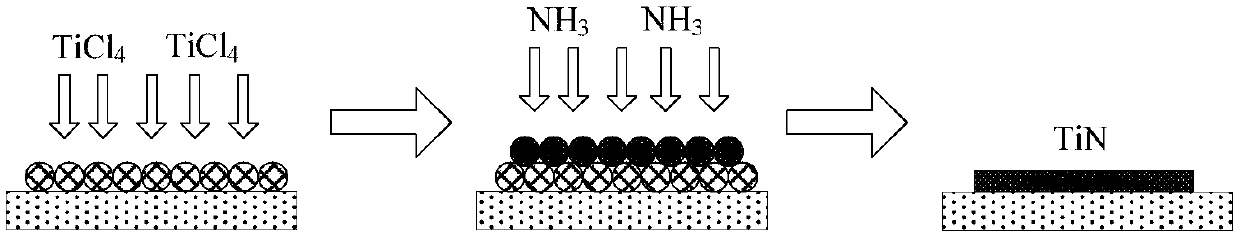

[0120] 5) performing a nitrogen ion plasma diffusion process on the lower electrode layer, and the nitrogen ions diffuse into the inner surf...

Embodiment 2

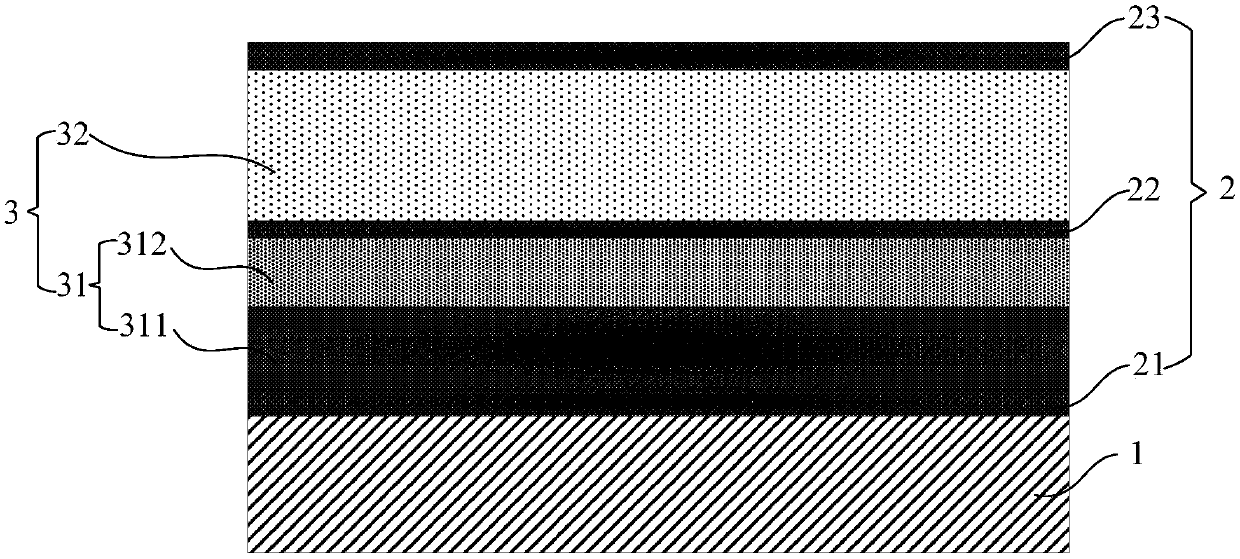

[0163] Please continue to refer to Embodiment 1 Figure 14 , the present invention also provides a capacitor array structure, wherein the capacitor array structure is preferably prepared by the preparation method of the present invention, of course, is not limited thereto, and the capacitor array structure includes:

[0164] semiconductor substrate 1;

[0165] The lower electrode layer 6 is formed on the semiconductor substrate 1, the cross-sectional shape of the lower electrode layer 6 includes a U shape, and the inner surface and the outer surface of the lower electrode layer 6 are diffusely implanted with nitrogen ions;

[0166] a capacitor dielectric layer 7 covering the inner and outer surfaces of the lower electrode layer 6;

[0167] The upper electrode layer 8 covers the outer surface of the capacitor dielectric layer 7 .

[0168] Wherein, the nitrogen ions diffused and implanted on the inner and outer surfaces of the lower electrode layer 6 can squeeze out the impuri...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More