LDMOS device and manufacturing method therefor

A manufacturing method and device technology, applied in the direction of semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of high manufacturing cost and complex manufacturing process, achieve low on-resistance, improve integration, and reduce conduction. The effect of resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

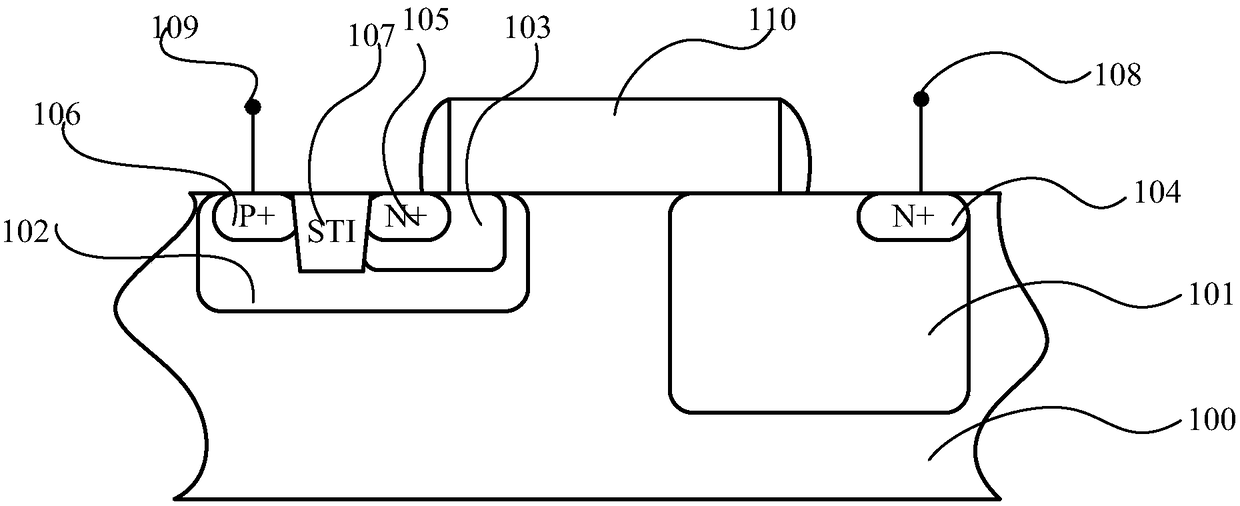

[0040] Please refer to figure 1 , an LDMOS device comprising: a semiconductor substrate 100, a drift region 101 and a deep well 102 arranged in the semiconductor substrate 100, a body region 103 arranged in the deep well 102, a gate arranged on the semiconductor substrate 100 A pole structure 110, a source region 105, a body contact region 106 and a shallow trench isolation structure 107 disposed in the body region 103, and electrodes 108 and 109 drawn from the drain region 104 and the body contact region 106, respectively. The body contact region 106 is used to adjust and control the potential of the body region 103, the doping types of the drift region 101 and the deep well 102 are opposite, and the doping type of the body region 103 and the deep well 102 are the same, thereby increasing the breakdown voltage and reduce the on-resistance. In this typical LDMOS device structure, due to the formation of the drift region 101 and the deep well 102, two deep well implant masks a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com