Electronic package and substrate construction thereof

一种电子封装件、电子元件的技术,应用在电气元件、电固体器件、电路等方向,能够解决封装基板18裂开、焊球12不沾锡、可靠度问题等问题,达到降低制程时间、降低制作成本、提升可靠度的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

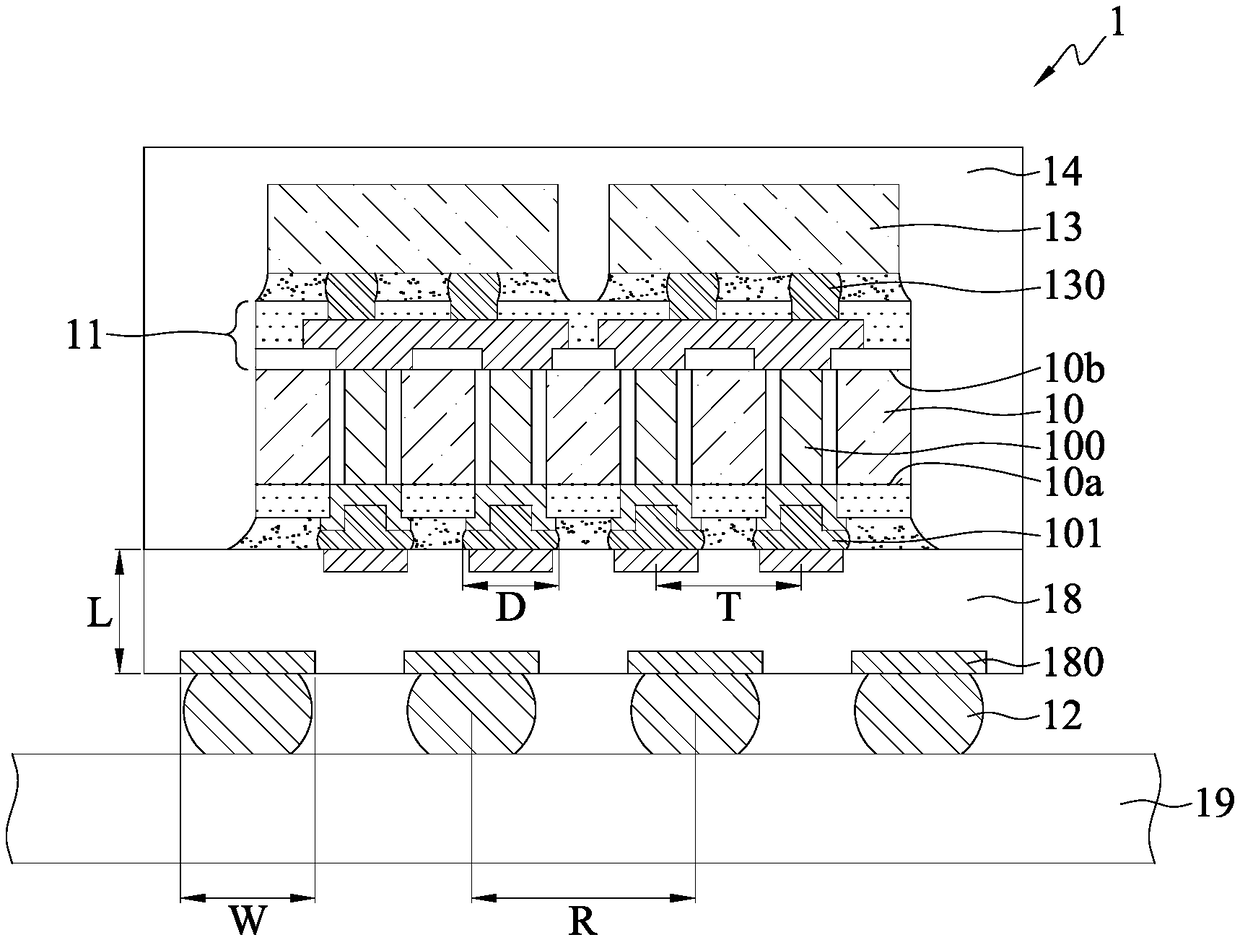

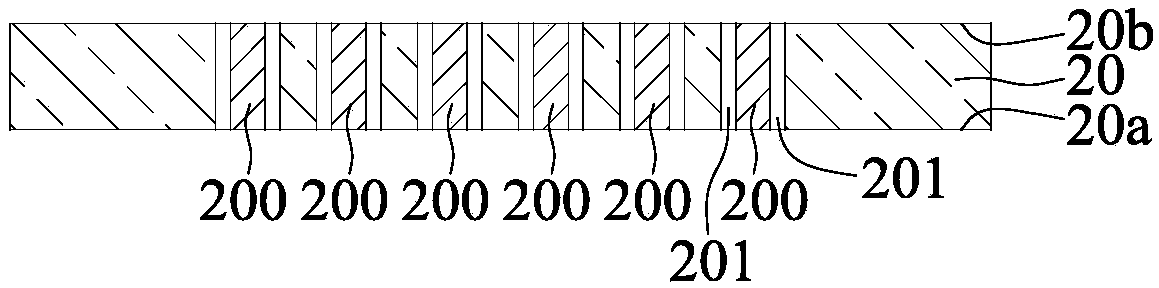

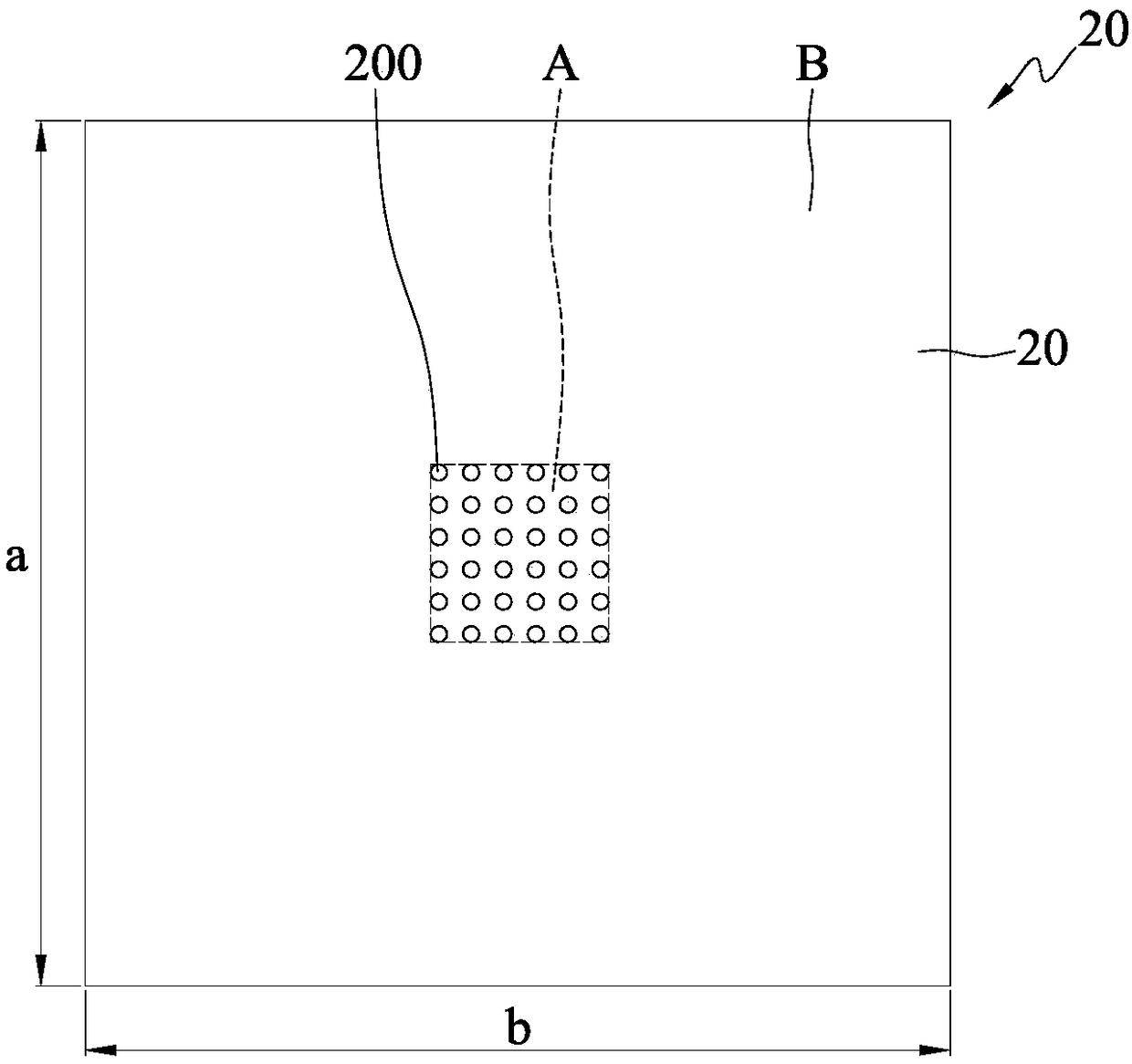

[0062] The embodiments of the present invention are described below through specific specific examples, and those skilled in the art can easily understand other advantages and effects of the present invention from the contents disclosed in this specification.

[0063] It should be noted that the structures, proportions, sizes, etc. shown in the drawings in this specification are only used to cooperate with the contents disclosed in the specification for the understanding and reading of those skilled in the art, and are not used to limit the implementation of the present invention. Restricted conditions, it does not have technical substantive significance, any structural modification, proportional relationship change or size adjustment, without affecting the effect that the present invention can produce and the purpose that can be achieved, should still fall within the present invention. The disclosed technical content must be within the scope of coverage. Meanwhile, terms such...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com