Method for manufacturing field effect transistor and semiconductor device

A manufacturing method and technology of field effect transistors, which are applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as insufficient gate control capability and short channel effect, reduce short channel effect, and improve gate control. capacity and carrier concentration, and the effect of improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

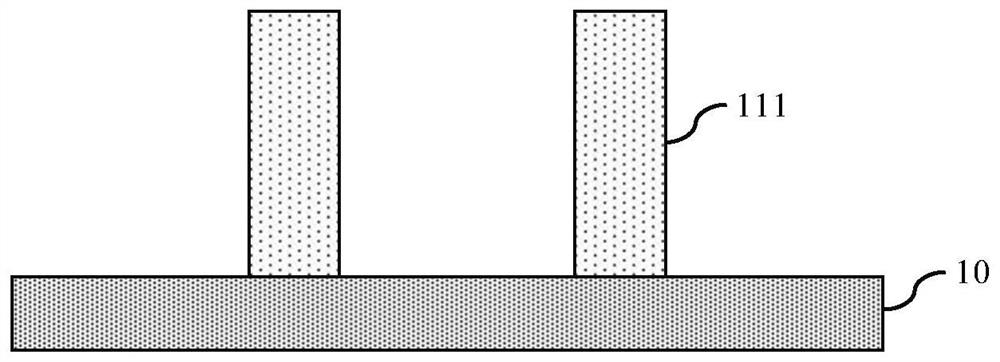

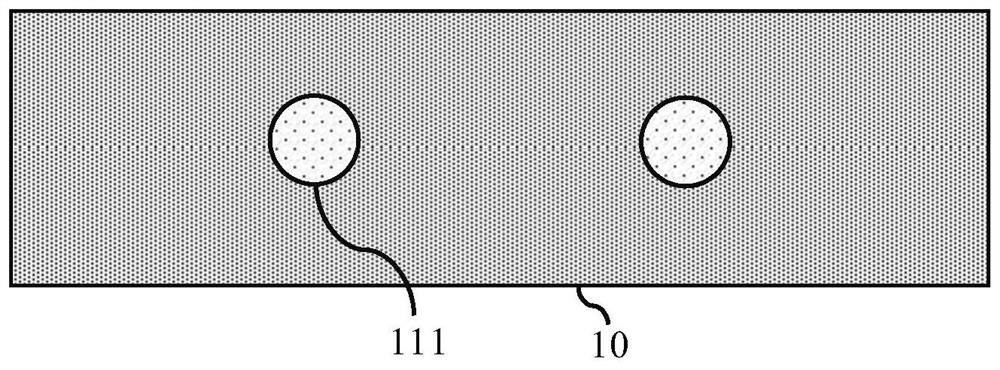

[0034] In order to make the purpose, advantages and characteristics of the present invention clearer, the following in conjunction with the attached Figure 1~2o' The manufacturing method of the field effect transistor and the semiconductor device proposed by the present invention will be further described in detail. It should be noted that all the drawings are in a very simplified form and use imprecise scales, and are only used to facilitate and clearly assist the purpose of illustrating the embodiments of the present invention.

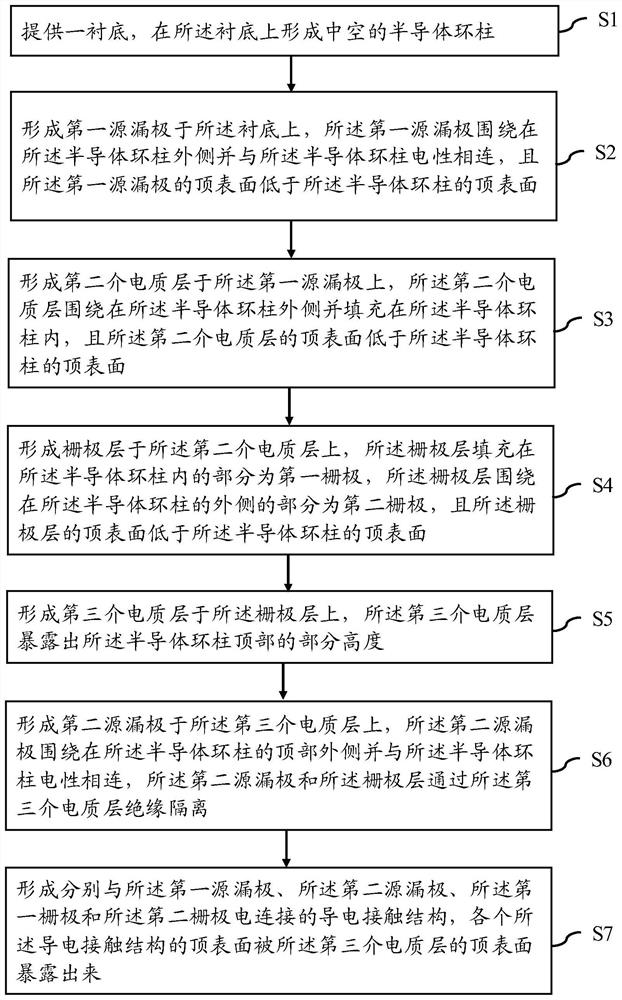

[0035] An embodiment of the present invention provides a method for manufacturing a field effect transistor, see figure 1 , figure 1 It is a flowchart of a method for manufacturing a field effect transistor according to an embodiment of the present invention, and the method for manufacturing a field effect transistor includes:

[0036] Step S1, providing a substrate, and forming a hollow semiconductor ring pillar on the substrate;

[0037] Step ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More