Semiconductor device and method of forming the same

A semiconductor and device technology, applied in the field of semiconductor devices and their formation, can solve the problems of reducing the concentration gradient of TFET LDD junction, device tunneling probability and on-state current reduction, TFET tunneling probability and driving current, etc. Transit probability and drive current, reduce thermal budget, increase the effect of concentration gradient

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

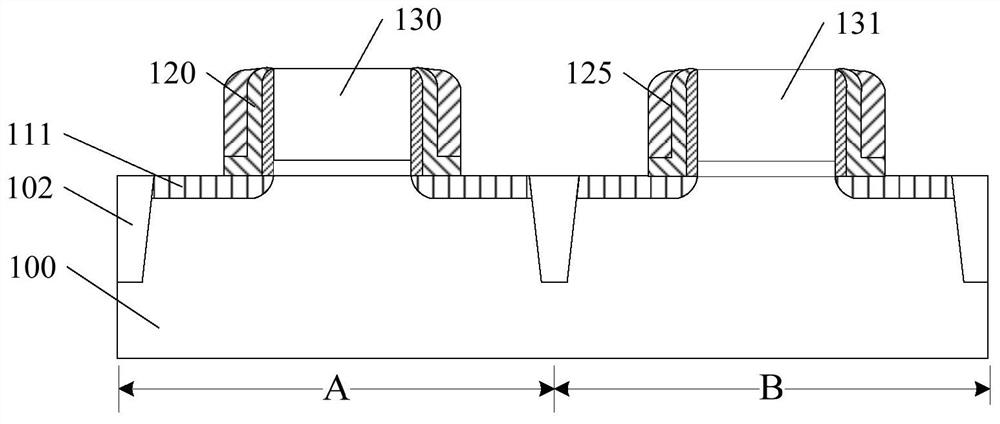

[0029] As mentioned in the background technology, in the existing TFET manufacturing process, both the TFET lightly doped drain process and the CMOS lightly doped drain process are performed before the LDD annealing process, for example, before the CMOS lightly doped drain process Or use the ion implantation process to form the TFET lightly doped drain region afterwards, so the dopant ions in the TFET lightly doped drain region will experience LDD Anneal and Source / Drain Anneal after forming the source and drain doped regions, because the high temperature in the annealing process will Affecting the thermal budget of the dopant ions in the lightly doped drain region of the TFET, and reducing the concentration gradient of the lightly doped drain region junction of the TFET, will easily lead to a decrease in the tunneling probability and driving current of the TFET, and a decrease in the tunneling probability and on-state current of the device.

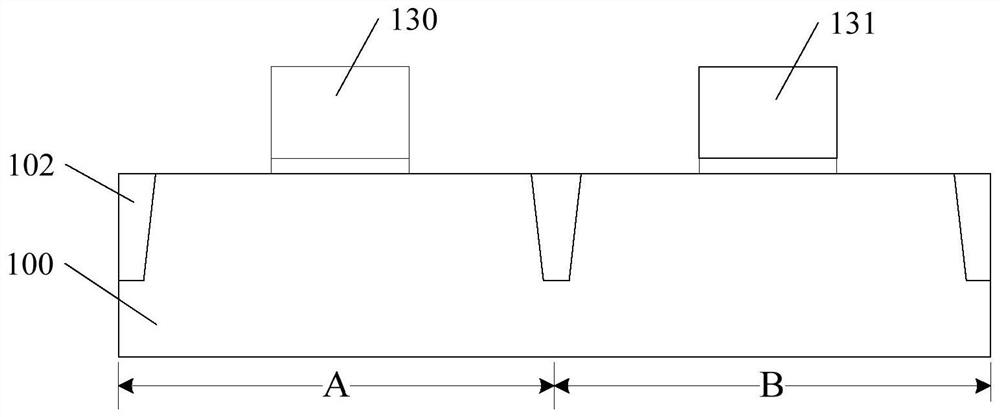

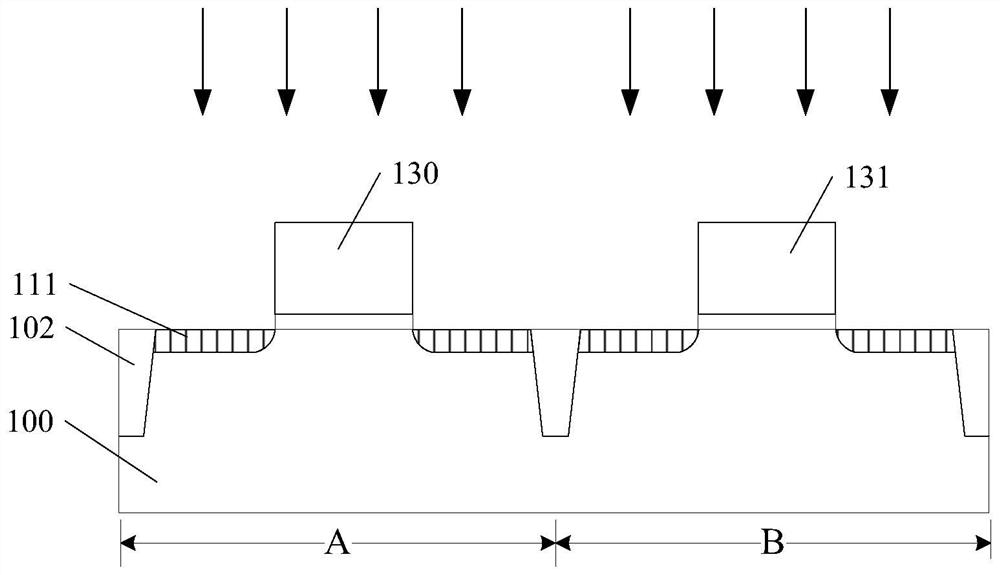

[0030] Figure 1 to Figure 4 It is...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More