Semiconductor device and manufacturing method thereof

A manufacturing method, semiconductor technology, applied in the direction of semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems that cannot meet the performance of MOSFET devices, can not completely eliminate short-channel effects and high leakage problems, and achieve improved short-circuit Channel effect, improvement of anti-short channel effect, effect of performance improvement

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

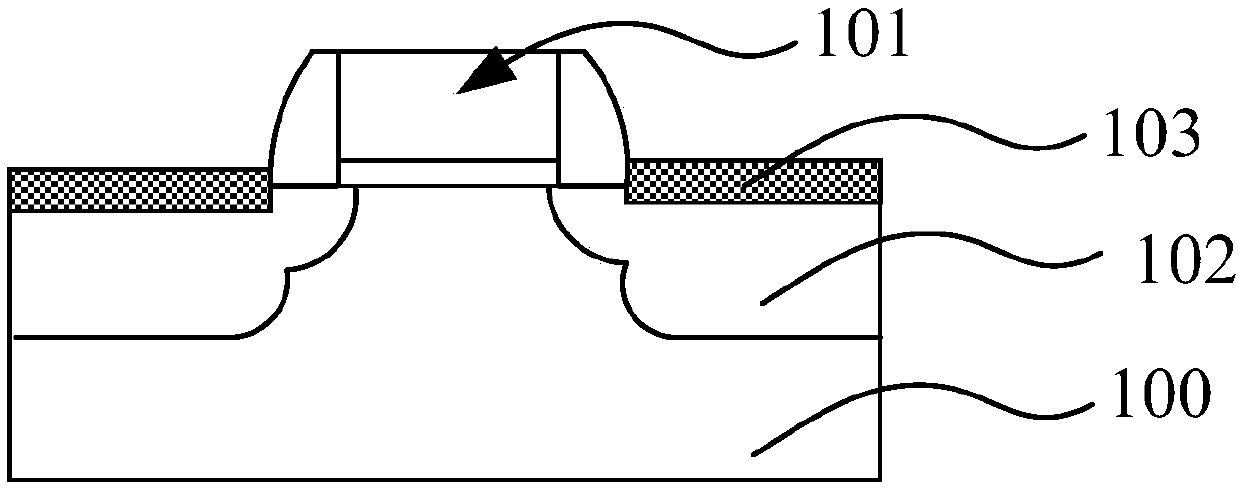

[0044] Please refer to figure 1 A MOS transistor includes a semiconductor substrate 100, a gate stack structure 101 formed on the surface of the semiconductor substrate 100, and LDD ion implantation regions 102 formed in the semiconductor substrate 100 on both sides of the gate stack structure 101 and The source and drain regions (i.e. source and drain regions) 103, the formation process of the source and drain regions 103 may include: etching the semiconductor substrate 100 on both sides of the gate stack structure 101 to form source and drain grooves; The growth process directly epitaxially grows a source-drain stress layer (silicon germanium for PMOS transistors and silicon carbon for NMOS transistors) in the source-drain grooves, thereby forming embedded source / drain regions 103 .

[0045]As mentioned in the background art, as the gate length of transistors shrinks, for example, after entering the 28nm technology node, the short channel effect (SCE) and the reverse short c...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More