Device and method for access control of multiple asynchronous interfaces inside a storage body

An asynchronous interface, access control technology, applied in the direction of instruments, electrical digital data processing, etc., to achieve the effect of reducing the number of control signals, precise and efficient control, flexible and efficient control

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

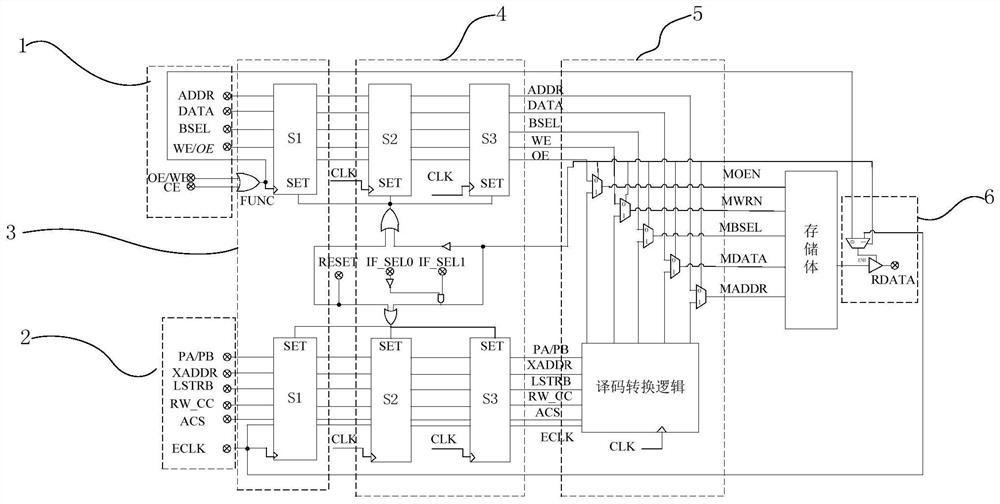

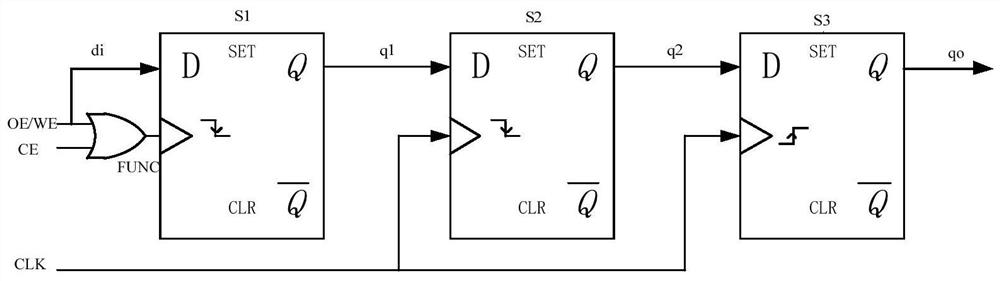

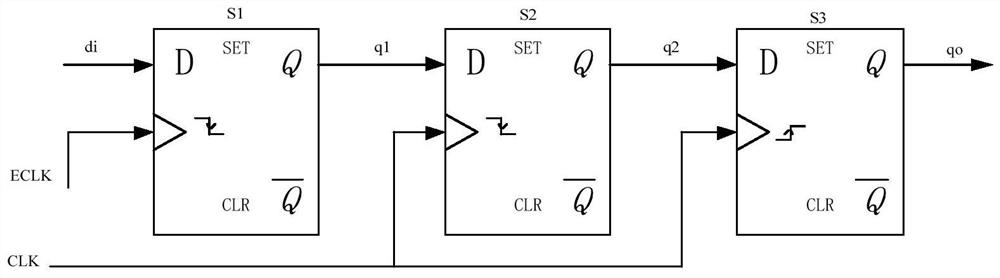

[0065] In this embodiment, the interfaces used are two asynchronous interfaces with different functions and timings. The first interface 1 is an interface without a control clock, and the second interface 2 is an interface with a control clock. The first interface 1 includes an address signal ADDR, a data signal DATA, a read / write signal WE / OE, a chip select signal CE and a byte select signal BSEL. The second interface 2 includes an address data signal PA / PB, an address comparison signal XADDR, a write signal RW_CC, a chip select signal ACS, an interface clock signal ECLK, and a byte select signal LSTRB. The port self-sampling unit 3 mainly implements the sampling of the signals of the first interface 1 and the second interface 2. For the first interface 1, the result of "OR" logic is performed on the two control signals of itself to sample other signals, and the second interface 2 passes The self-sampling signal ECLK realizes the sampling of other asynchronous signals. The s...

Embodiment 2

[0075] The invention has been successfully applied in a vehicle-mounted FlexRay control chip compatible with the FlexRay2.1A protocol, and realizes the access control of the 3-way asynchronous interface to the register of the on-chip 2KB addressing space and the 6KB memory. It effectively avoids access conflicts of multiple interfaces and realizes fast and reliable access to on-chip storage space. The FlexRay control chip has completed the loading test, and its functional performance meets the requirements for use.

[0076] In addition, the circuit design of a certain high-performance FlexRay type MCU also adopts the structure of the present invention. It also uses 3 asynchronous interfaces with different functions to access registers in the on-chip 2KB address space and 8KB capacity Memory. Through the design structure of the invention, the problem of extremely strict access timing of one of the interfaces is realized, the design flexibility is improved, and the design compl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More