Planar gate device structure having high switching speed and manufacturing method thereof

A technology of switching speed and device structure, used in semiconductor devices, electrical components, circuits, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

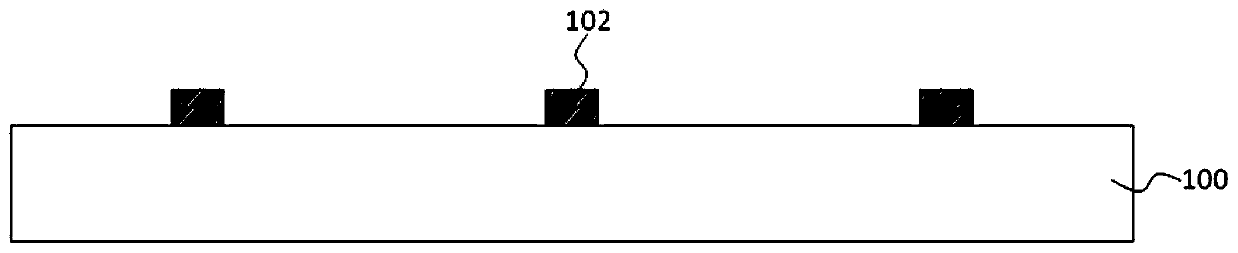

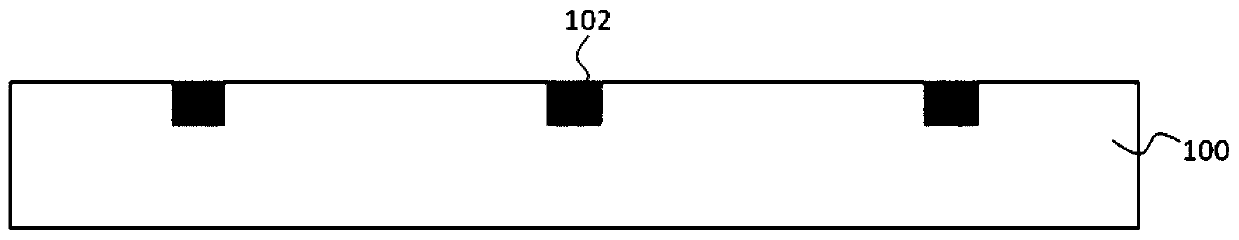

[0044] A planar gate device structure with high switching speed, such as Figure 7a As shown, a semiconductor substrate or epitaxial layer 100 is included, and a group of planar gates 10 are arranged on the surface of the semiconductor substrate or epitaxial layer 100 . The planar gate 10 includes a first gate electrode insulating layer 102 arranged in the middle, and the first gate electrode insulating layer 102 extends upward from the surface of the semiconductor substrate or the epitaxial layer 100 to protrude from the semiconductor substrate or the epitaxial layer 100 s surface. The second gate electrode insulating layer 103 extending from the first gate electrode insulating layer 102 to both sides and the gate electrode 104 arranged on the first gate electrode insulating layer 102 and the second gate electrode insulating layer 103, the first gate electrode The thickness of the insulating layer 102 is greater than that of the second gate electrode insulating layer 103 . ...

Embodiment 2

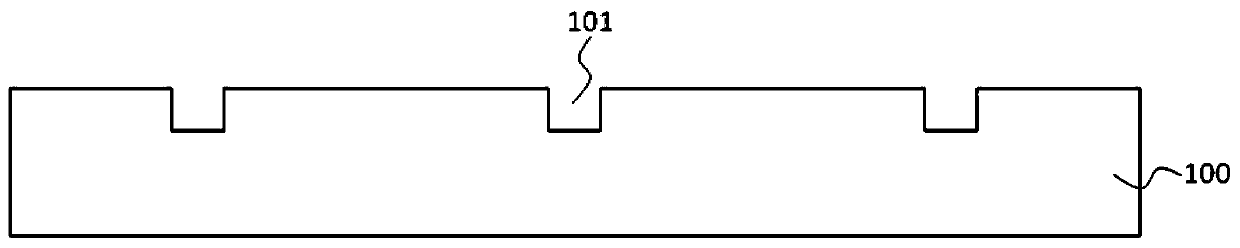

[0062] A planar gate device structure with high switching speed, such as Figure 7b As shown, it includes a semiconductor substrate or an epitaxial layer 100, and a group of planar gates 10 are arranged on the surface of the semiconductor substrate or epitaxial layer 100, and the planar gate 10 includes a first gate electrode insulating layer 102 arranged in the middle, so The first gate electrode insulating layer 102 extends downward from the surface of the semiconductor substrate or the epitaxial layer 100 and sinks into the semiconductor substrate or the epitaxial layer 100 . And the distance between the first gate insulating layer 102 and the first doped region 105 is greater than the carrier diffusion length between the first gate insulating layer 102 and the first doped region 105 when the device is turned on. The second gate electrode insulating layer 103 extending from the first gate electrode insulating layer 102 to both sides and the gate electrode 104 arranged on th...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More