Miniaturized high-density system-level logic circuit

A logic circuit, high-density technology, applied in logic circuits, logic circuits using specific components, logic circuits using basic logic circuit components, etc. The PAD arrangement is simple and reasonable, the number of PADs is reduced, and the circuit volume is reduced.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

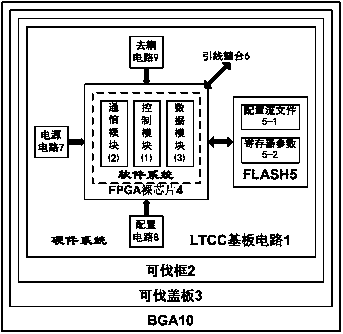

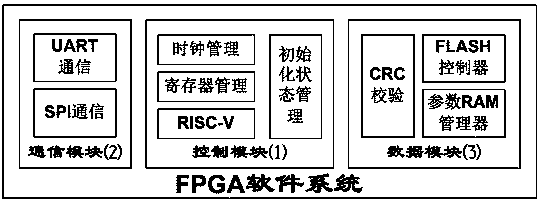

[0107] combine Figure 2~Figure 4 , the logic circuit hardware system provided by the present invention is composed of 10 parts, including LTCC substrate circuit 1, Kovar frame 2, Kovar cover plate 3, FPGA bare chip 4, FLASH bare chip 5, wire bonding 6, power supply circuit 7, Configuration circuit 8, decoupling circuit 9 and BGA10.

[0108] Such as Figure 5 As shown, the logic circuit of the present invention adopts a chip stacking structure, and the FPGA bare chip 4 and the FLASH bare chip 5 are assembled on the TOP layer of the circuit through pyramidal stacking.

[0109] Such as Image 6 As shown, the logic circuit of the present invention adopts a wire bonding structure, including FPGA bare chip outer layer PAD4-1, FPGA bare chip inner layer PAD4-2, FLASH bare chip PAD5-1, ceramic base outer layer bonding PAD1-1 , Ceramic base middle layer bonding PAD1-2, ceramic base inner layer bonding PAD1-3, outer layer wire bonding 6-1, middle layer wire bonding 6-2, inner layer ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More