Semiconductor structure and forming method thereof

A technology of semiconductor and gate structure, which is applied in the field of semiconductor structure and its formation, can solve the problems of high process difficulty, device performance and yield decline, etc., and achieve the effect of simplifying process steps, reducing adverse effects, and reducing process difficulty

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

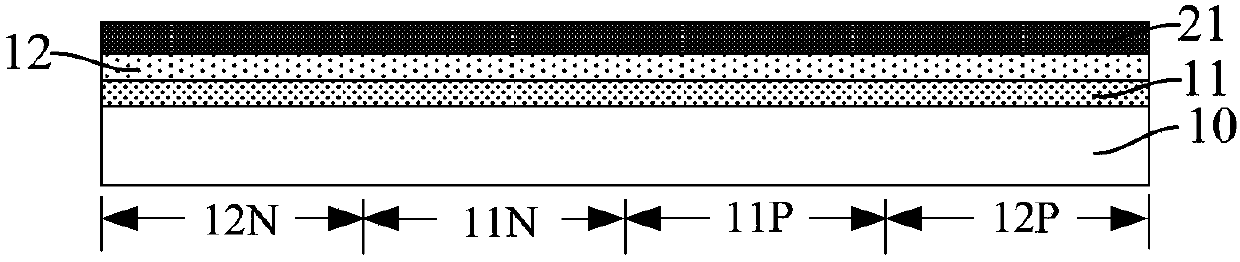

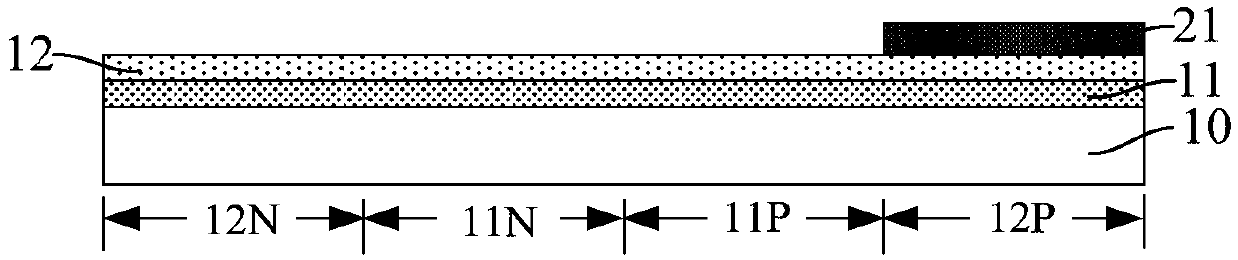

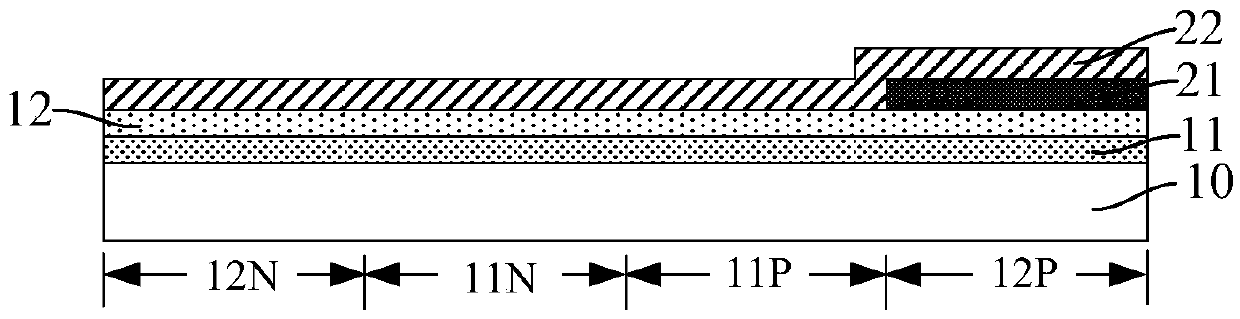

[0013] Lightly Doped Drain (LDD) implantation is the main process for accurately adjusting the threshold voltage of devices, but with the continuous reduction of the feature size of CMOS devices, the semiconductor process has gradually begun to shift from planar MOSFETs to three-dimensional three-dimensional ones with higher power efficiency. Transistor transitions such as Fin Field Effect Transistors (FinFETs). After the fin structure is introduced into the semiconductor structure, the effect of adjusting the threshold voltage of the device through the lightly doped drain implantation process will be correspondingly reduced. Therefore, at present, the multi-layer work function process (Multi-Work Function Process) is mainly used The NMOS device and the PMOS device have different threshold voltages.

[0014] In the multi-layer work function layer process, the doping ion concentration of the source and drain doping layers of each NMOS device is the same, and the doping ion conc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More