Cellular structure of silicon carbide VDMOS device and manufacturing method thereof

A technology of silicon carbide and devices, which is applied in the field of power semiconductor devices, can solve the problems of increasing the on-state resistance of the JFET area and reducing the dV/dt ability, and achieve the effects of improving the conduction ability, not being easy to open, and improving reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

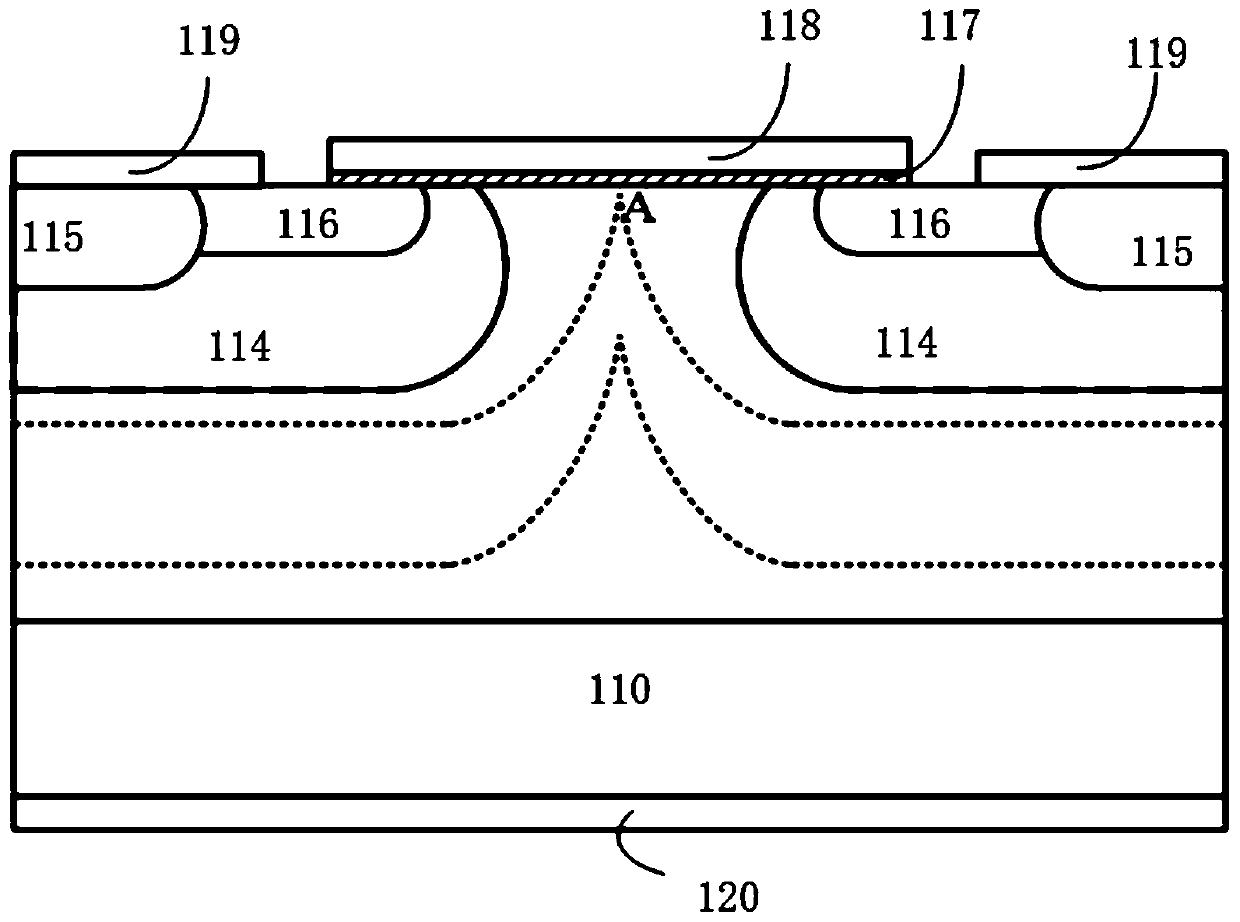

[0086] image 3 It is a schematic diagram of a cross-sectional structure of a silicon carbide VDMOSFET in this embodiment,

[0087] Figure 4 It is a schematic diagram of the electric field when the silicon carbide VDMOSFET is turned off in this embodiment.

[0088] The cell structure of a silicon carbide VDMOS device provided by this implementation, such as image 3 ,include:

[0089] The first conductivity type substrate 10, the first conductivity type drift region 11, the second conductivity type shielding region 12, the first conductivity type JFET injection region 13, the second conductivity type base region 14, the second conductivity type source region 15, the second conductivity type One conductivity type source region 16 , gate insulating layer 17 , gate 18 , source electrode 19 , drain electrode 20 .

[0090] When the SiC VDMOSFET is turned off, the electric field as Figure 4 , wherein the electric field distribution in the drift region 11 of the first conducti...

no. 2 example

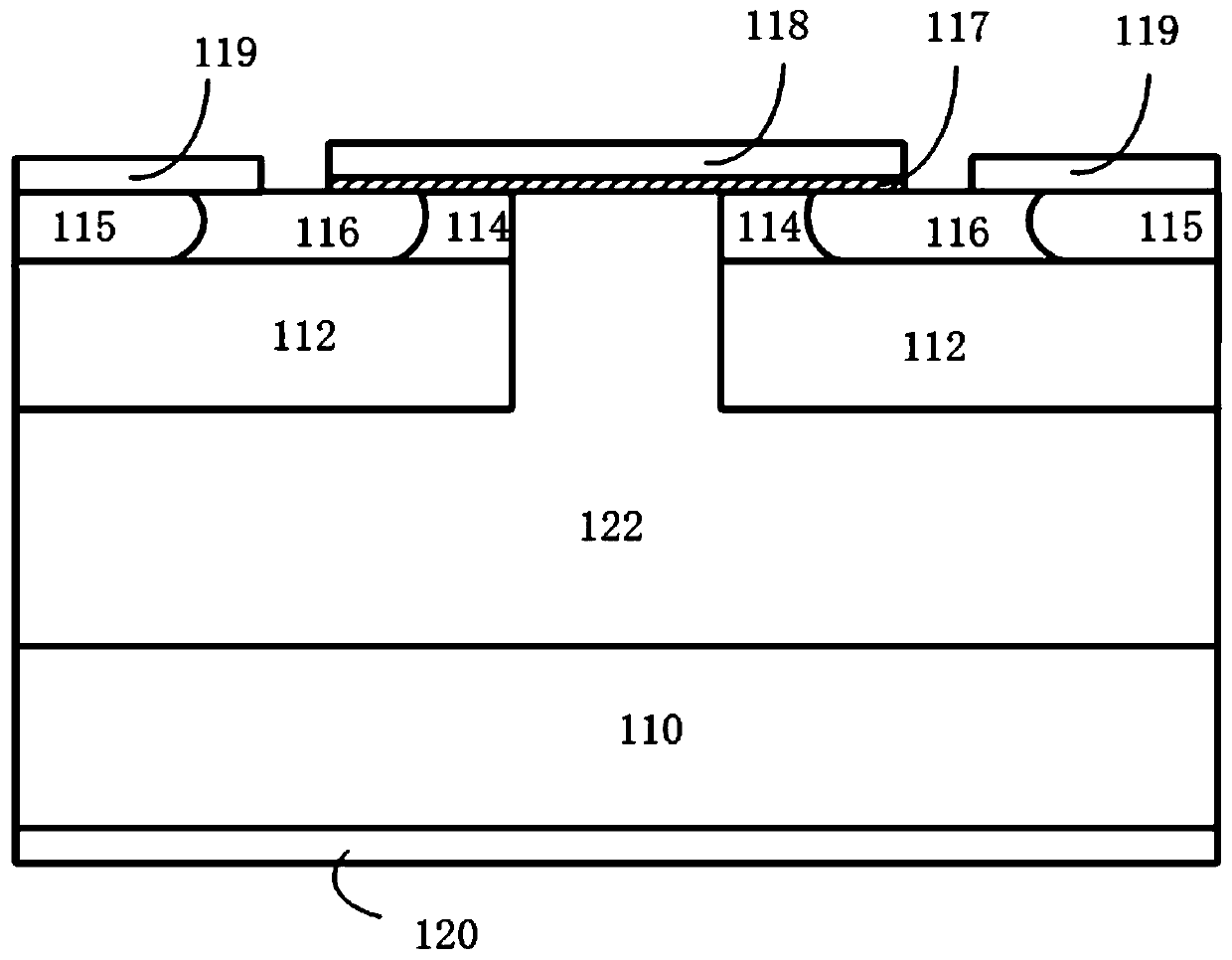

[0112] Figure 5 It is a schematic diagram of a cross-sectional structure of a silicon carbide VDMOSFET in this embodiment,

[0113] Figure 6 It is a schematic diagram of the electric field when the silicon carbide VDMOSFET is turned off in this embodiment.

[0114] The cell structure of a silicon carbide VDMOS device provided by this implementation, such as Figure 5 ,include:

[0115] The first conductivity type substrate 10, the first conductivity type drift region 11, the second conductivity type shielding region 12, the first conductivity type JFET injection region 13, the first conductivity type epitaxial region 21, the second conductivity type base region 14, the second conductivity type The second conductivity type source region 15 , the first conductivity type source region 16 , the gate insulating layer 17 , the gate 18 , the source electrode 19 , and the drain electrode 20 .

[0116] When the SiC VDMOSFET is turned off, the electric field as Figure 6 , wherei...

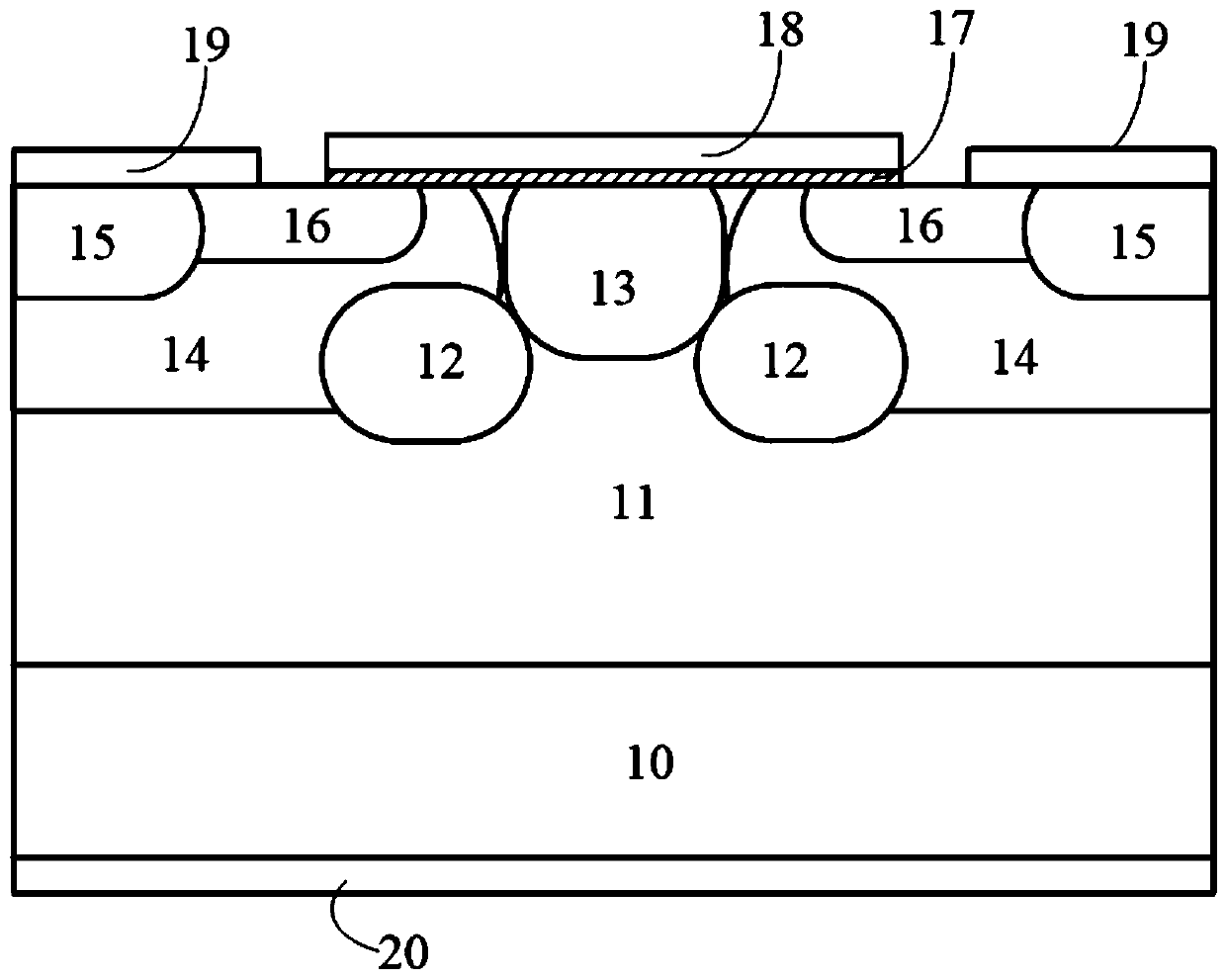

no. 3 example

[0140] Figure 7 It is a schematic flow chart of the fabrication method of the cell structure of the silicon carbide VDMOS device in this embodiment.

[0141] The present invention also provides a method for making a cell structure of a silicon carbide VDMOS device, the specific process is as follows Figure 7 , including the following steps:

[0142] S310, growing the drift region 11 of the first conductivity type on the substrate 10 of the first conductivity type, such as Figure 7.1 ;

[0143] Then form several shielding regions 12 of the second conductivity type, JFET injection regions 13 of the first conductivity type, base regions 14 of the second conductivity type, source regions 16 of the first conductivity type and source regions 15 of the second conductivity type, specifically,

[0144] S320, forming the shielding region 12 of the second conductivity type at a specified depth by implanting ions into the surface of the drift region 11 of the first conductivity type...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| electrical resistivity | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More