Packaging structure, semiconductor device and packaging method

A technology of packaging structure and chip unit, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve the problems of customer layer fracture, solder pad cracking, etc., to improve the isolation effect and stress strength. improved effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

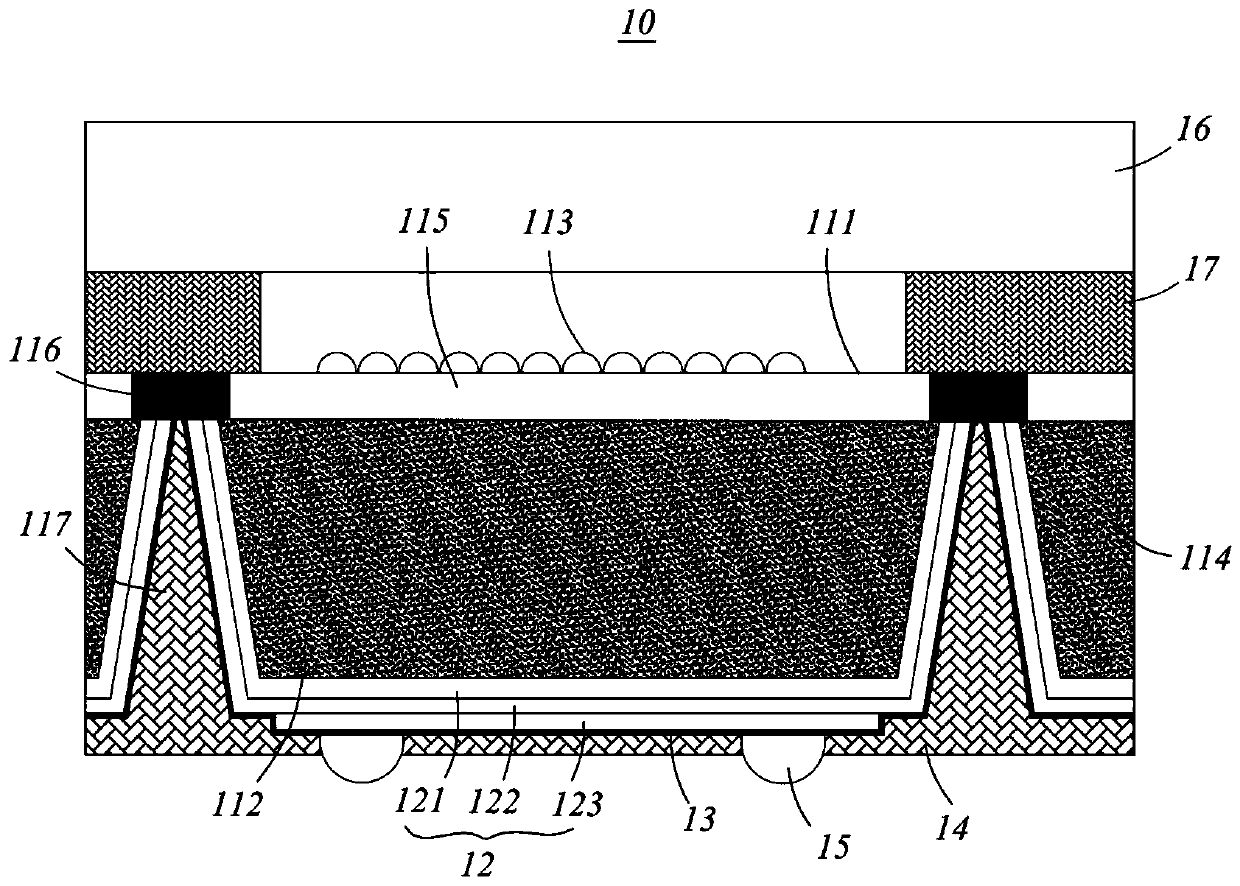

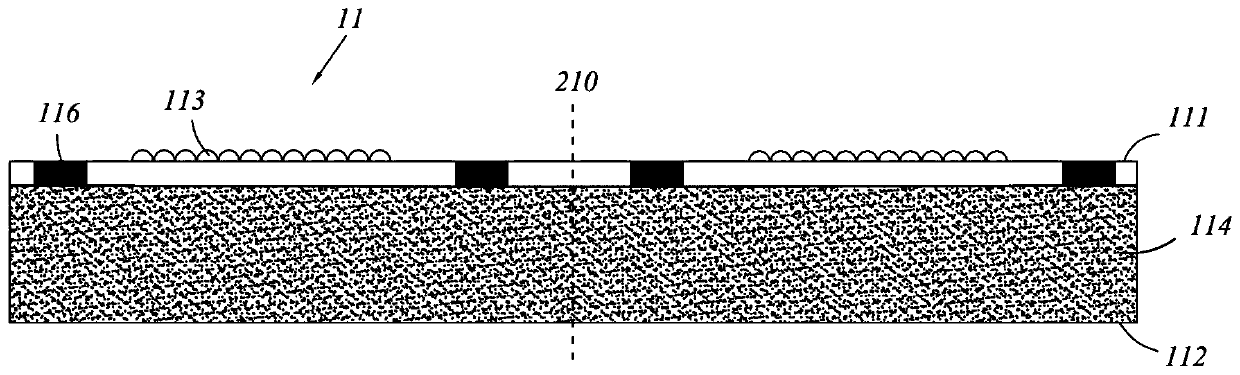

[0032] As mentioned in the background, in the existing package structure, the solder pad itself or the adjacent client layer are prone to breakage. The main reason is that in TSV (Through Silicon Via) packaging, SiO 2 Or organic materials such as epoxy resin are used as an insulating layer to cover the side walls of the through holes and connect to the pads. However, due to the large CTE (coefficient of thermal expansion) of the organic material, it is easy to pull the pads, causing the pads to break.

[0033] Aiming at the problems of the prior art, the main innovation of the embodiments of the present invention is that the insulating layer is made of SiO 2 +Si 3 N 4 + Epoxy resin three-layer structure, through this structure, the moisture insulation effect can be greatly improved, and the stress resistance strength of itself is also greatly improved, so it has a significant effect in resisting structural stress and reducing stress at the pad.

[0034] In order to make the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More