High-linearity wide-swing CMOS voltage follower

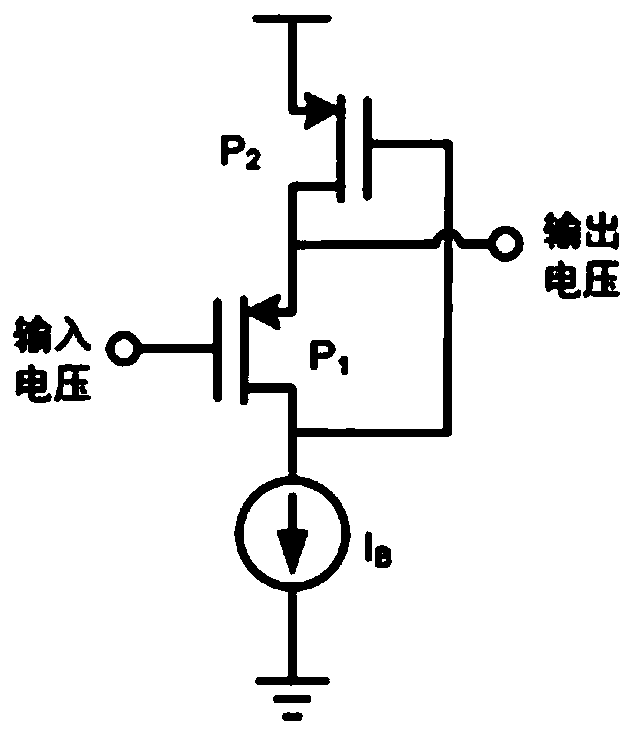

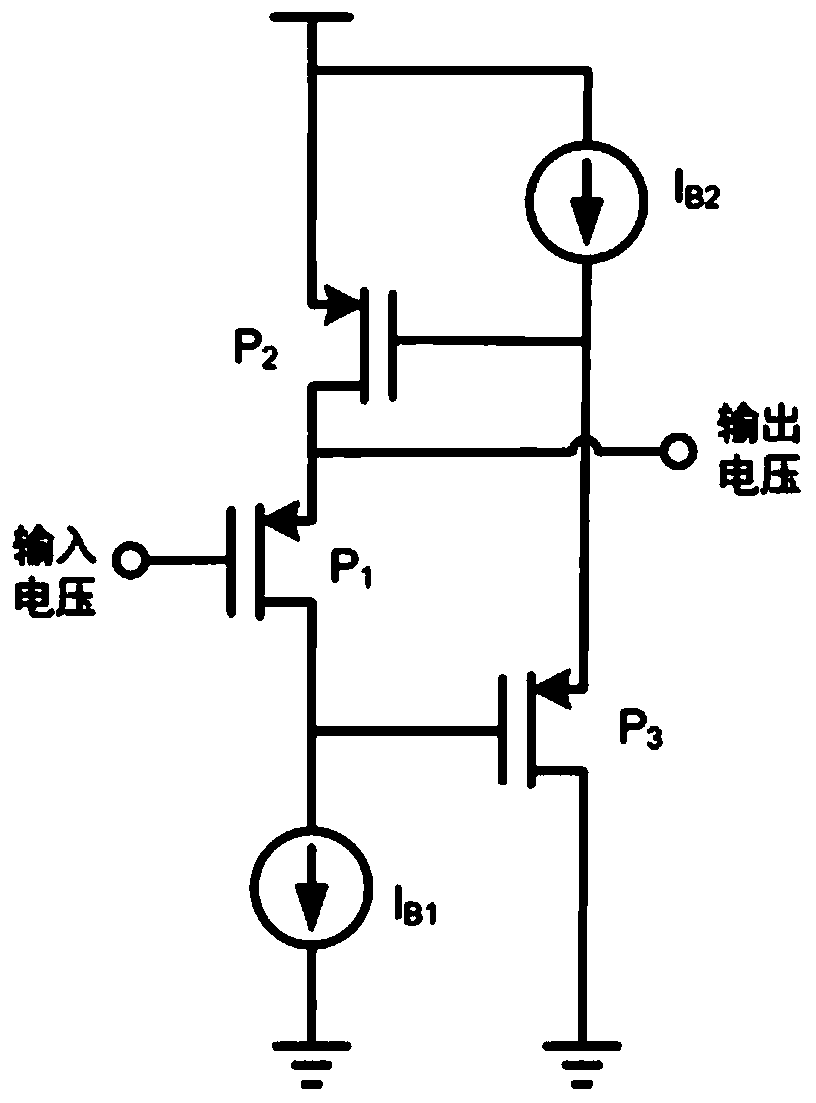

A voltage follower, high linearity technology, applied in the direction of reliability improvement modification, logic circuit connection/interface layout, logic circuit coupling/interface using field effect transistors, etc., can solve the problem of output impedance increase, super source follower The device loses the function of voltage follower, and it is difficult to expand the voltage swing, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

[0024] Example: refer to Figure 4 As shown, a high-linearity wide-swing CMOS voltage follower is characterized in that it includes a PMOS transistor P1, a PMOS transistor P2, a PMOS transistor P3, a PMOS transistor P4, a PMOS transistor P5, a PMOS transistor P6, a PMOS transistor P7, and a PMOS transistor. Tube P8, PMOS tube P9, PMOS tube P10, NMOS tube N1, NMOS tube N2, NMOS tube N3, NMOS tube N4, NMOS tube N5, reference current source Iref, resistor R1, resistor R2, capacitor C1, bias voltage Vb and A voltage source VDD; wherein one end of the reference current source Iref is respectively connected to one end of the resistor R1, the grid of the PMOS transistor P5, the grid of the PMOS transistor P6, the grid of the PMOS transistor P7, and the grid of the PMOS transistor P8; The other end of the resistor R1 is respectively connected to the gate of the PMOS transistor P1, the gate of the PMOS transistor P2, the gate of the PMOS transistor P3, the gate of the PMOS transistor P...

Embodiment example

[0025] The bias voltage Vb of the NMOS transistor N3 is designed at a lower value, so that the NMOS transistor N2 is biased at the edge of the saturation region. This implementation case is built under the 40nm CMOS process and 1.2V power supply voltage. The drain-source voltage of the NMOS transistor N2 is biased at about 150mV, which can ensure a more sufficient drain-source voltage of the input transistor (PMOS transistor P10), and at the same time, the PMOS transistor P10 is sufficient The drain-source voltage guarantees the better linearity performance of the present invention.

[0026] The working principle of the present invention is: the reference current is mirrored into two currents through the low-voltage cascode current mirror, and flows into the mirror image composed of NMOS transistor N1, NMOS transistor N2, NMOS transistor N4, and NMOS transistor N5 through PMOS transistor P6 and PMOS transistor P7. current source. The size ratio of NMOS transistor N4 and NMOS tr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More