MOSFET device and preparation method thereof

A device, p-type technology, applied in the field of MOSFET devices and their preparation, can solve problems such as small breakdown voltage, and achieve the effects of improving breakdown voltage, uniform electric field, and reducing electric field concentration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

[0107] The embodiment of the present invention also provides a method for preparing the above-mentioned MOSFET device, including:

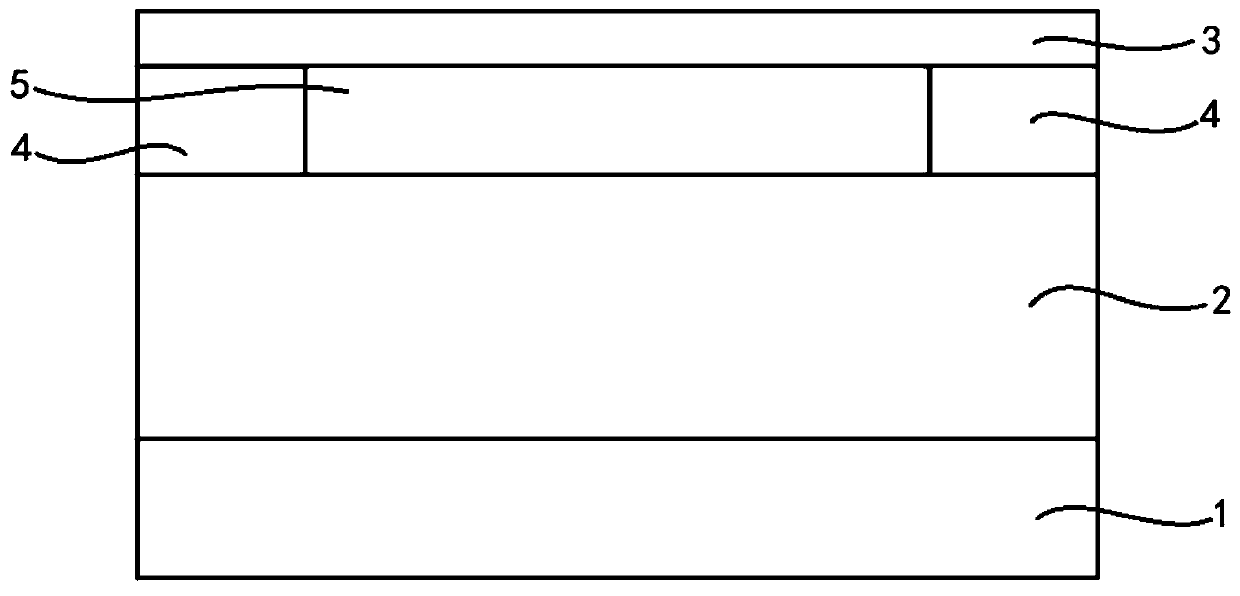

[0108] Step S1, providing a substrate 1, and sequentially forming a first n-type semiconductor layer 2, a p-type semiconductor layer and a second n-type semiconductor layer 3 on the substrate 1, the p-type semiconductor layer including a first p-type doped region 4 and the second p-type doped region 5, the first p-type doped region 4 is located on both sides of the second p-type doped region 5, and the doping concentration of the second p-type doped region 5 is higher than that of the first p-type doped region Miscellaneous area 4.

[0109] The first n-type semiconductor layer 2 and the second n-type semiconductor layer 3 are prepared by a metal organic chemical vapor deposition (MOCVD) process.

[0110] As an optional implementation, the preparation method of the p-type semiconductor layer includes:

[0111] forming a p-type semiconductor layer...

Embodiment 1

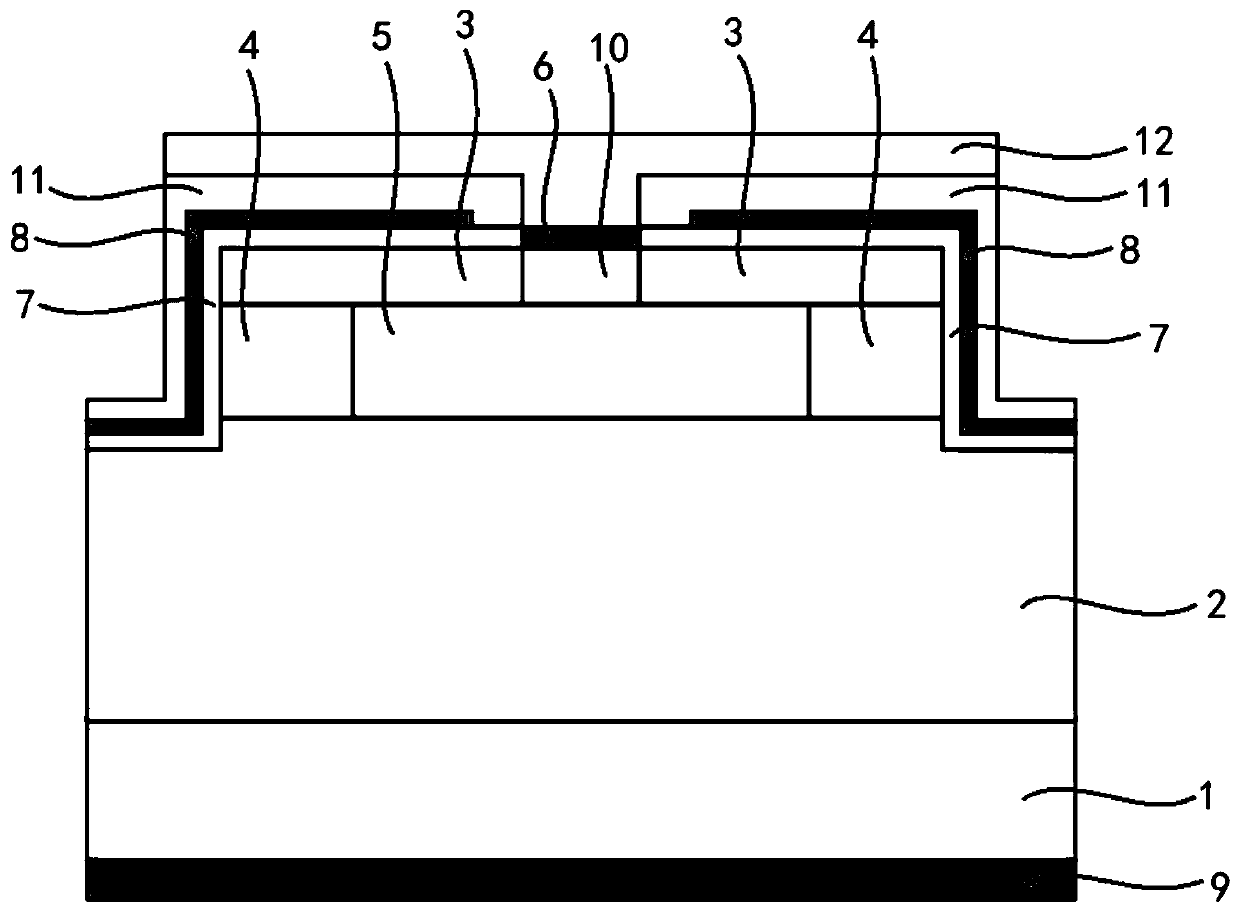

[0138] This embodiment provides a GaN-based MOSFET device, in which a drain, an n+GaN substrate, an n-GaN layer, a p-layer, and an n+GaN layer are stacked sequentially from bottom to top, wherein the p-layer consists of a p+GaN region and Composed of p-GaN regions located on the left and right sides of the p+GaN region;

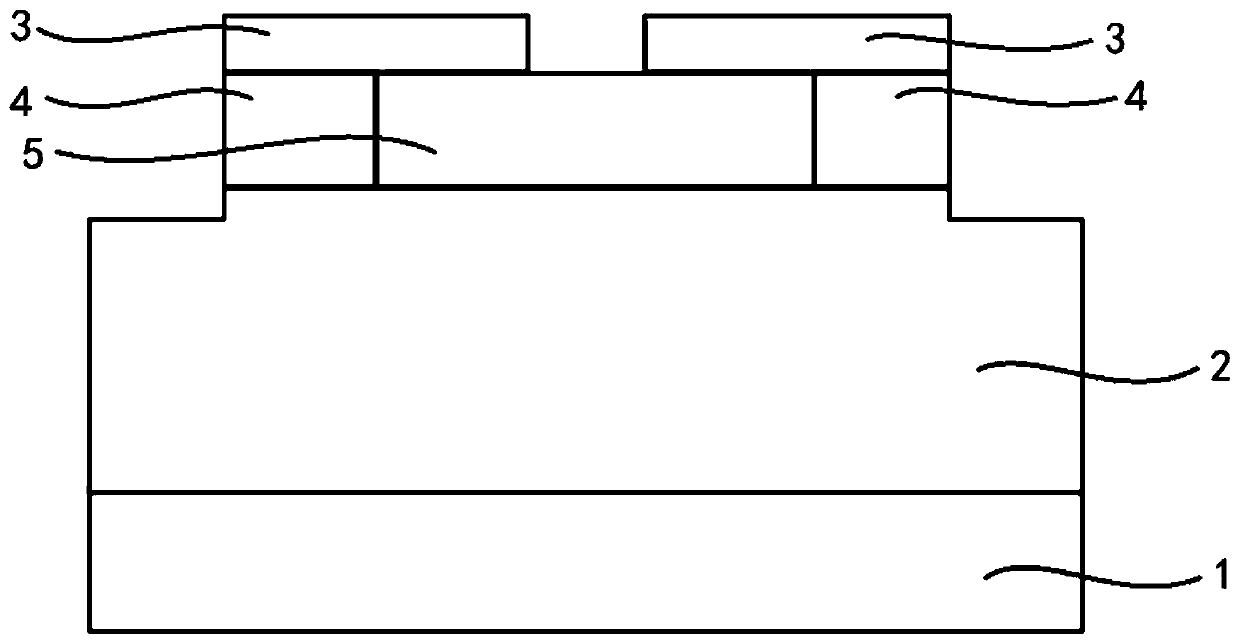

[0139] A mesa structure is formed on the edge of the n-GaN layer, p layer, and n+GaN layer. The mesa structure is composed of a bottom surface and a side surface. The bottom surface is the upper surface exposed by etching the n-GaN layer, and the side surface is the n-GaN layer. , p layer, n+GaN layer is etched and exposed side;

[0140] Pd electrodes are arranged in the n+GaN layer, and the Pd electrodes are respectively in contact with the n+GaN layer and the p+GaN region;

[0141] A source is provided on the Pd electrode; a gate insulating layer is provided on the surface of the n+GaN layer located on the left and right sides of the source and extends to ...

Embodiment 2

[0158] This embodiment provides a method for preparing a GaN-based MOSFET device in Embodiment 1, and the steps are as follows:

[0159] (1) Prepare a commercially available n+GaN substrate;

[0160](2) The n-GaN layer and the p-layer are sequentially grown on the n+GaN substrate by a metal organic chemical vapor deposition (MOCVD) process;

[0161] (3) Use an ion implanter to implant p-type dopants in the middle of the p-layer at a distance of 5 μm from the left and right ends to form a p+GaN region, and p-GaN regions are formed on both sides;

[0162] (4) growing an n+GaN layer on the p layer by metal organic chemical vapor deposition (MOCVD);

[0163] (5) Using inductively coupled plasma etching (ICP), using Cl 2 / SiCl 4 Dry etching etches a mesa structure on the left and right edges of the n-GaN layer, p layer, and n+GaN layer, and etches a groove in the middle of the n+GaN layer;

[0164] (6) A magnetron sputtering process is used to form a Pd electrode in the groove;...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Width | aaaaa | aaaaa |

| Side height | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More