Semiconductor device structure and manufacturing method thereof

A technology of device structure and manufacturing method, which is applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, and electric solid-state devices, can solve the problems of only discrete channel width changes, layout loss, and reduced circuit integration, and achieve improved The effect of device integration and device performance, reducing interface traps and improving reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

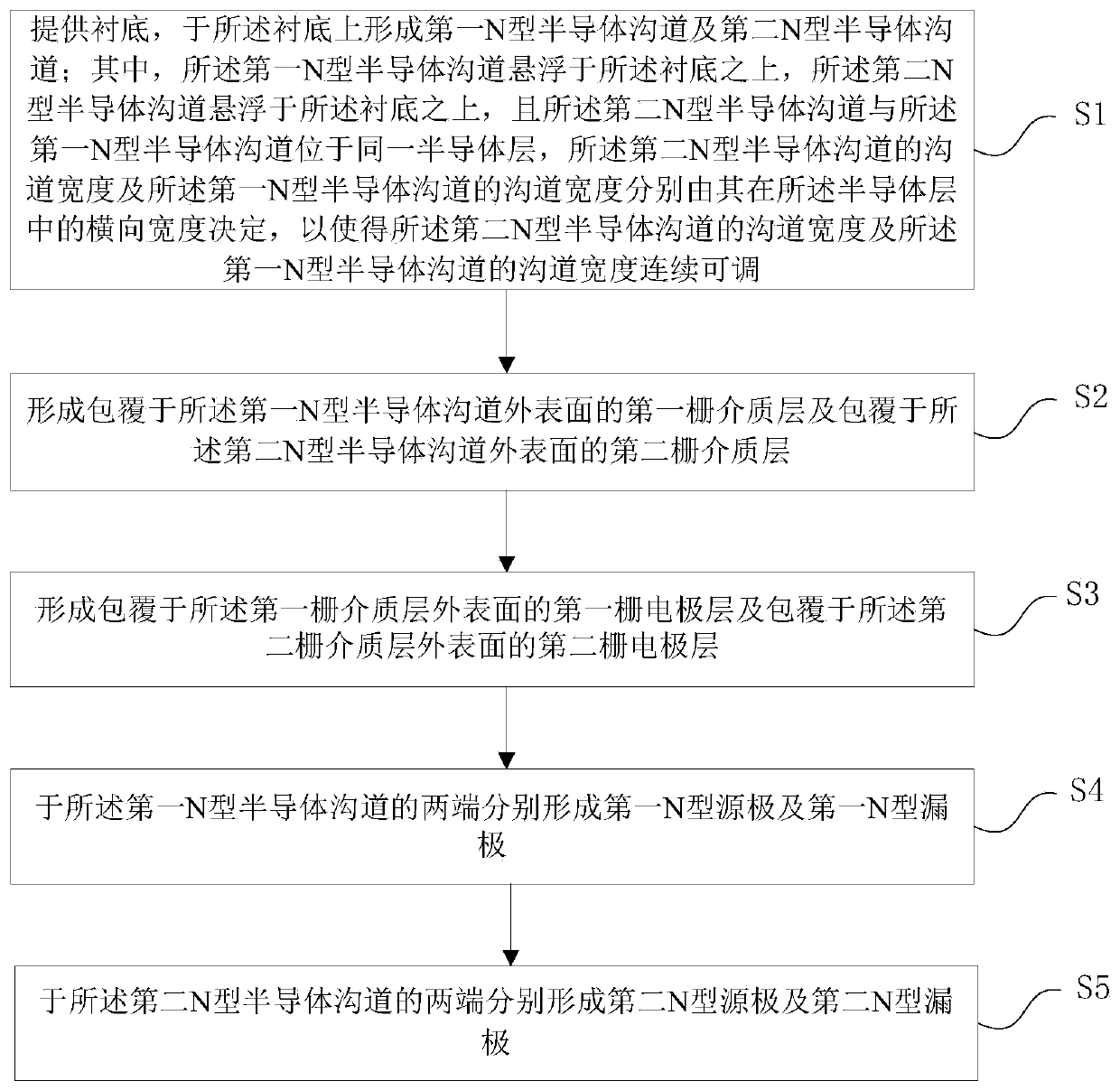

[0083] see figure 1 , the invention provides a method for manufacturing a semiconductor device structure, the method for manufacturing a semiconductor device structure includes the steps of:

[0084] 1) Provide a substrate, and form a first N-type semiconductor channel and a second N-type semiconductor channel on the substrate; wherein, the first N-type semiconductor channel is suspended above the substrate, and the The second N-type semiconductor channel is suspended above the substrate, and the second N-type semiconductor channel is located in the same semiconductor layer as the first N-type semiconductor channel, and the second N-type semiconductor channel The channel width of the channel and the channel width of the first N-type semiconductor channel are respectively determined by its lateral width in the semiconductor layer, so that the channel width of the second N-type semiconductor channel and the The channel width of the first N-type semiconductor channel is continuo...

Embodiment 2

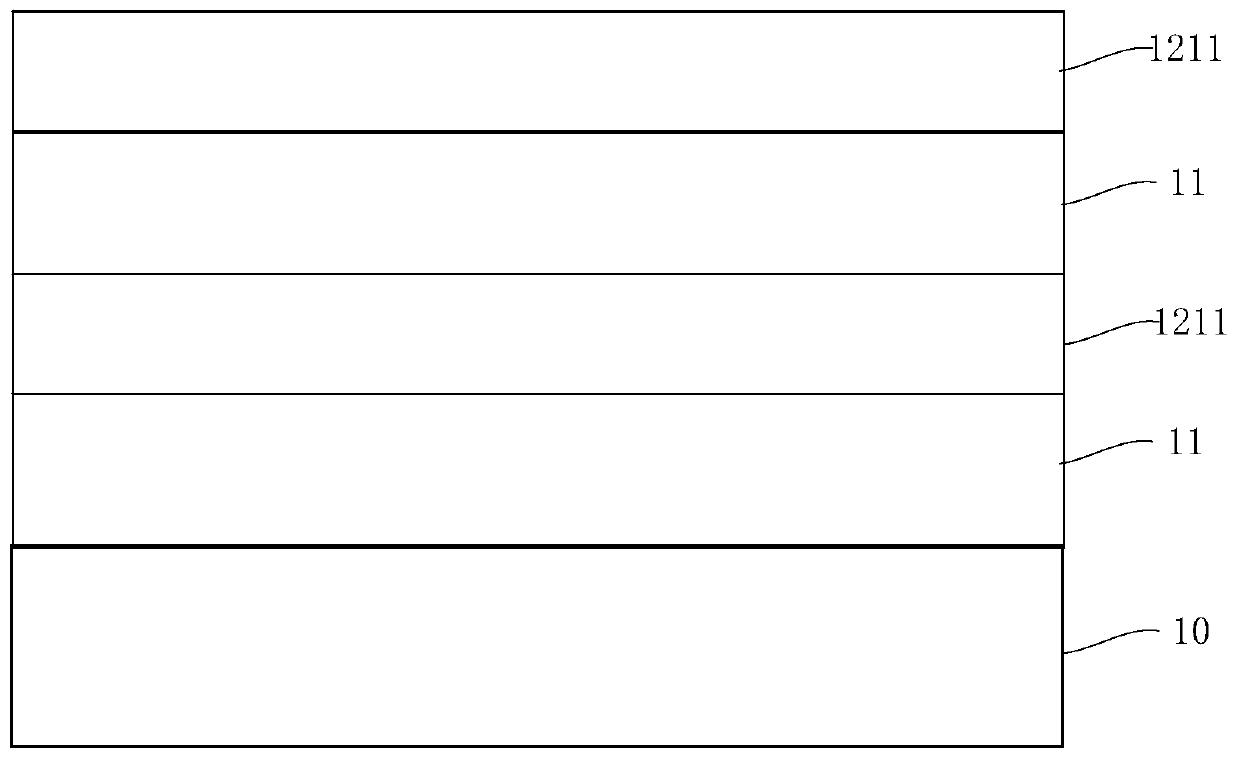

[0127] Please combine Figure 2 to Figure 11 read on Figure 12 , the present invention also provides a semiconductor device structure, the semiconductor device structure includes: a substrate 10; a first N-type semiconductor channel 121, the first semiconductor channel 121 is suspended above the substrate 10; Two N-type semiconductor channels 131, the second N-type semiconductor channel 131 is suspended above the substrate 10, the second N-type semiconductor channel 131 and the first N-type semiconductor channel 121 are located In the same semiconductor layer, the channel width of the second N-type semiconductor channel 131 and the channel width of the first N-type semiconductor channel 121 are respectively determined by their lateral widths in the semiconductor layer, so that the The channel width of the second N-type semiconductor channel 131 and the channel width of the first N-type semiconductor channel 121 are continuously adjustable; the first gate dielectric layer 122...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More