Chip packaging preprocessing method and chip analysis method

A multi-chip packaging and pretreatment technology, applied in chemical instruments and methods, electrical components, semiconductor/solid-state device manufacturing, etc., can solve problems such as difficulty in removing the bare die to be removed, and overcome FIB pretreatment problems and costs. Inexpensive, easy-to-use effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0067] An embodiment of the present invention provides a preprocessing method for multi-chip packaging, and the preprocessing method may include:

[0068] Detect the surface projection area of different die on the multi-chip package;

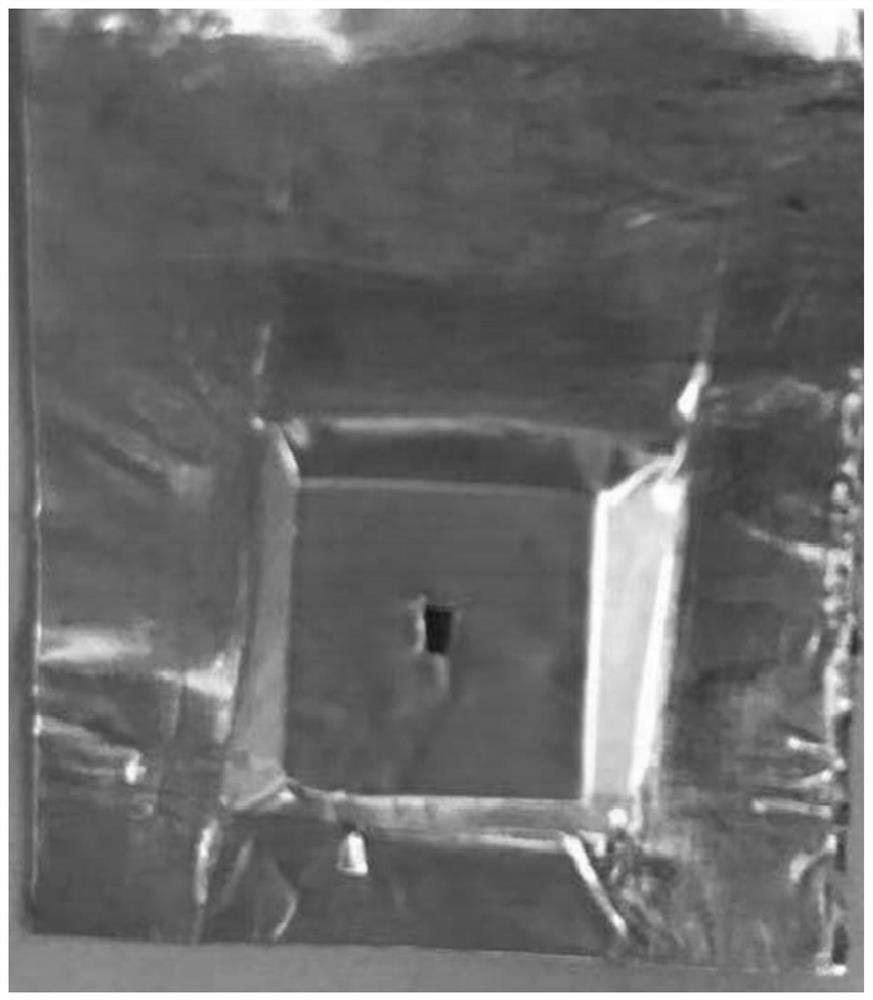

[0069] Protection of multi-chip packages outside the projected area of the surface from which the die is to be removed;

[0070] etching the multi-chip package;

[0071] peeling off the die to be removed to obtain a bare target die.

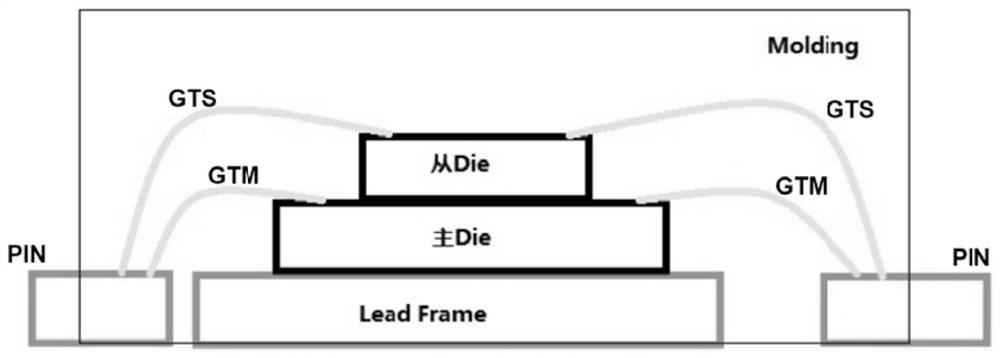

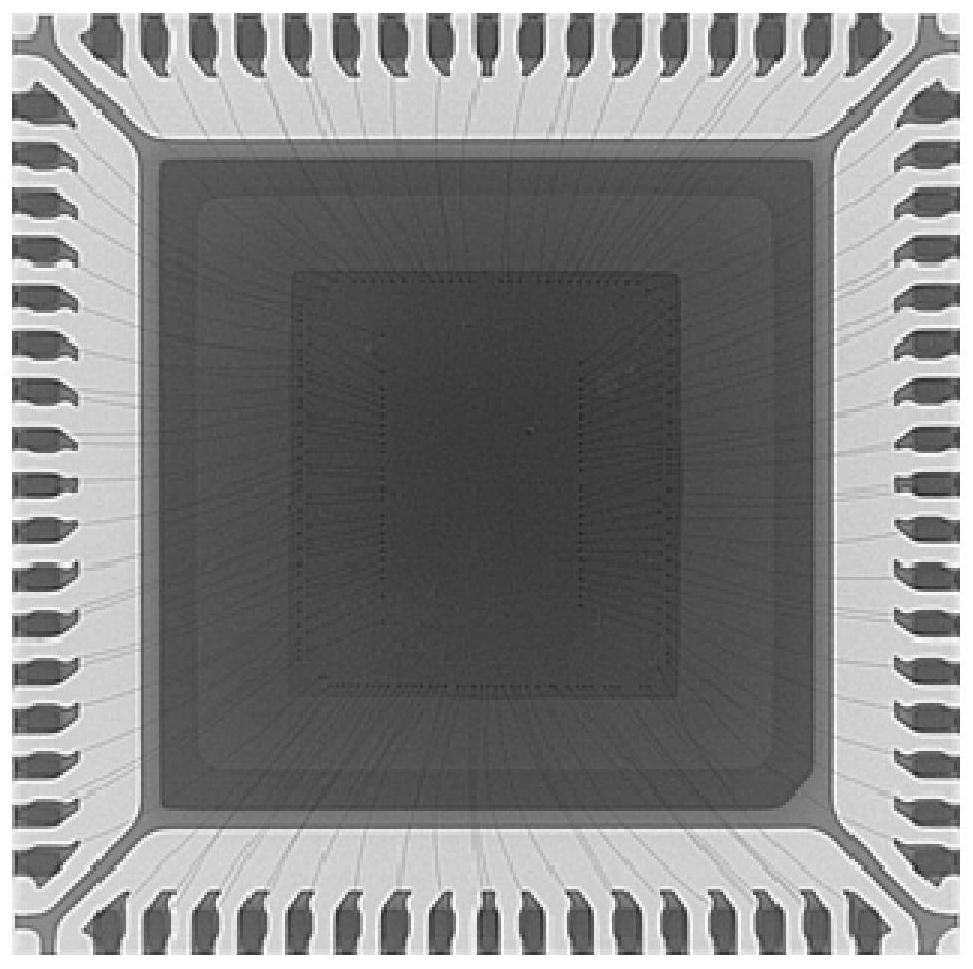

[0072] Such as figure 1 , the chips to be preprocessed are stacked and packaged, called multi-chip packaging, from Die is the bare die to be removed, the main Die is the target bare die, LeadFrame is the lead frame, Molding is molding, and molding is usually resin Constituted, GTS is the gold wire of the slave Die, GTM is the gold wire of the main Die, PIN is the outer pin of the package, and the surface projection area can be projected onto the molded outer surface of the chip with the surface of the lead f...

Embodiment 2

[0100] Based on Embodiment 1, the embodiment of the present invention provides a chip analysis method, which includes:

[0101] Perform the preprocessing method described in Embodiment 1 on the chip;

[0102] Focused ion beam analysis was performed on the preconditioned chip.

[0103] Further, exemplarily, performing focused ion beam (FIB) analysis on the pre-processed chip may include:

[0104] Using a FIB device to generate a focused ion beam to irradiate the main Die of the pretreated chip or a Die sample extracted from the pretreated chip, wherein the Die sample or the main Die responds to a charge pulse corresponding to the ion beam;

[0105] The charge pulse is received by a spectrum amplifier, and the output wave of the spectrum amplifier corresponding to the charge pulse is received by a multi-channel analyzer, thereby realizing failure analysis of the main Die or the Die sample.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More