Robot chassis control system and method based on time hard synchronization

A control system and robot technology, applied in the direction of program control manipulators, instruments, manipulators, etc., can solve the problems of untimely response to requests, uncertain delays, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

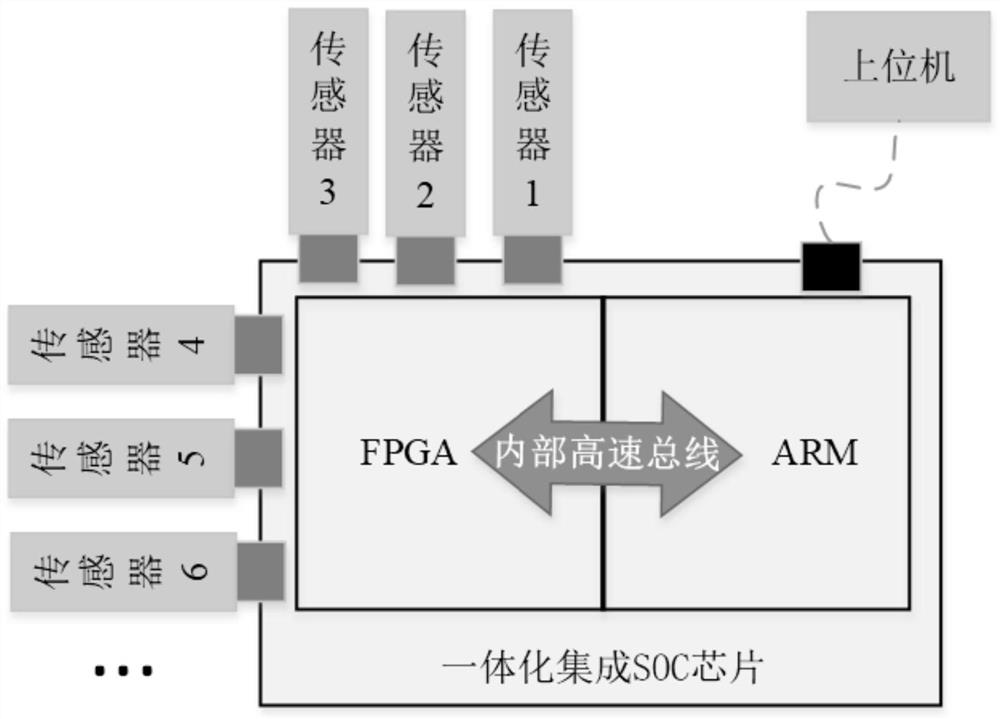

[0027] Please refer to figure 1 , which is a structural diagram of a robot chassis control system based on time-hard synchronization disclosed in the present invention. A robot chassis control system based on time-hard synchronization disclosed in the present invention includes an integrated SOC chip, in which the SOC chip Embedded with an ARM processor and FPGA device, the FPGA device is a semi-custom circuit in an application-specific integrated circuit, and is a programmable logic array, which can effectively solve the problem that the number of gate circuits of the original device is small .

[0028] The robot chassis control system also includes a host computer electrically connected to the ARM processor through the RS232 serial port;

[0029] When multiple sensors are used to monitor the control parameters of the robot chassis (refer to figure 1 The sensor 1, sensor 2...) in the sensor are mounted to the FPGA, and based on the parallel processing characteristics of the...

Embodiment 2

[0046] When there is no relevant serial port in the FPGA that can be mounted to the sensor, for example, there is no 485 serial port in the FPGA, but the 485 bus serial port is currently the most widely used and most common bus form in the industry. When it is necessary to connect external sensors through the 485 serial port, it can be considered to simulate the 485 communication protocol through software inside the FPGA, and then add a 485 level conversion chip to convert the 1.8VTTL level of the FPGA to the level required by the 485 serial port, thereby realizing The FPGA communicates with external sensors through the 485 serial port.

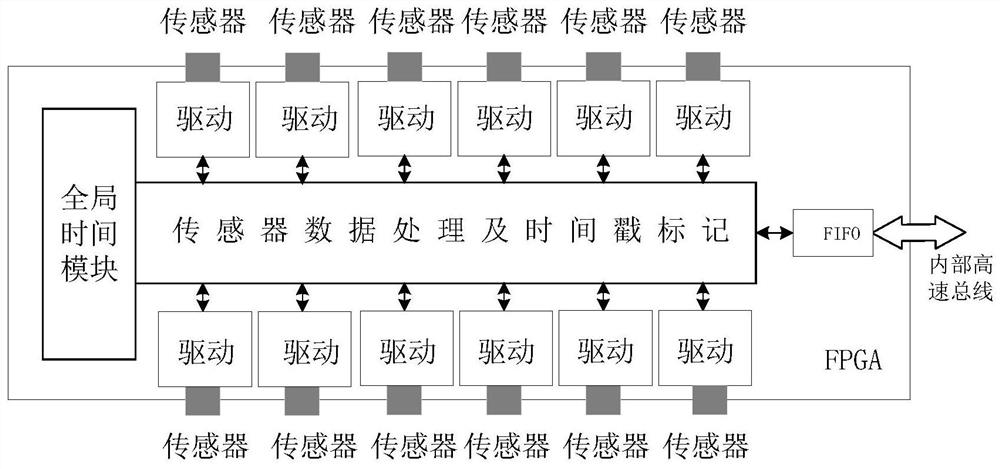

[0047] specific reference Figure 4 , which is an implementation diagram of the FPGA mounted to the sensor. In this embodiment, it is considered that a processor and a memory are respectively set in the sensor drive processing module, wherein the execution program of the simulated 485 communication protocol written can be stored in the In th...

Embodiment 3

[0050] In order to ensure that the data reported by the ARM processor is not lost or leaked, under this embodiment, a buffer module is provided on the FPGA, and the buffer module can use a FIFO buffer, which is a buffer link of the system. If there is no FIFO buffer It is impossible for the whole system to work normally without the controller. It mainly has several functions:

[0051] 1) Cache the continuous data stream to prevent data loss during machine loading and storage operations;

[0052] 2) The data is collected and stored in the machine, which can avoid frequent bus operations and reduce the burden on the CPU;

[0053] 3) Allow the system to perform DMA operations to improve data transmission speed. This is a very important point. If the DMA operation is not used, the data transmission will not meet the transmission requirements, and the burden on the CPU will be greatly increased, and the data storage work cannot be completed at the same time.

[0054] Therefore, s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More