Patents

Literature

31results about How to "Low latency processing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

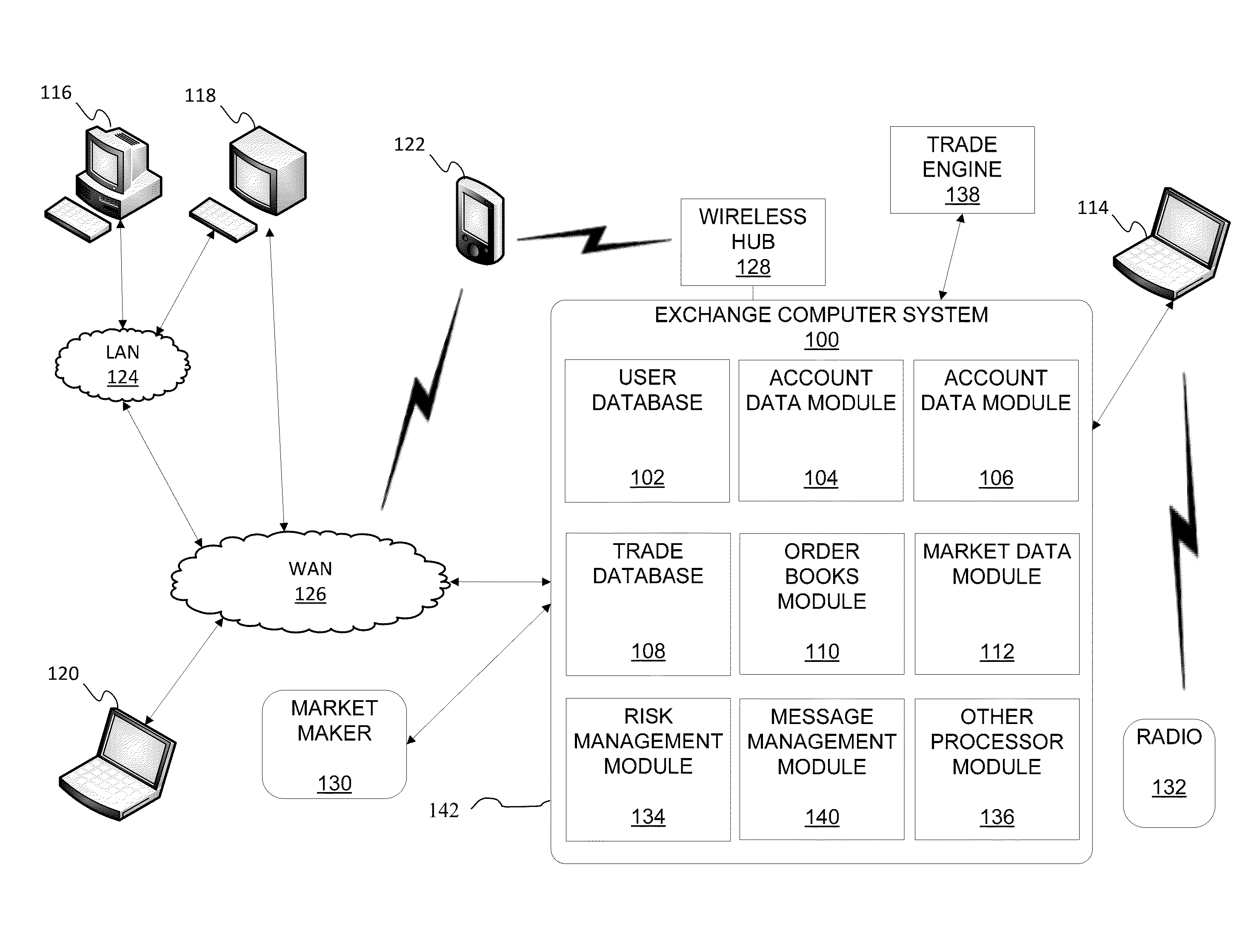

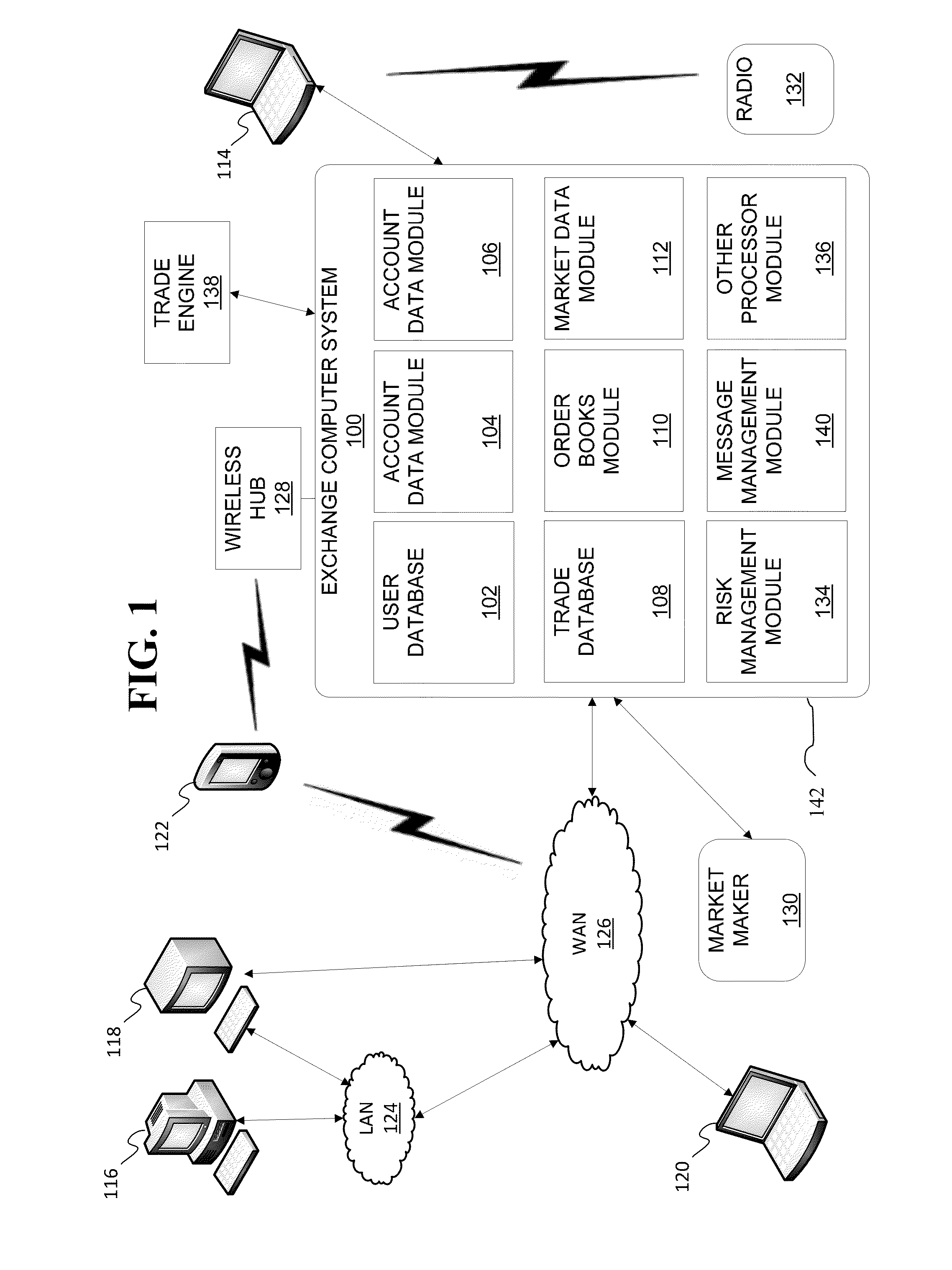

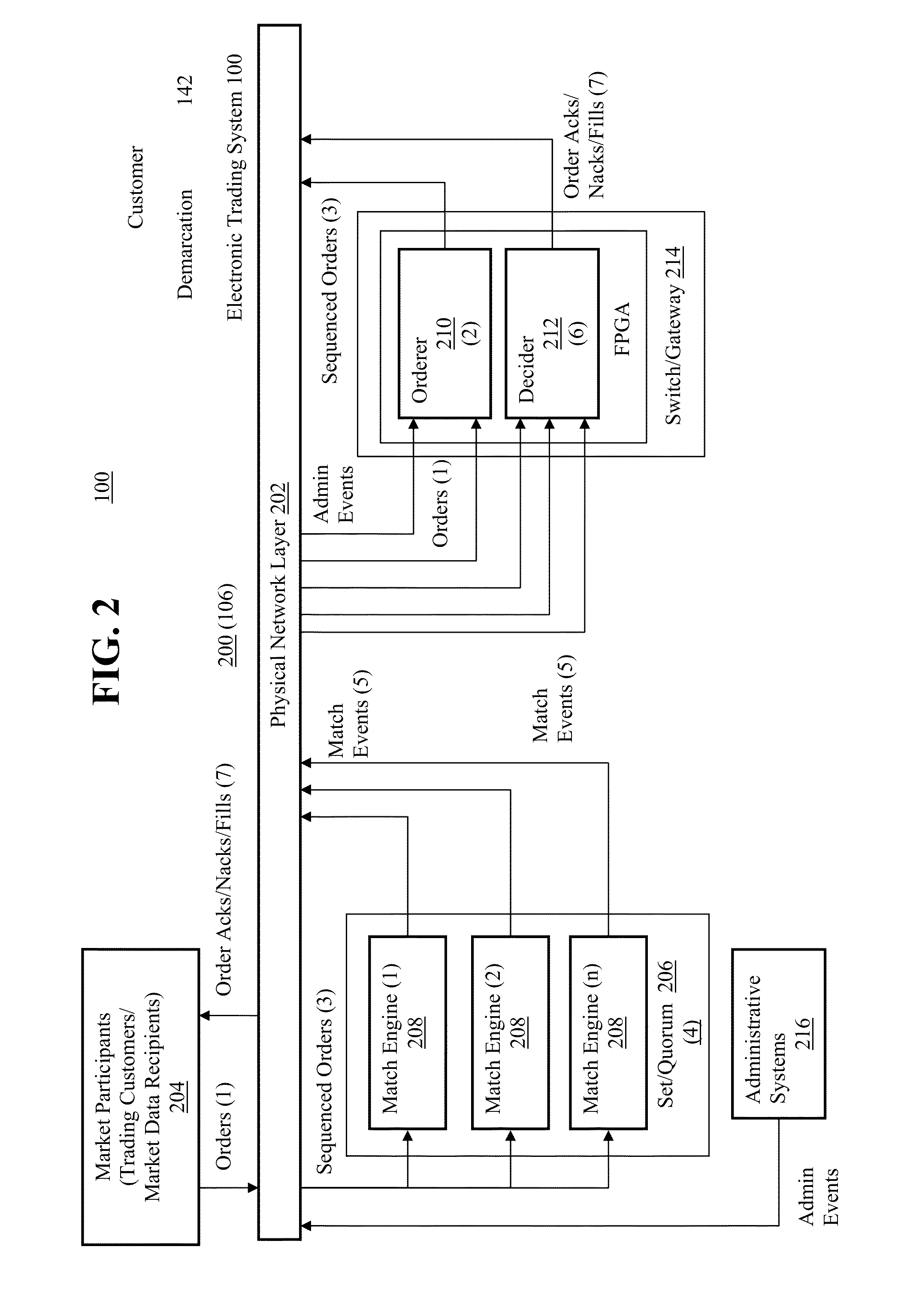

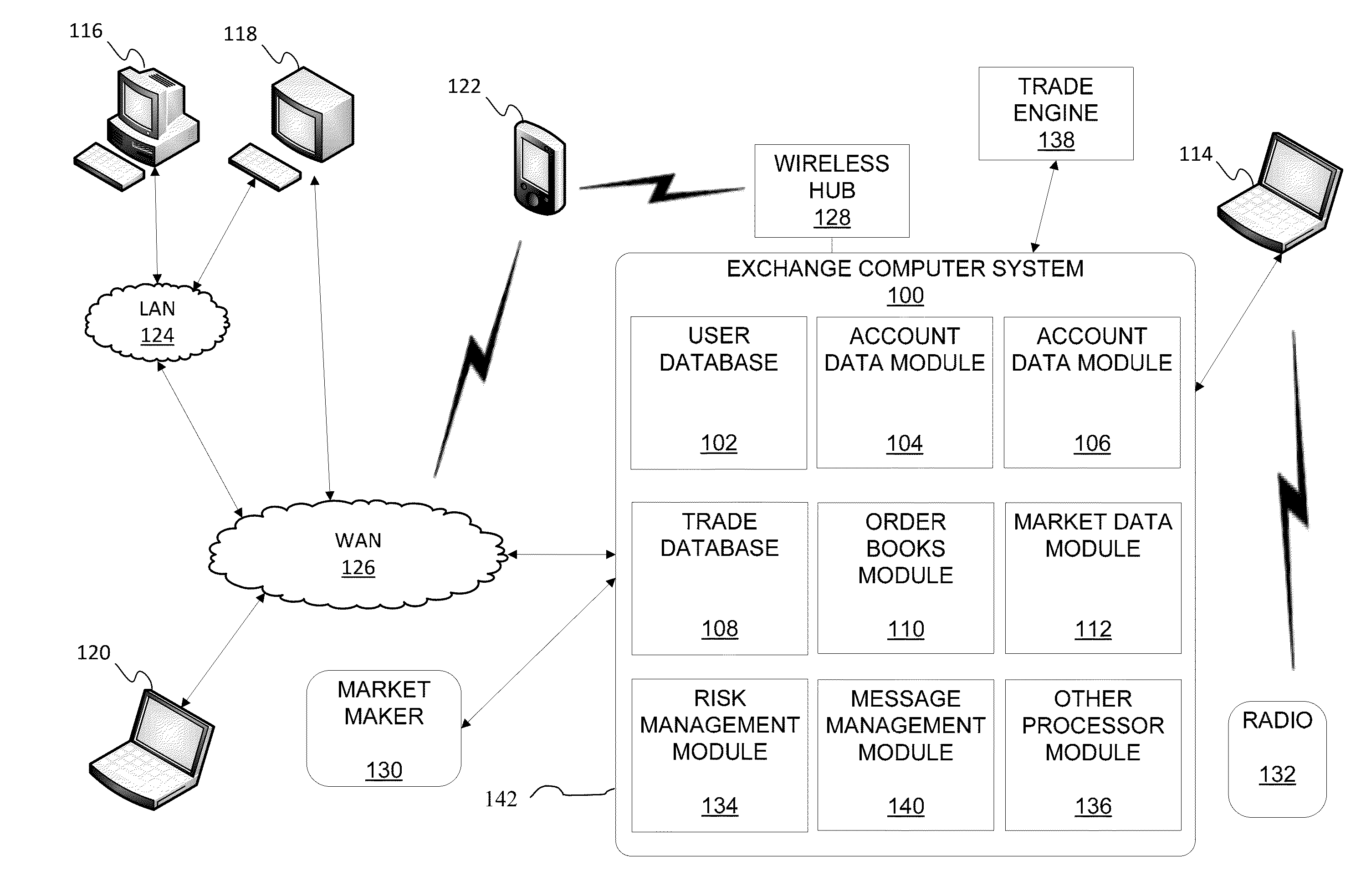

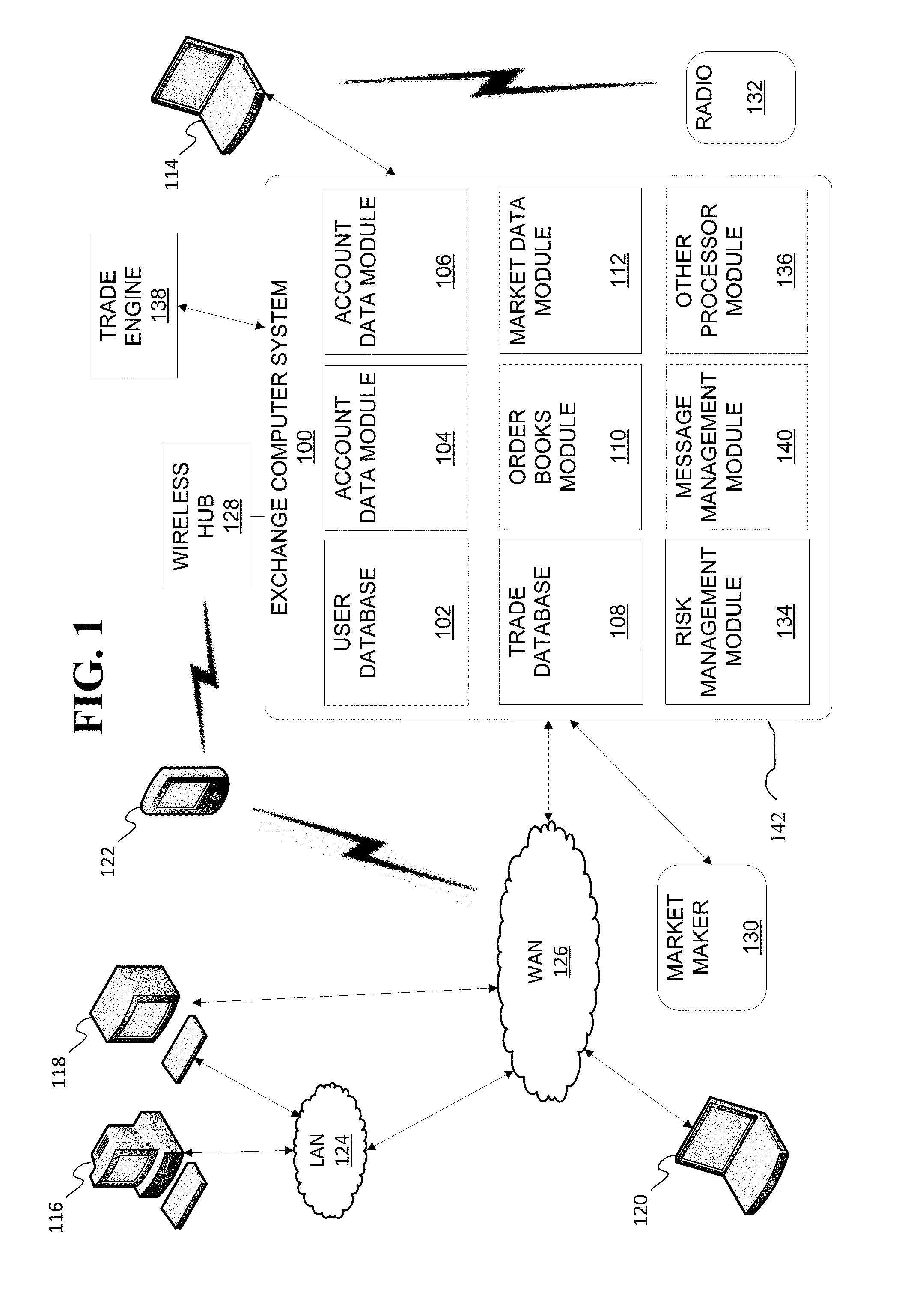

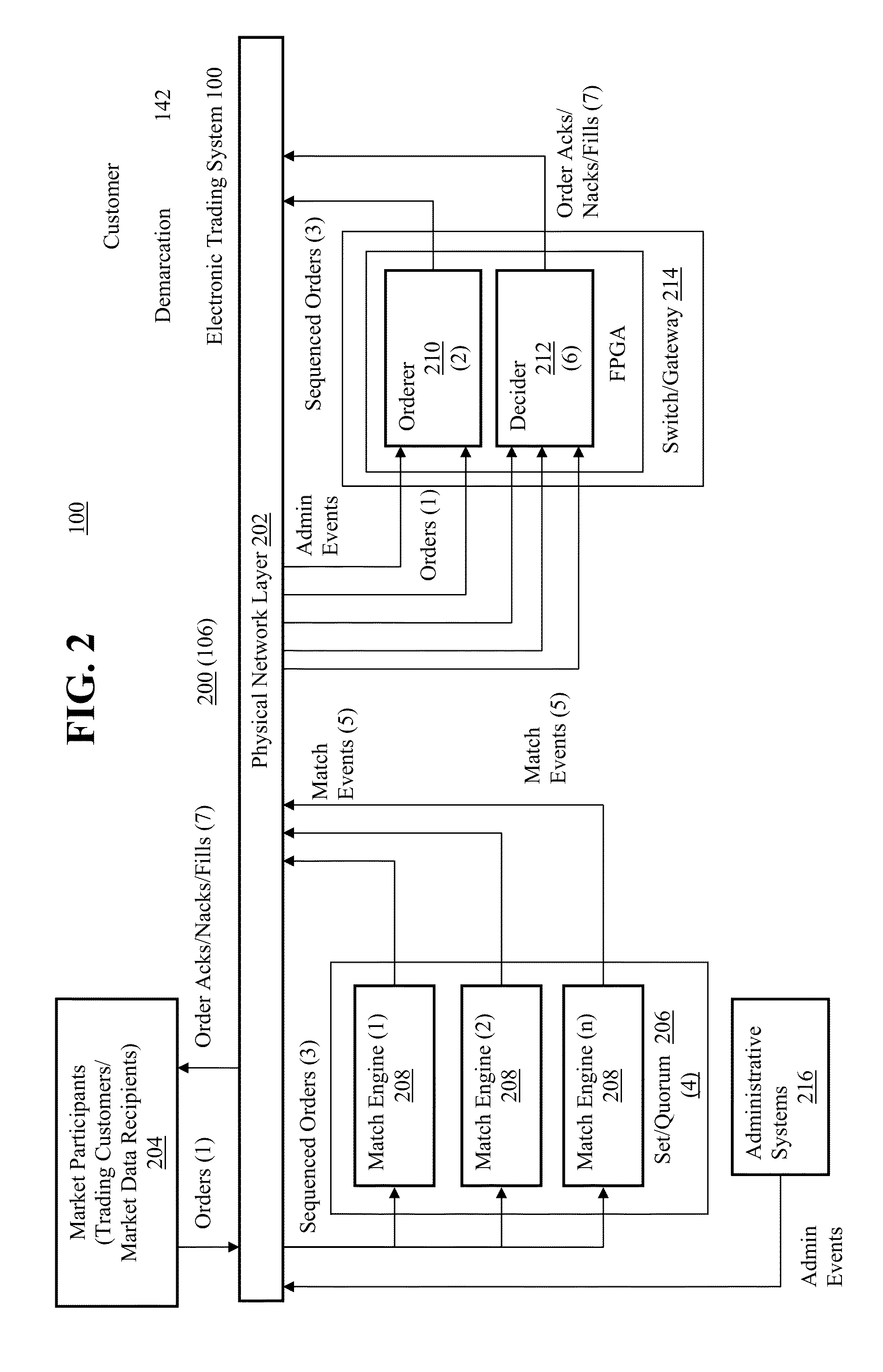

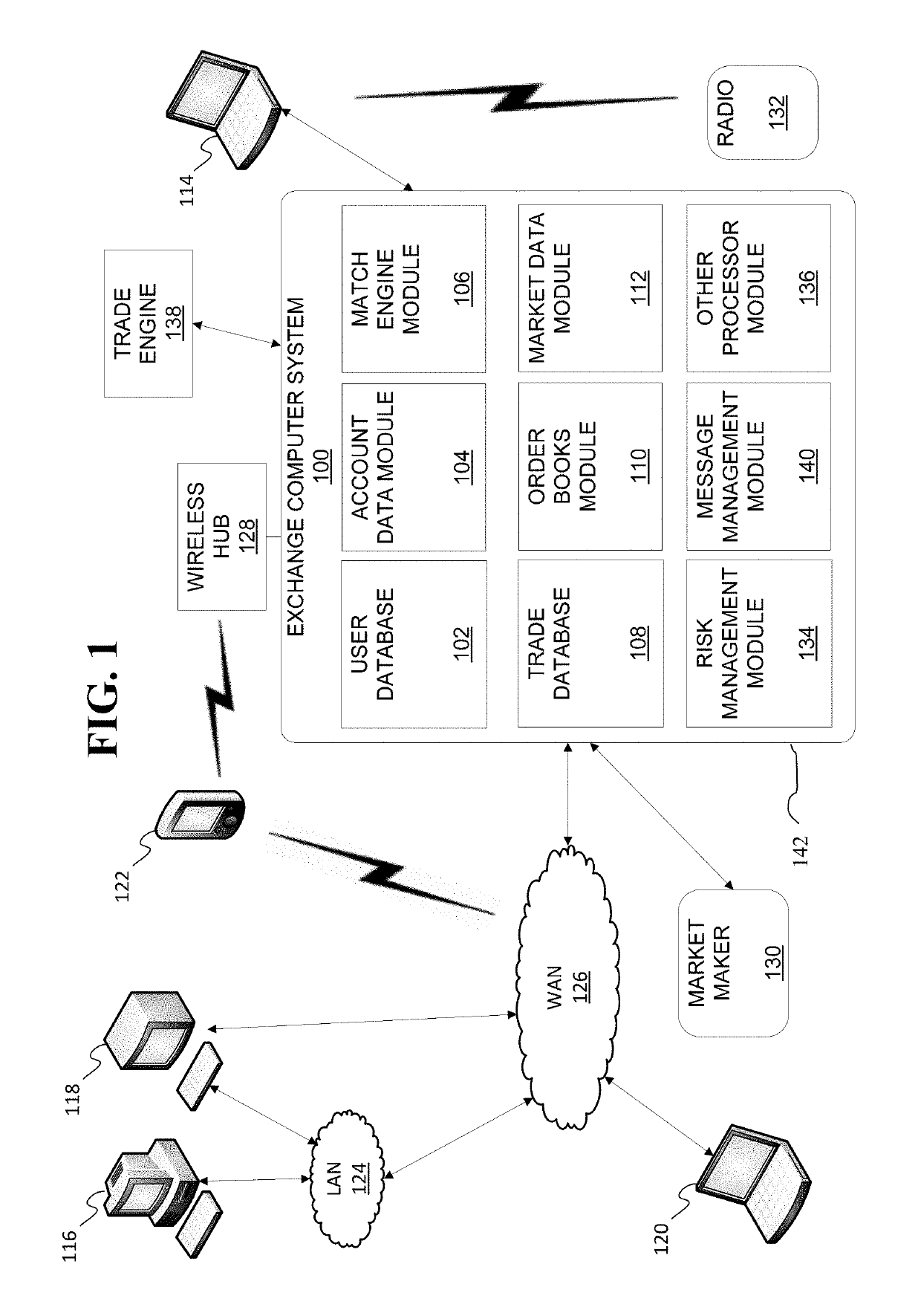

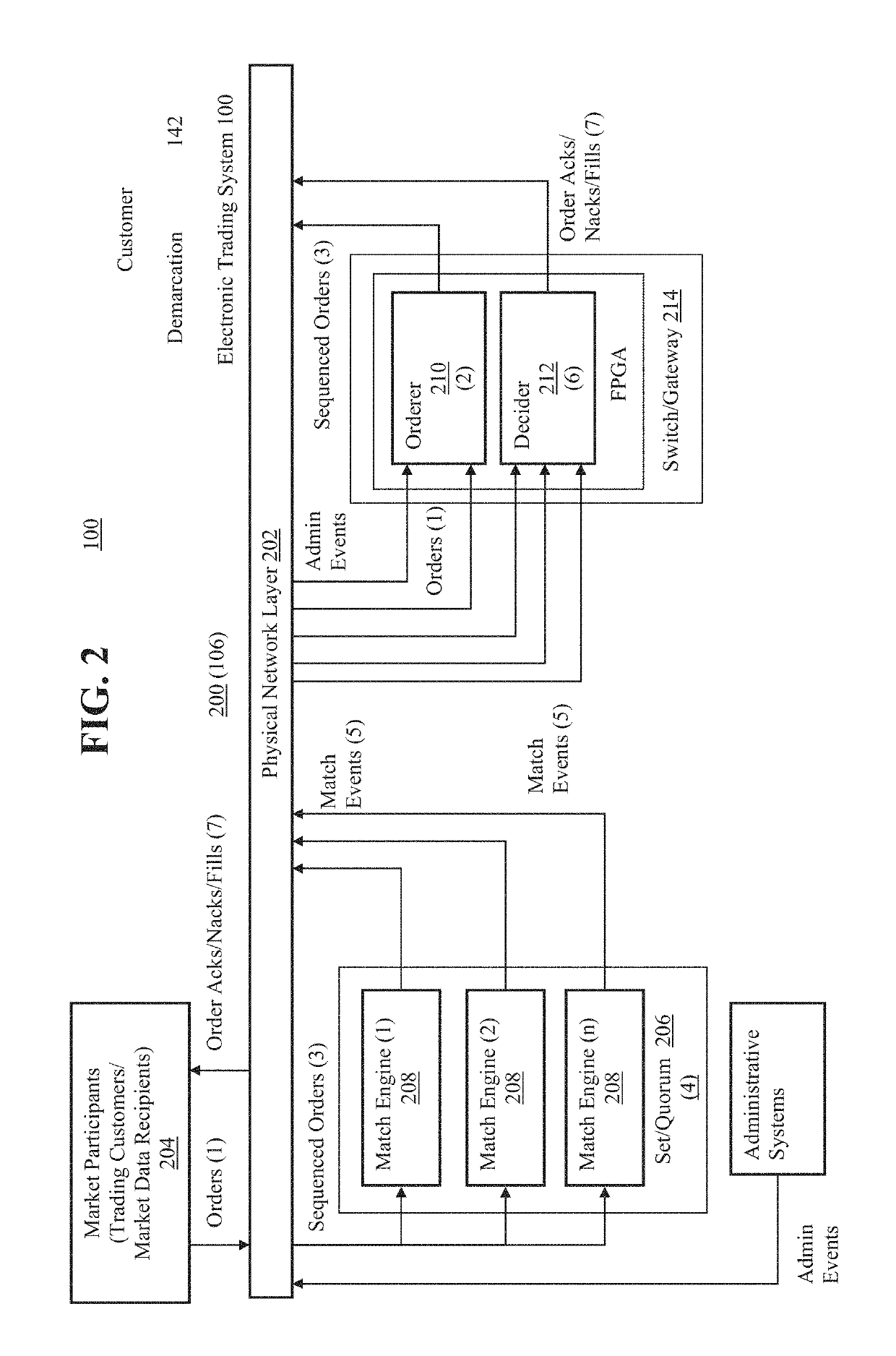

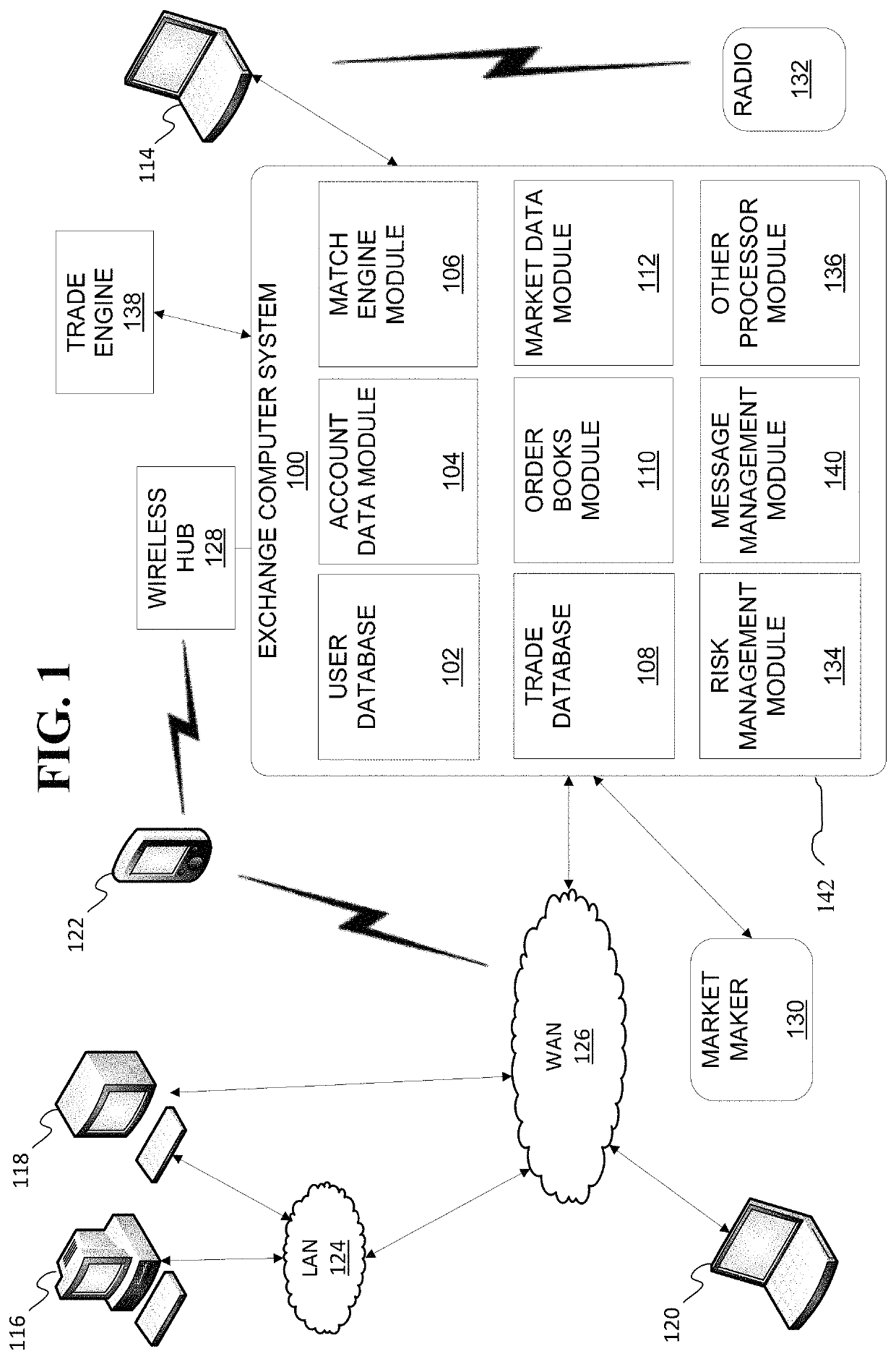

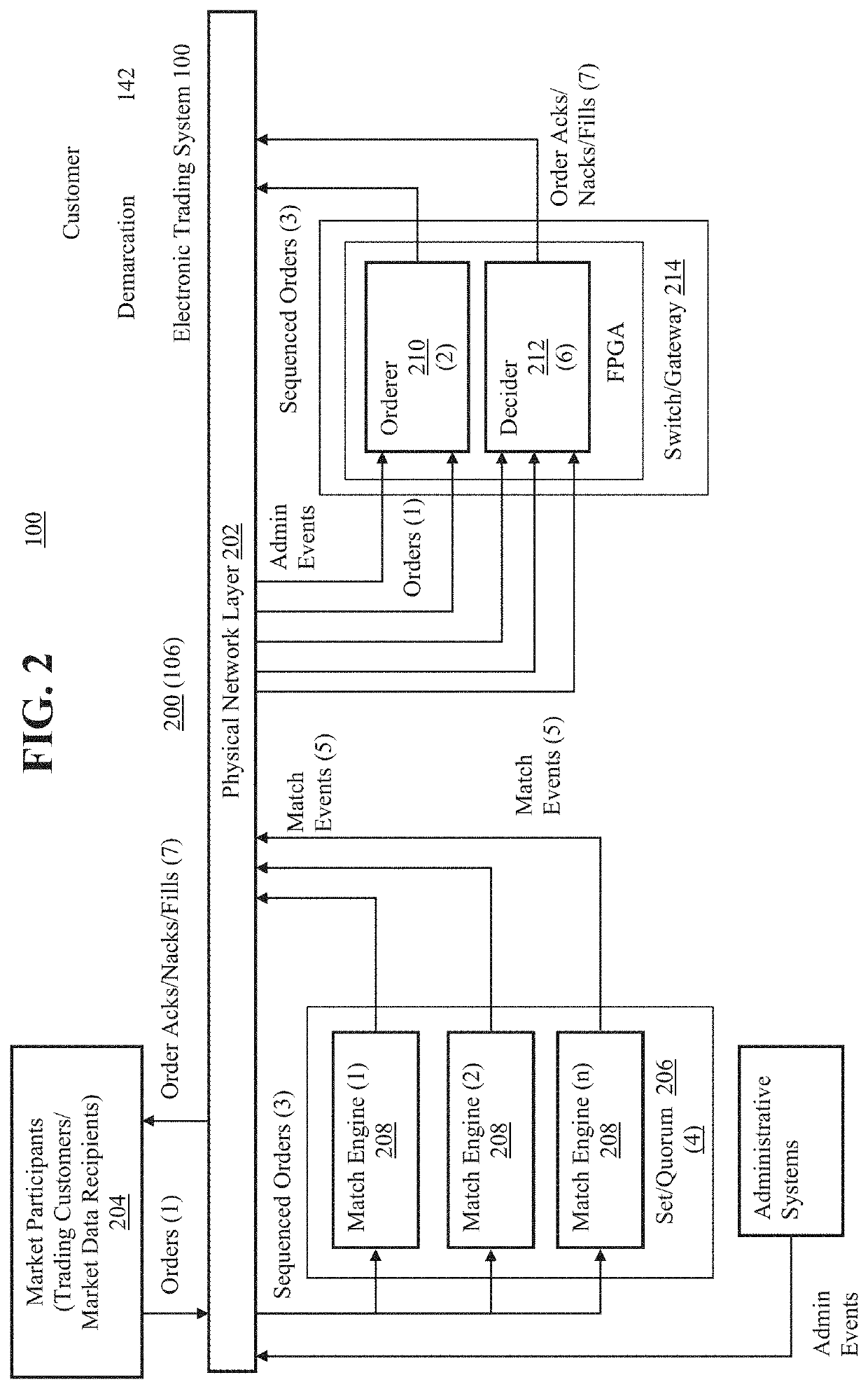

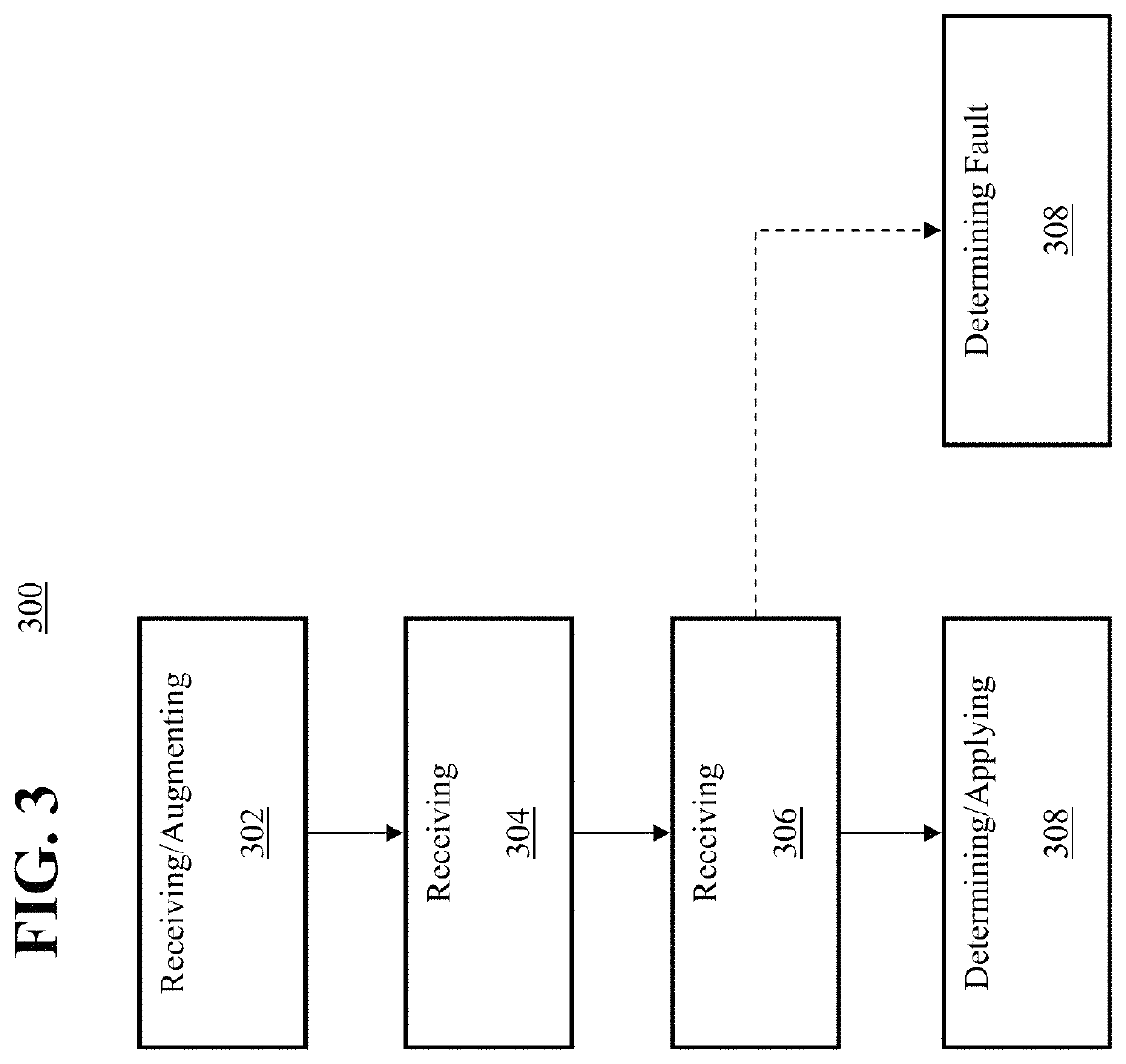

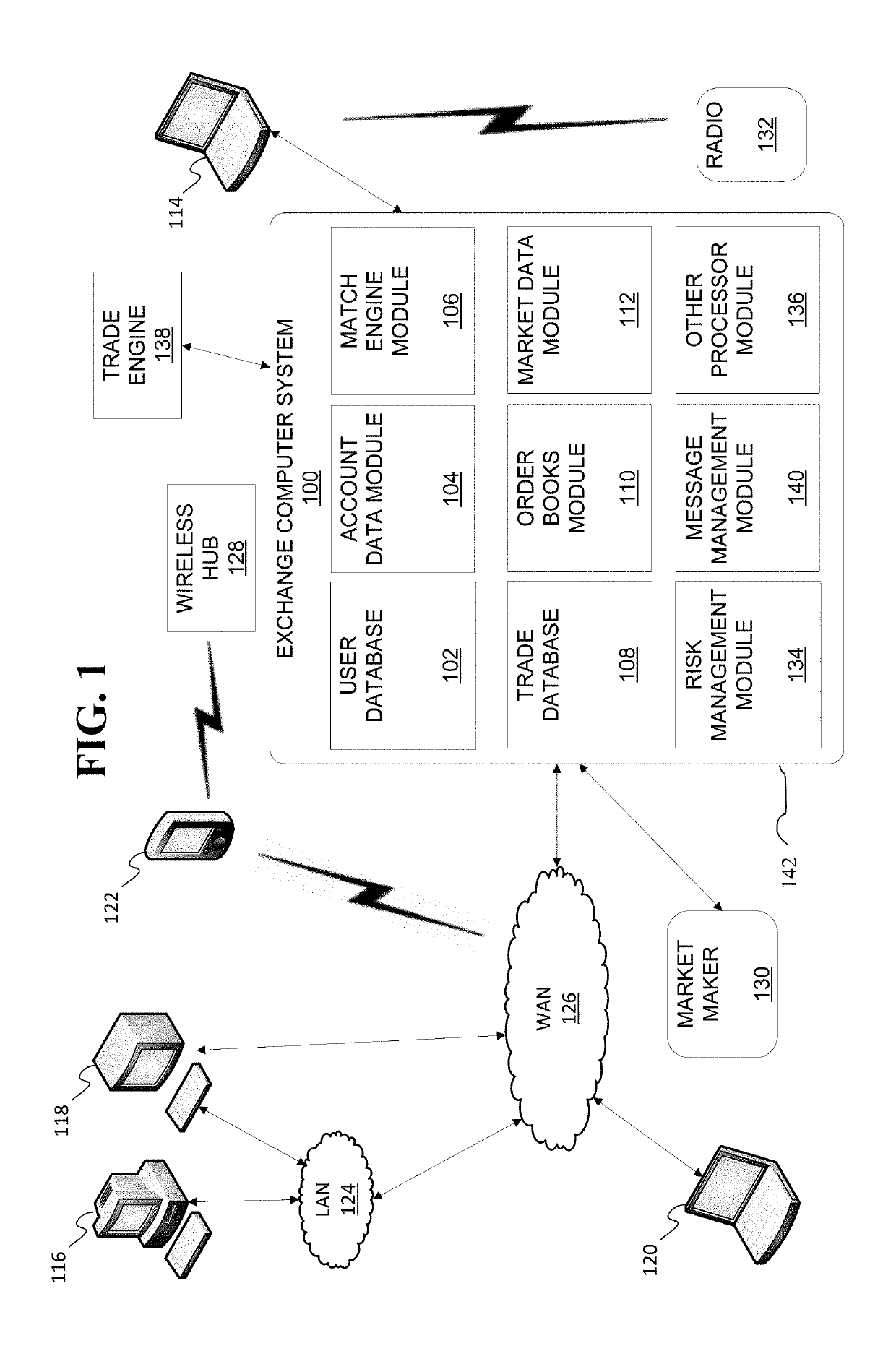

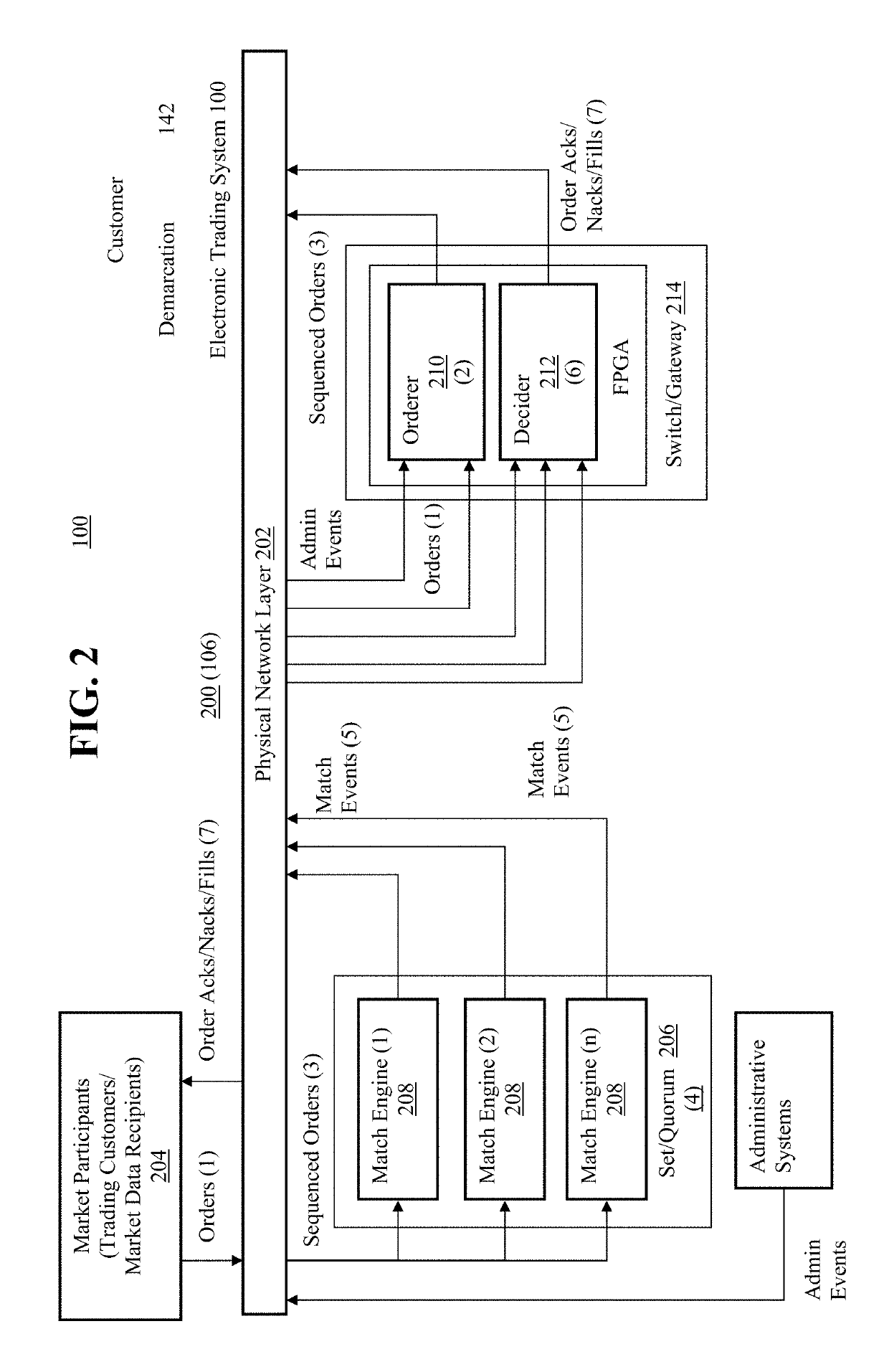

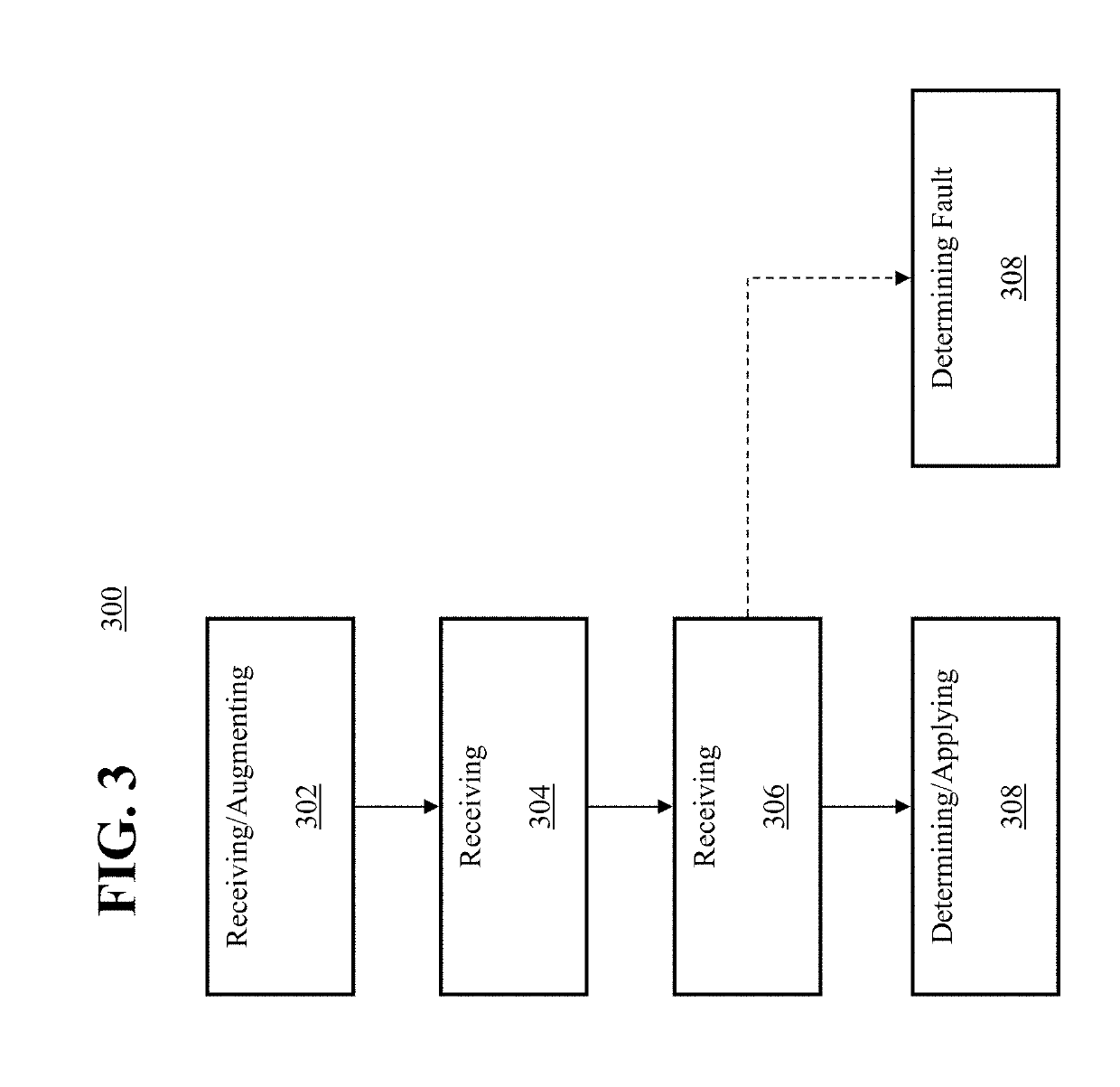

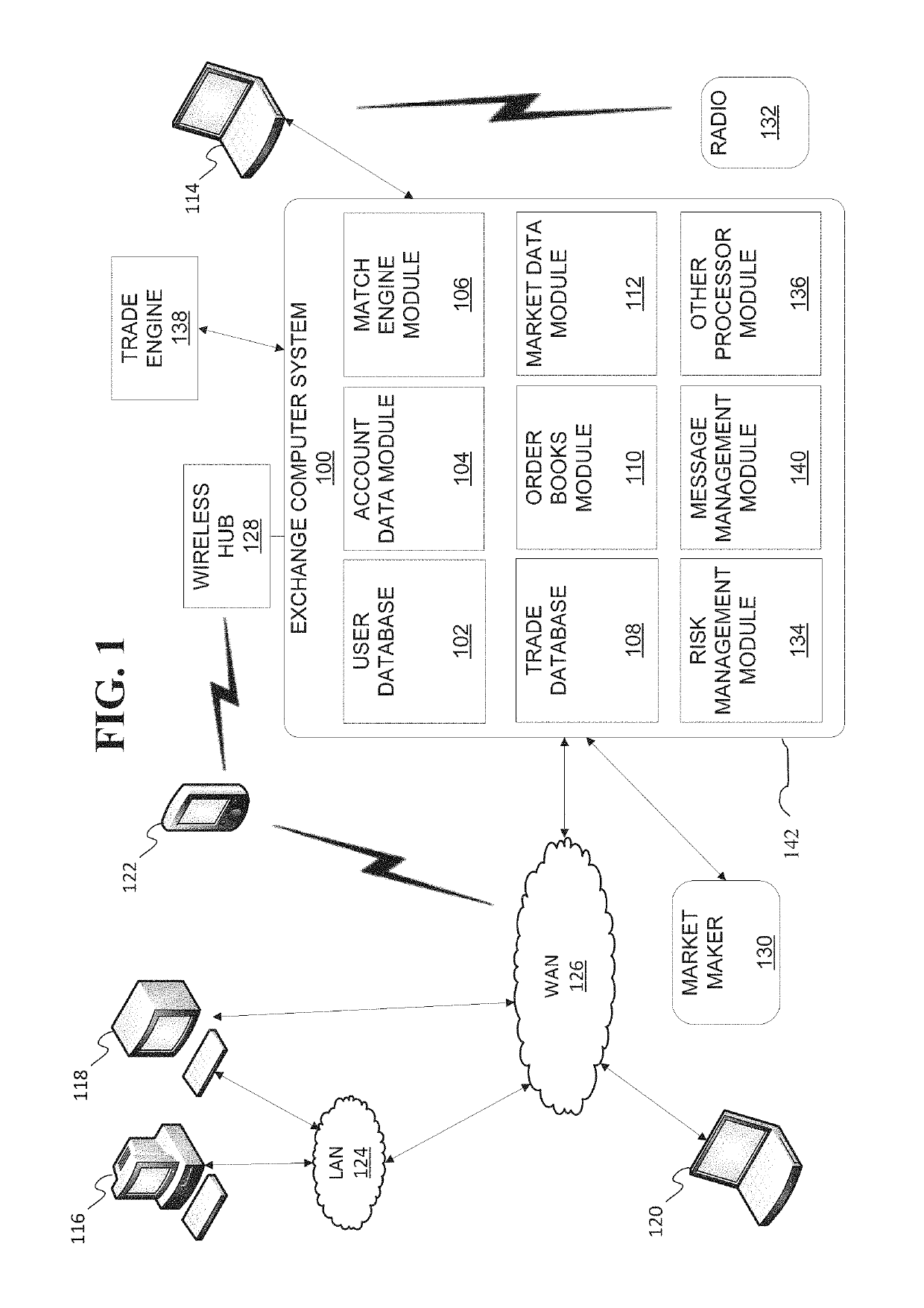

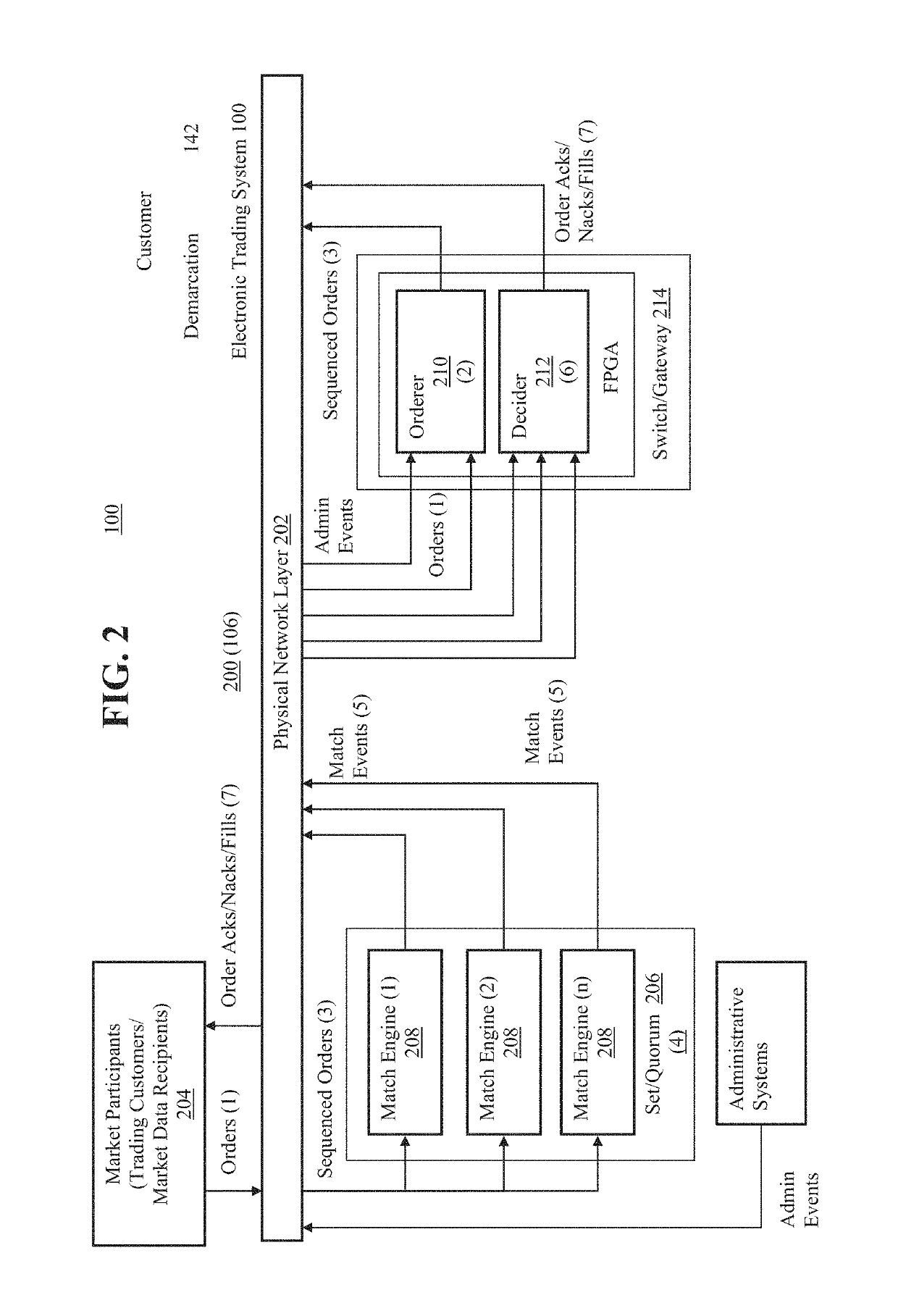

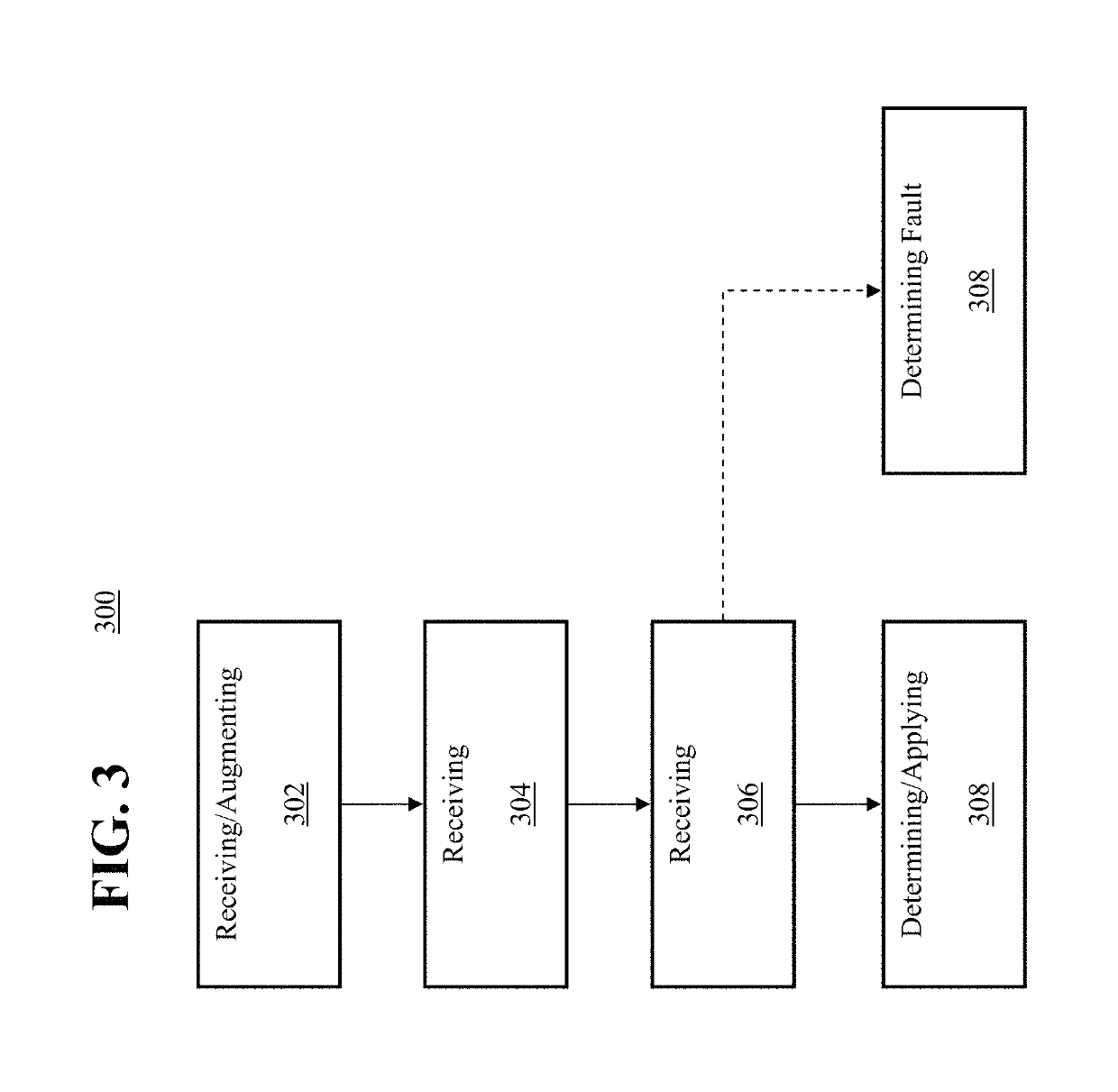

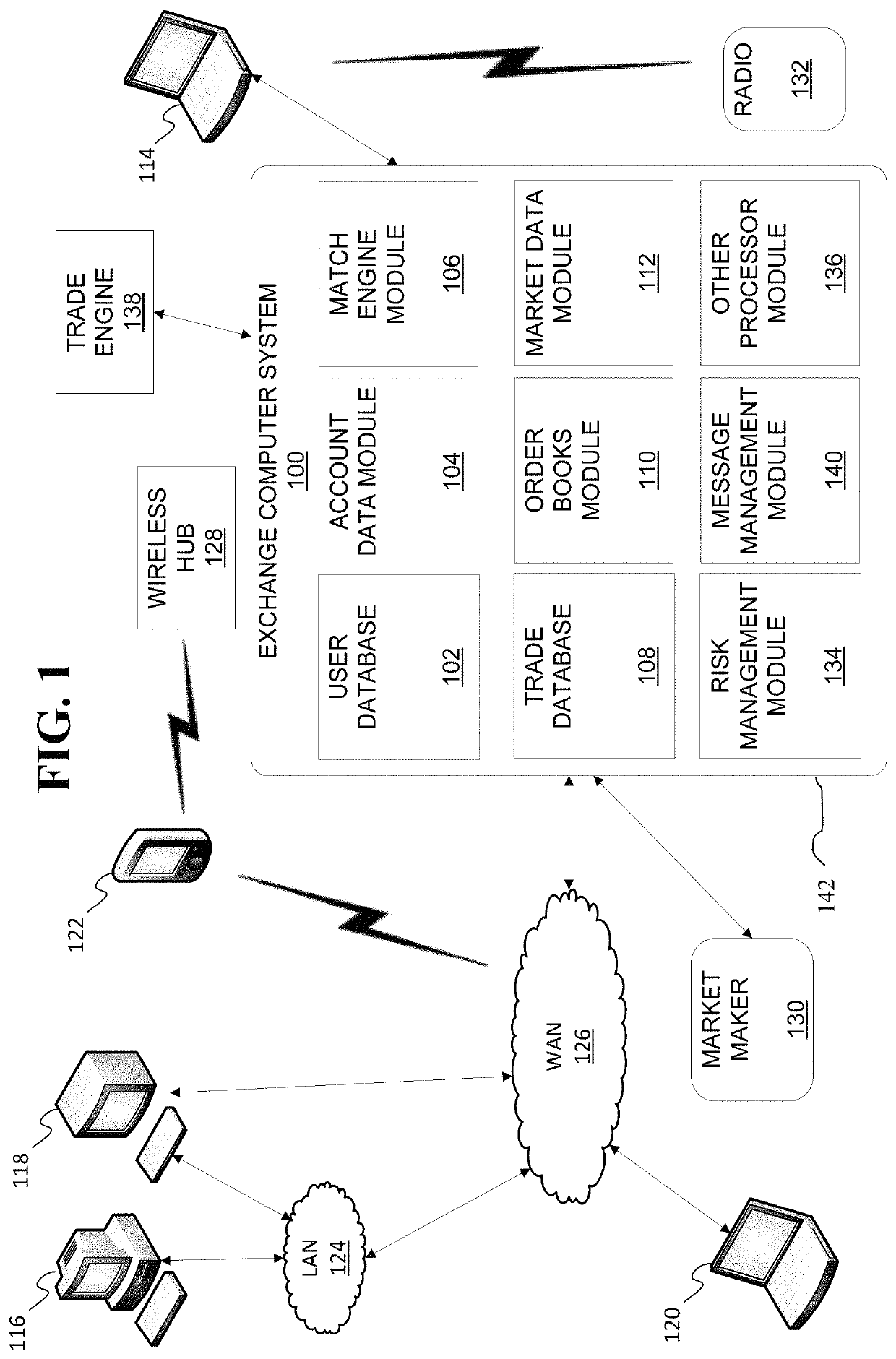

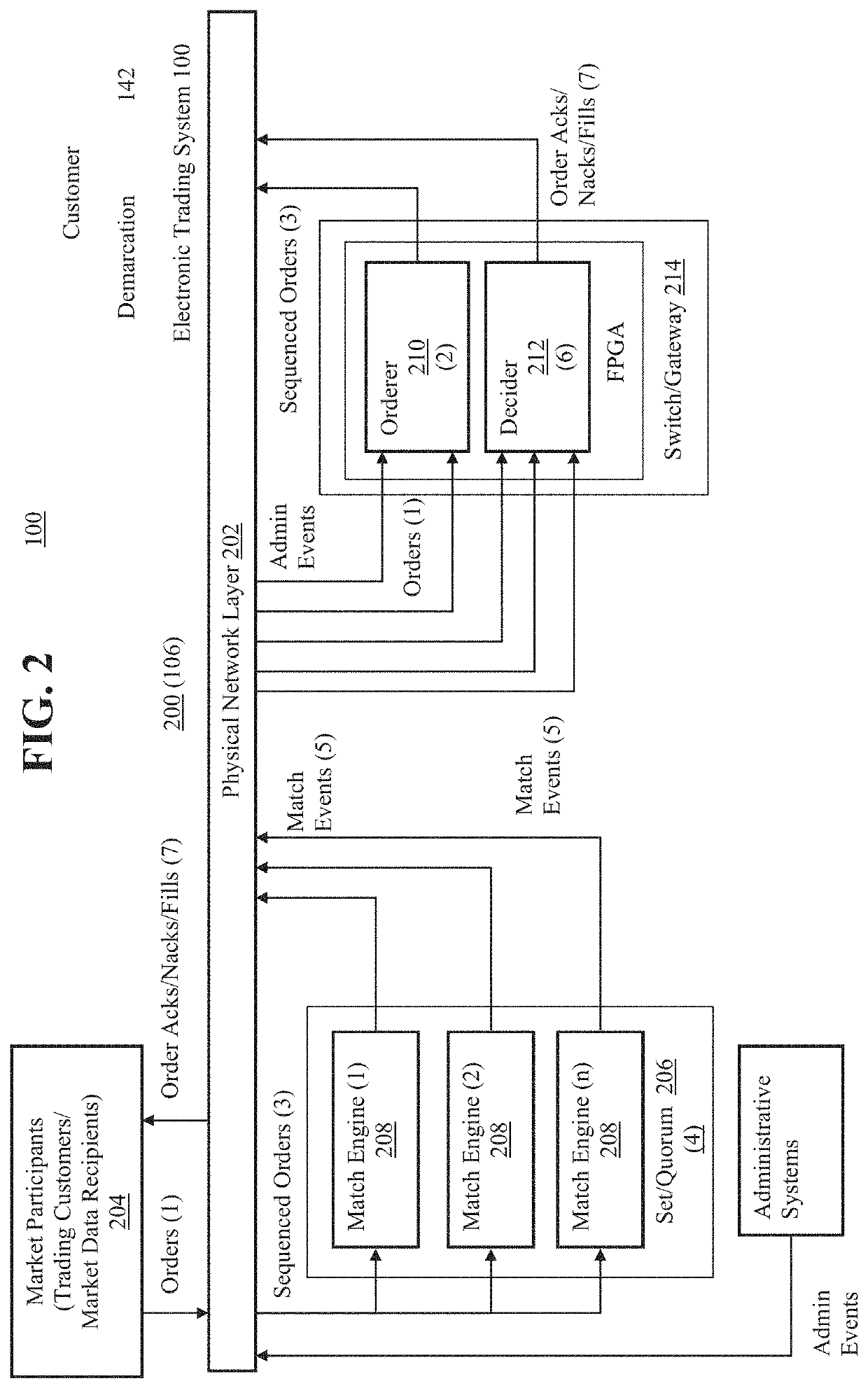

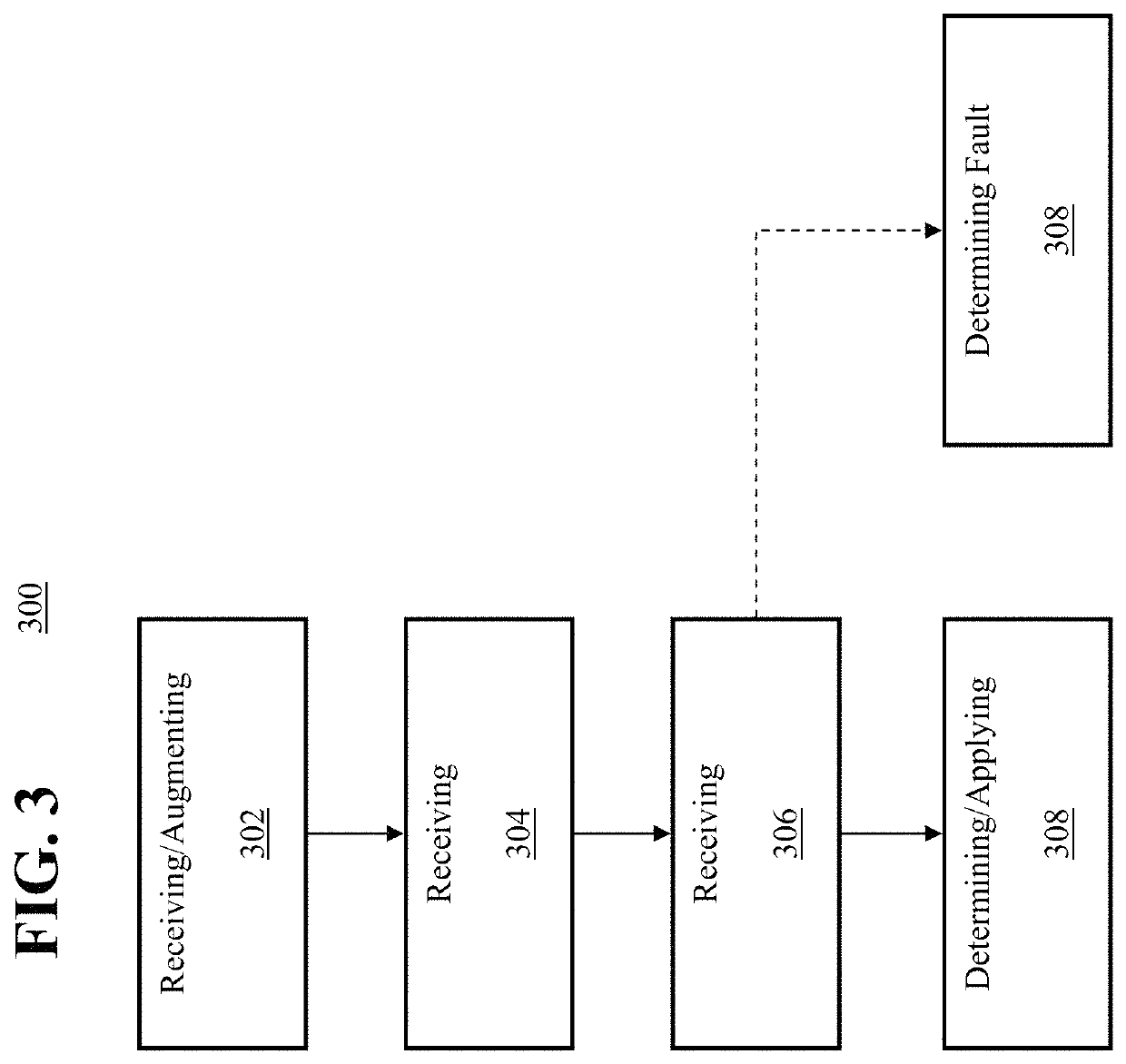

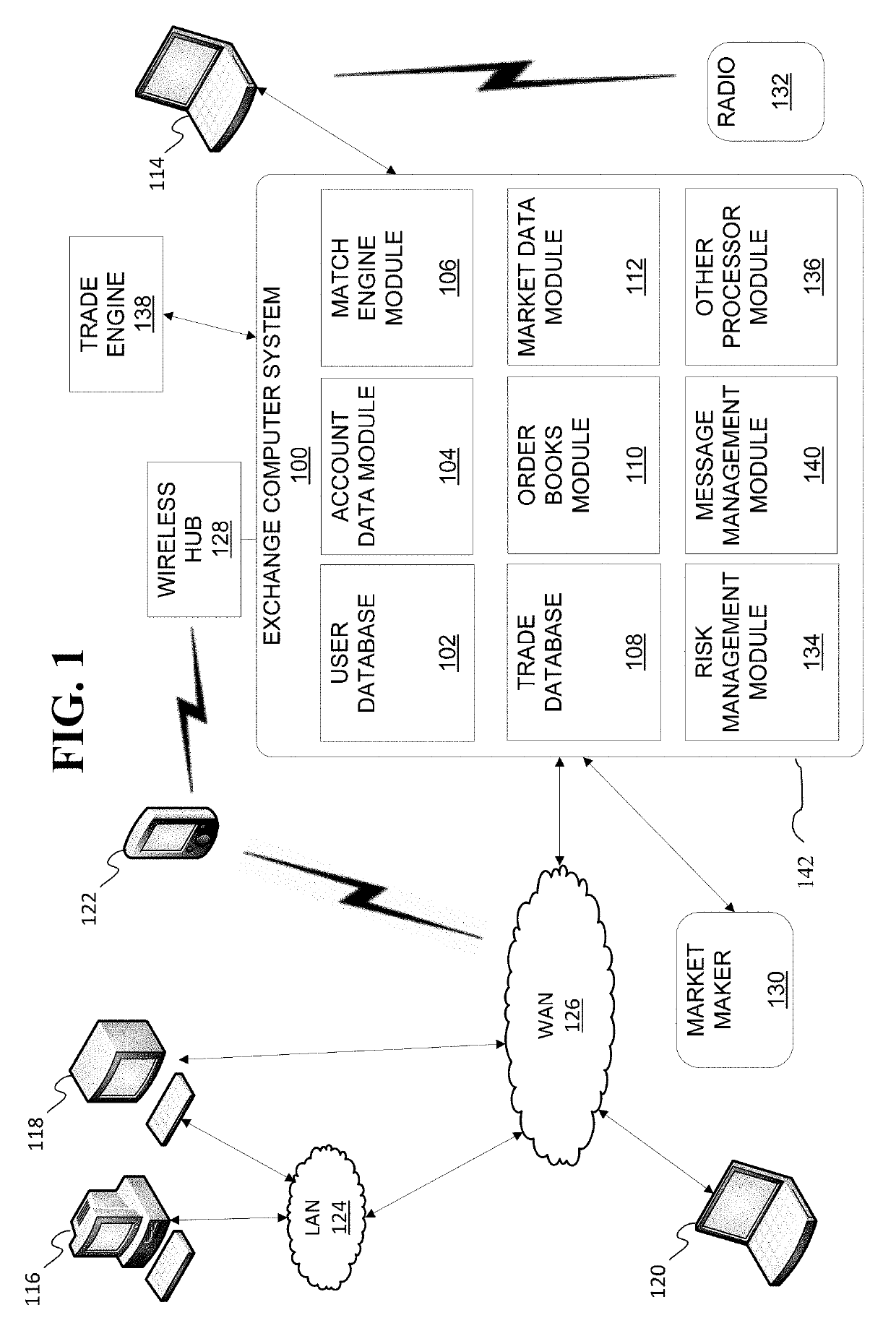

Transactionally Deterministic High Speed Financial Exchange Having Improved, Efficiency, Communication, Customization, Performance, Access, Trading Opportunities, Credit Controls, and Fault Tolerance

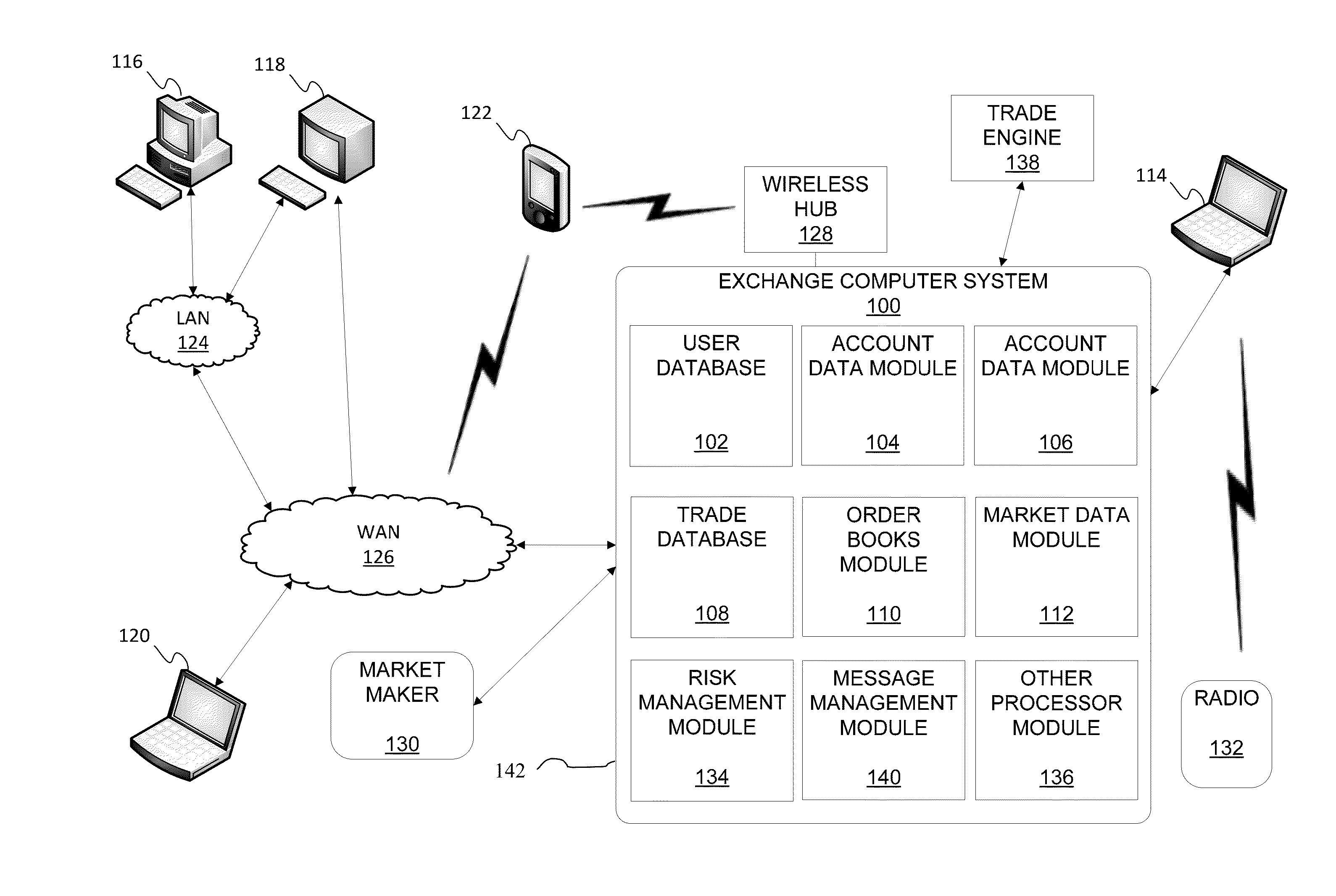

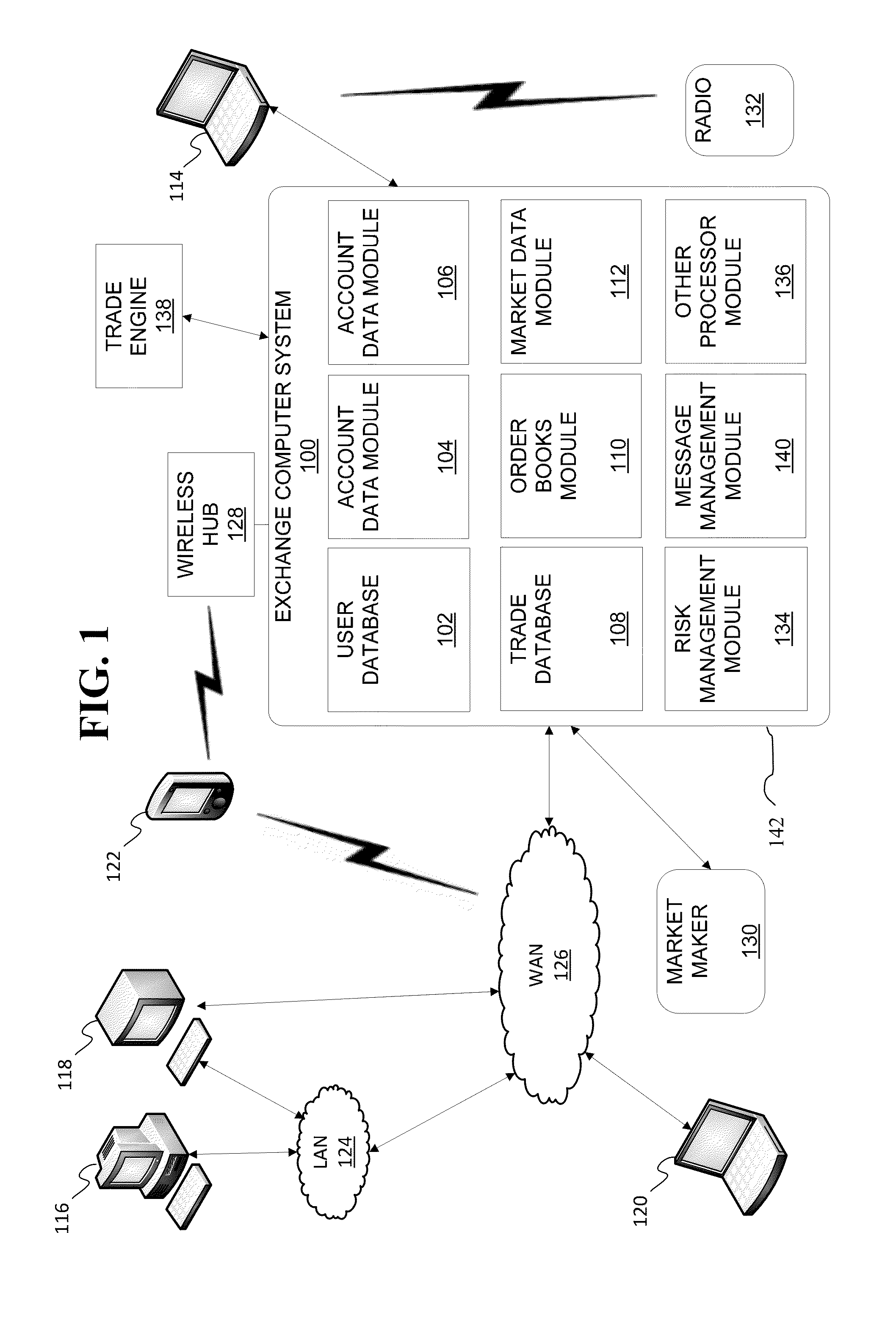

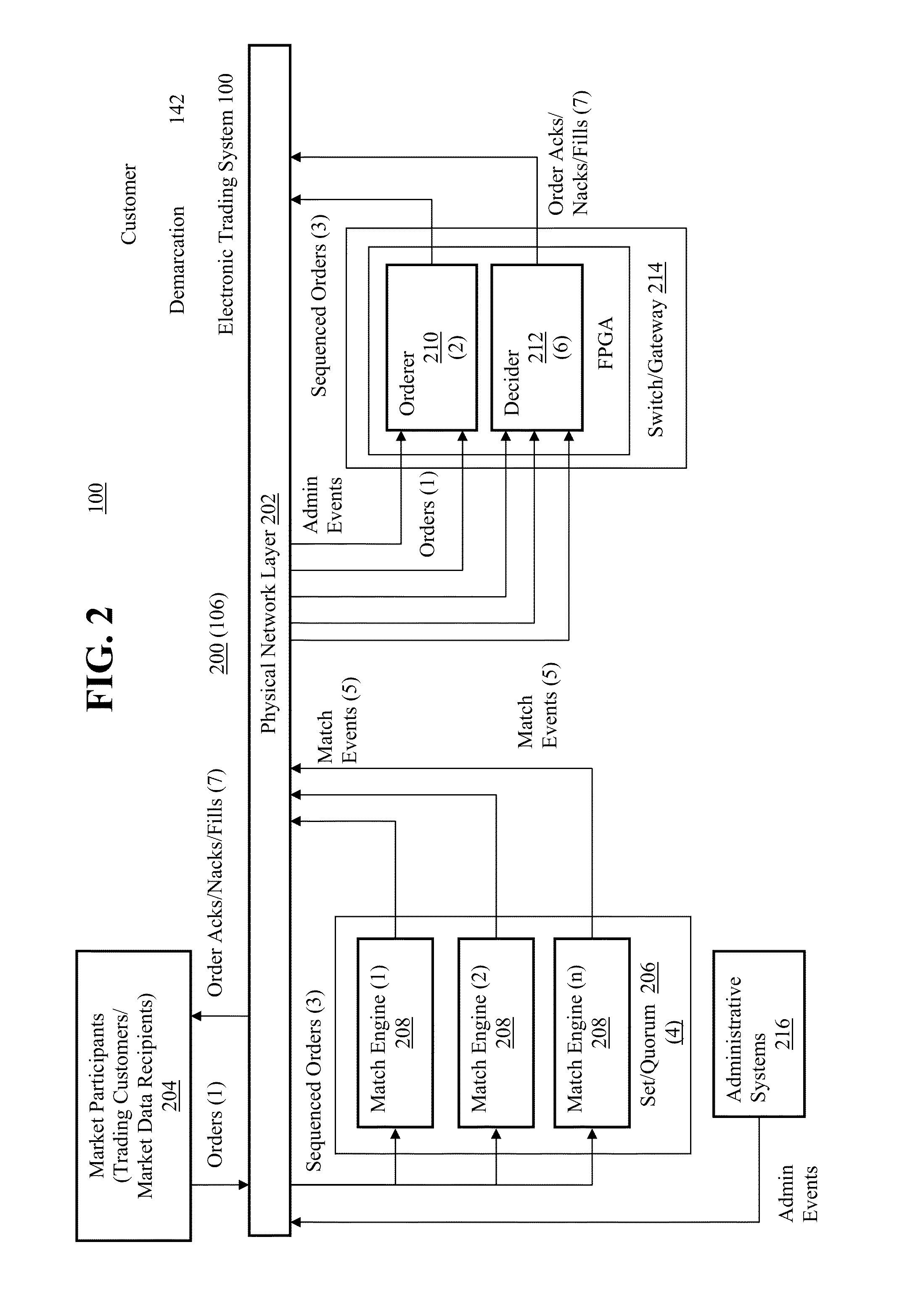

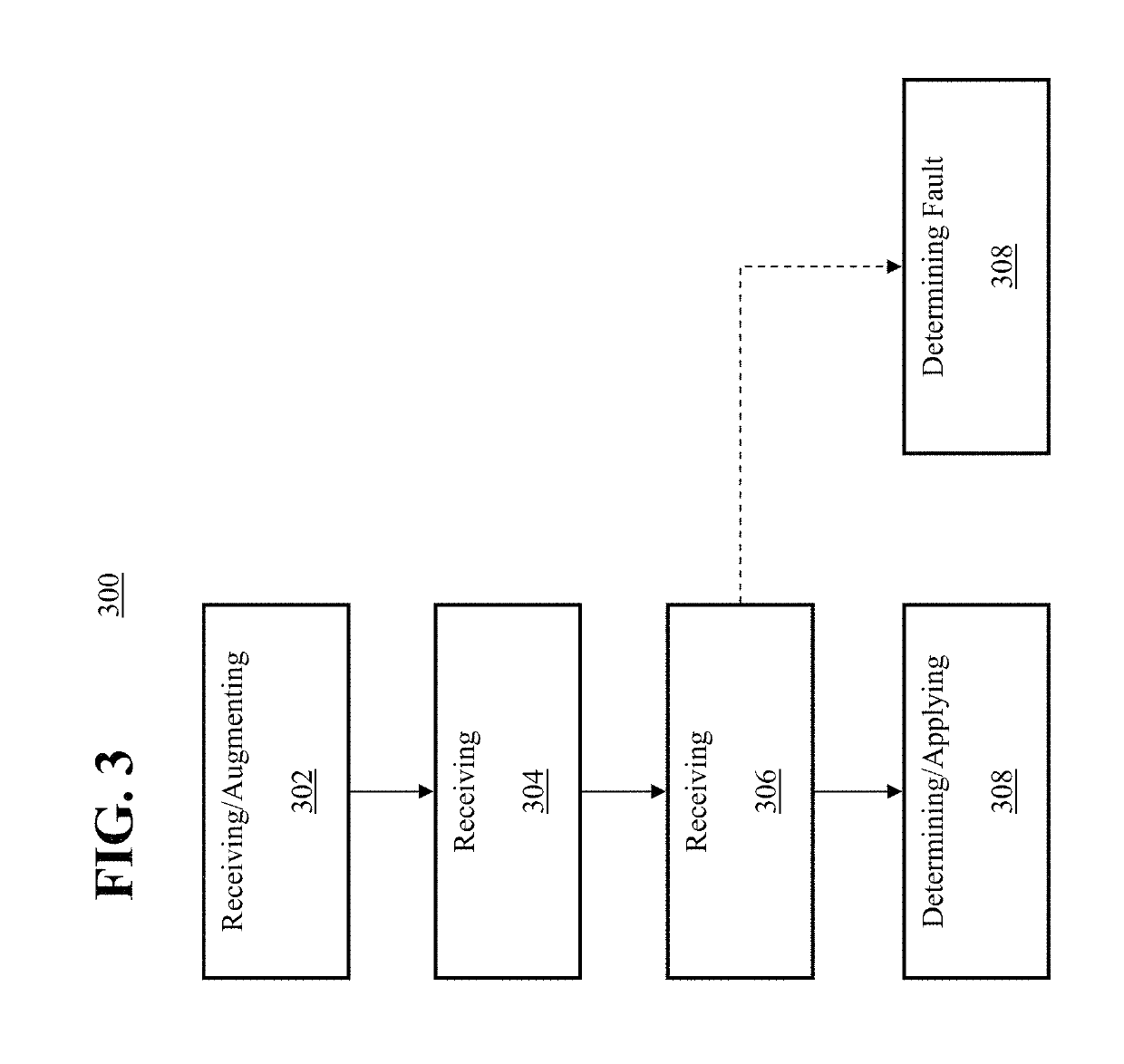

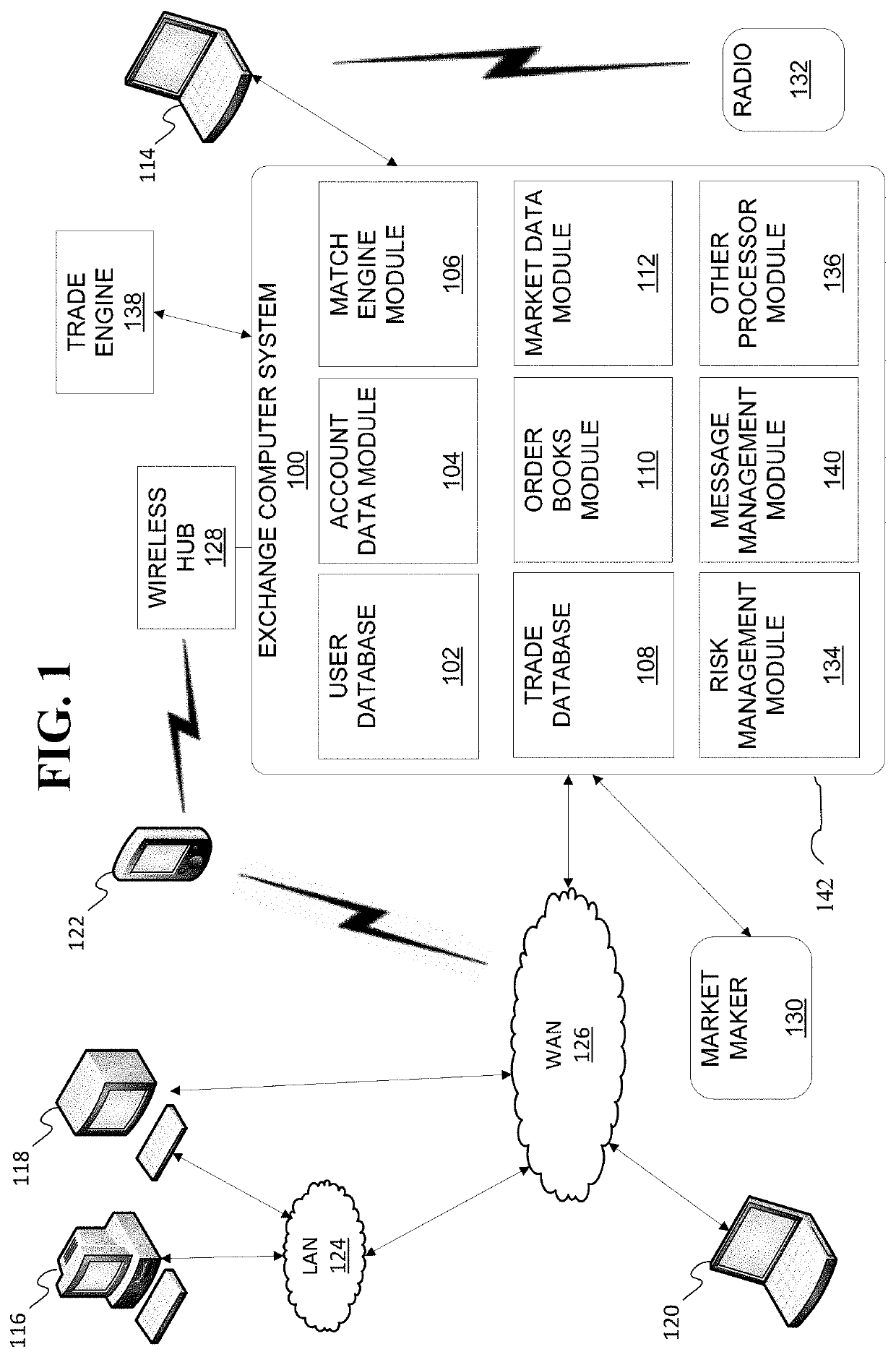

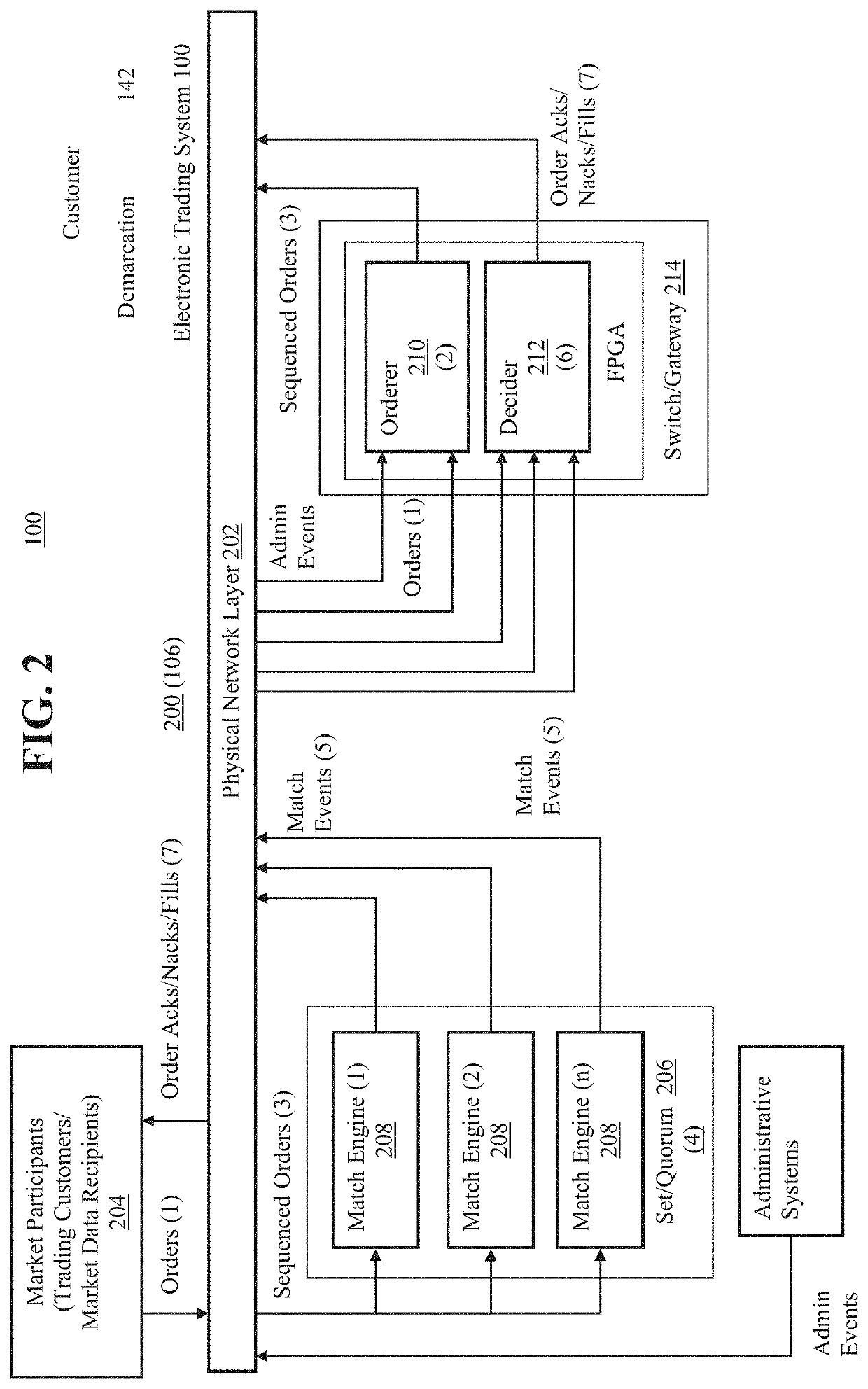

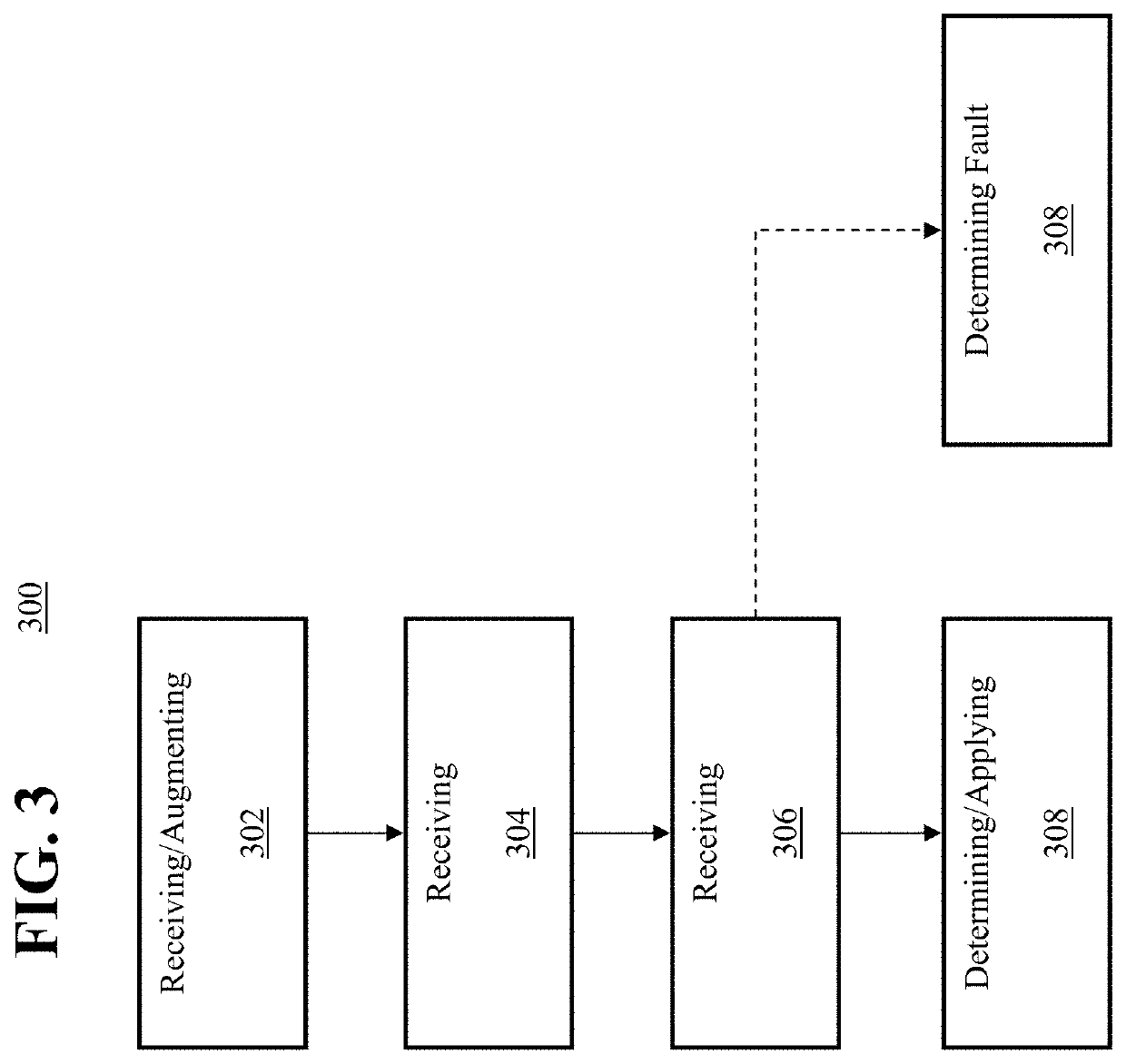

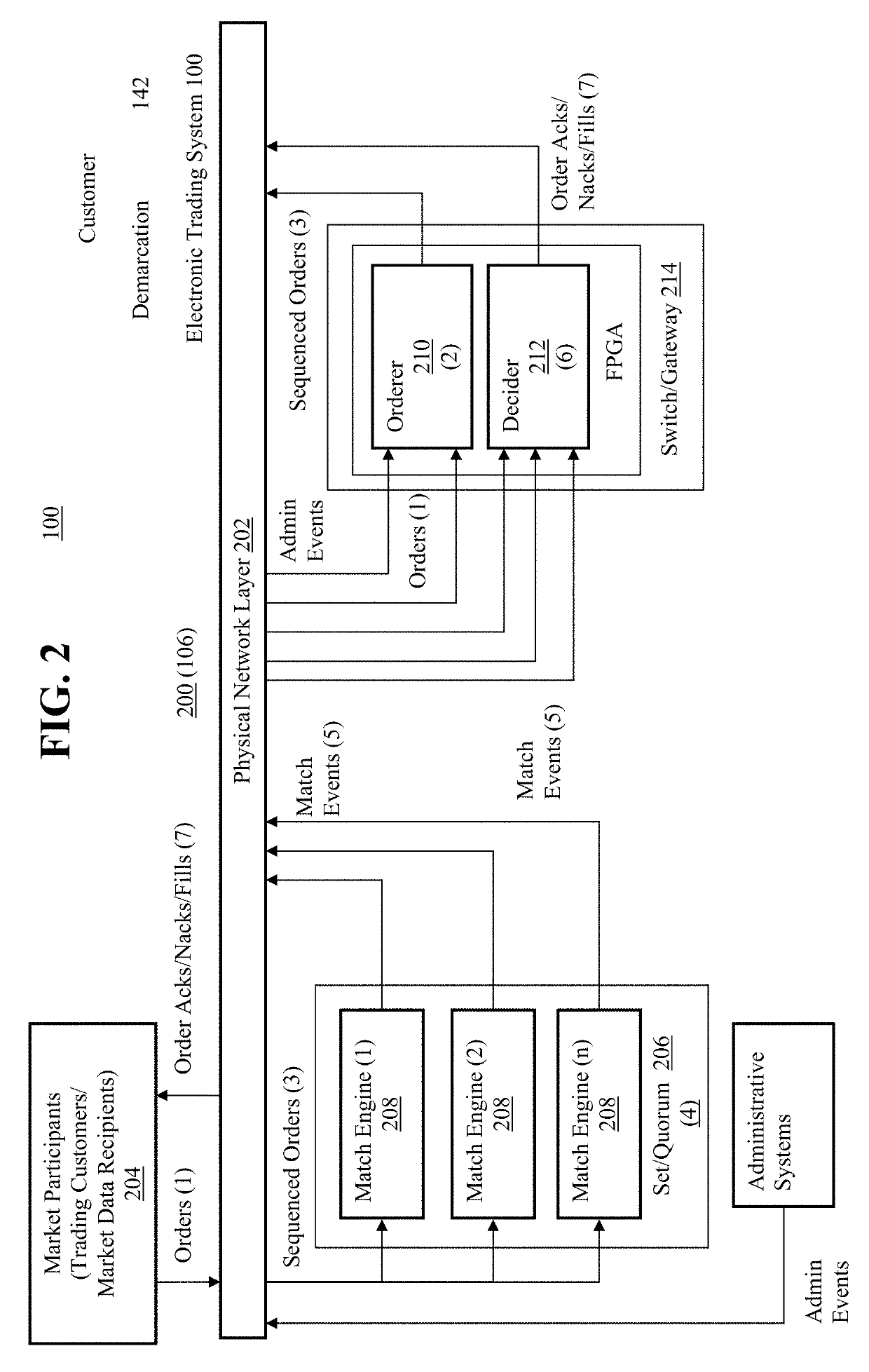

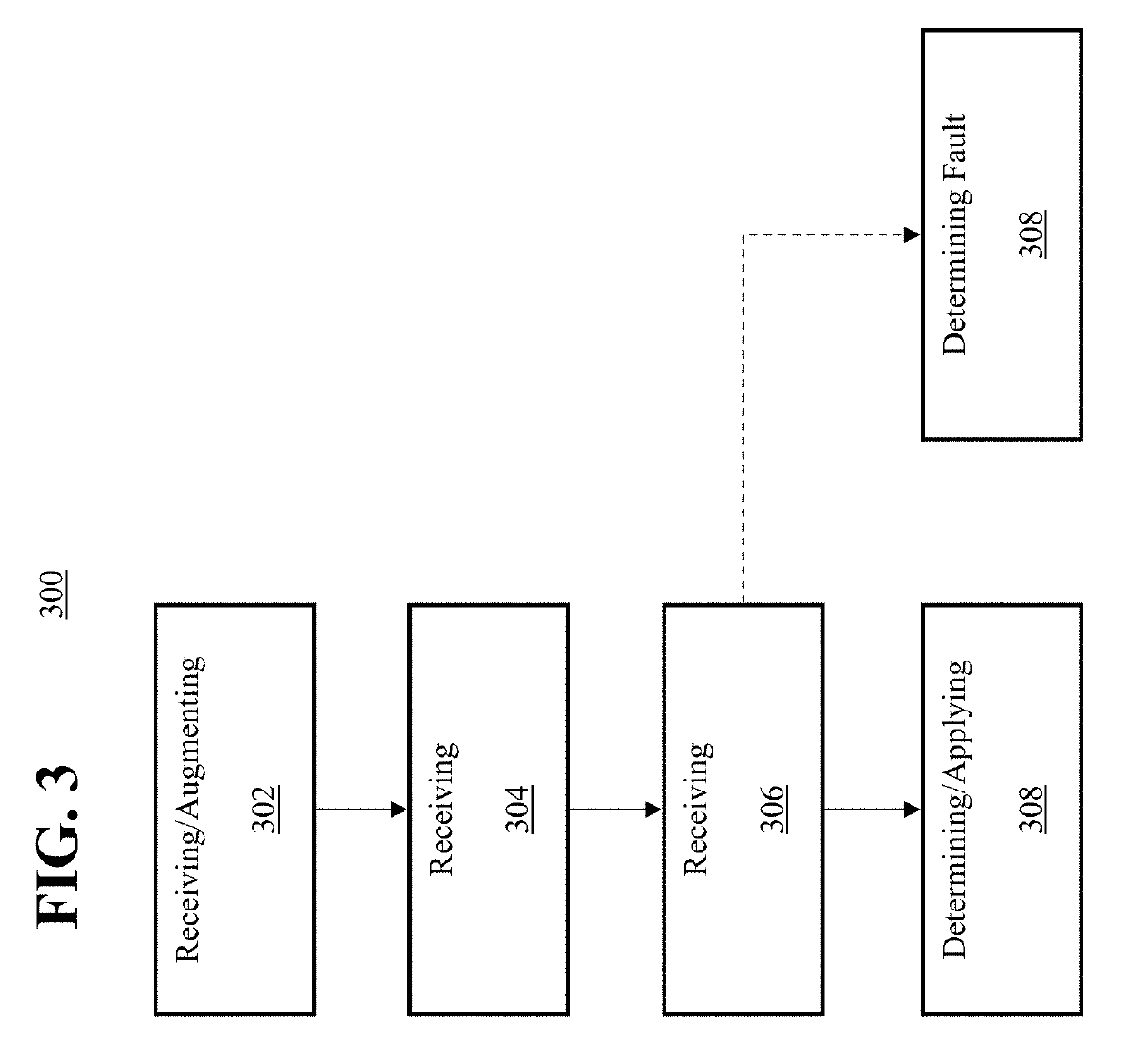

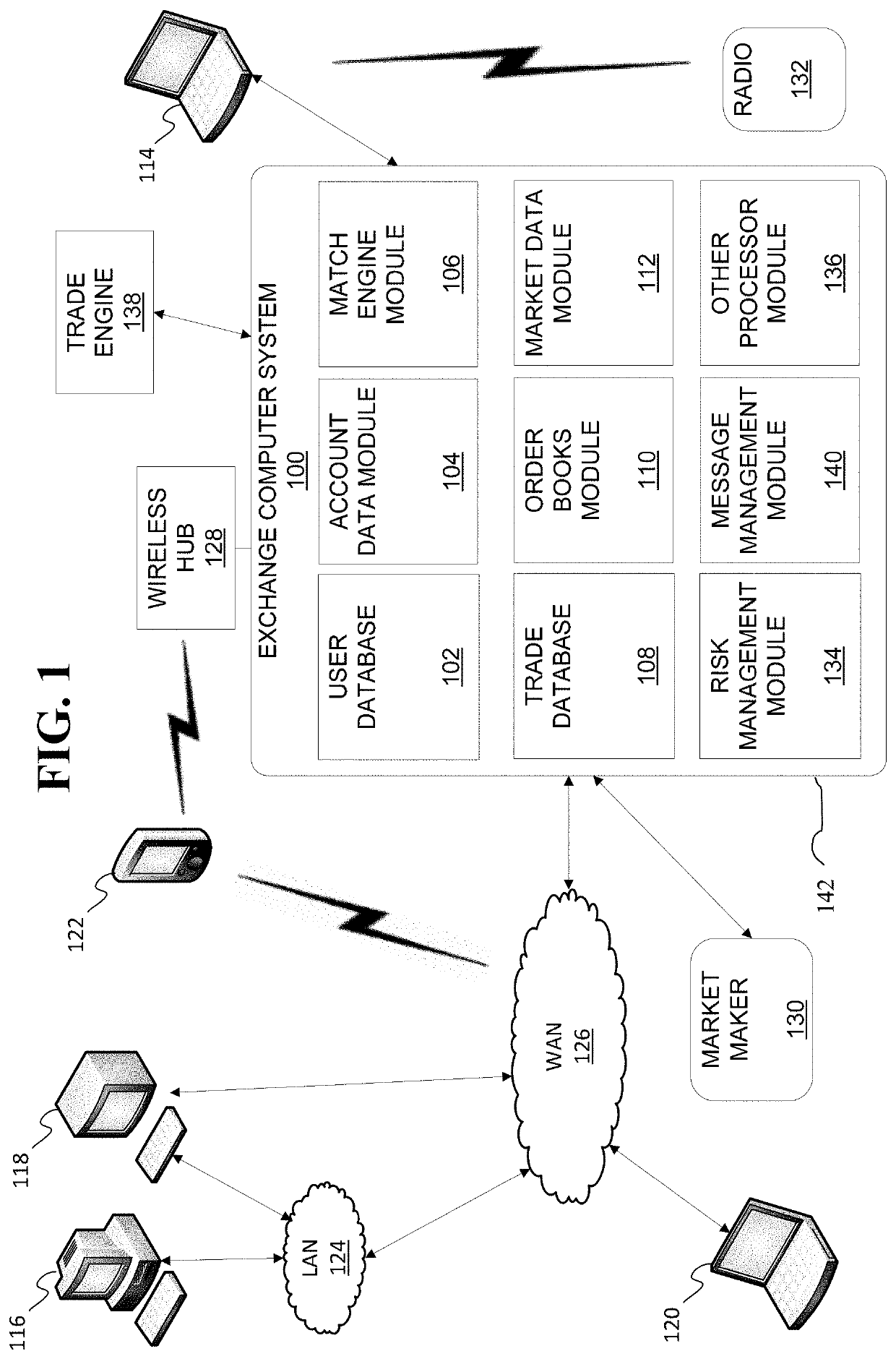

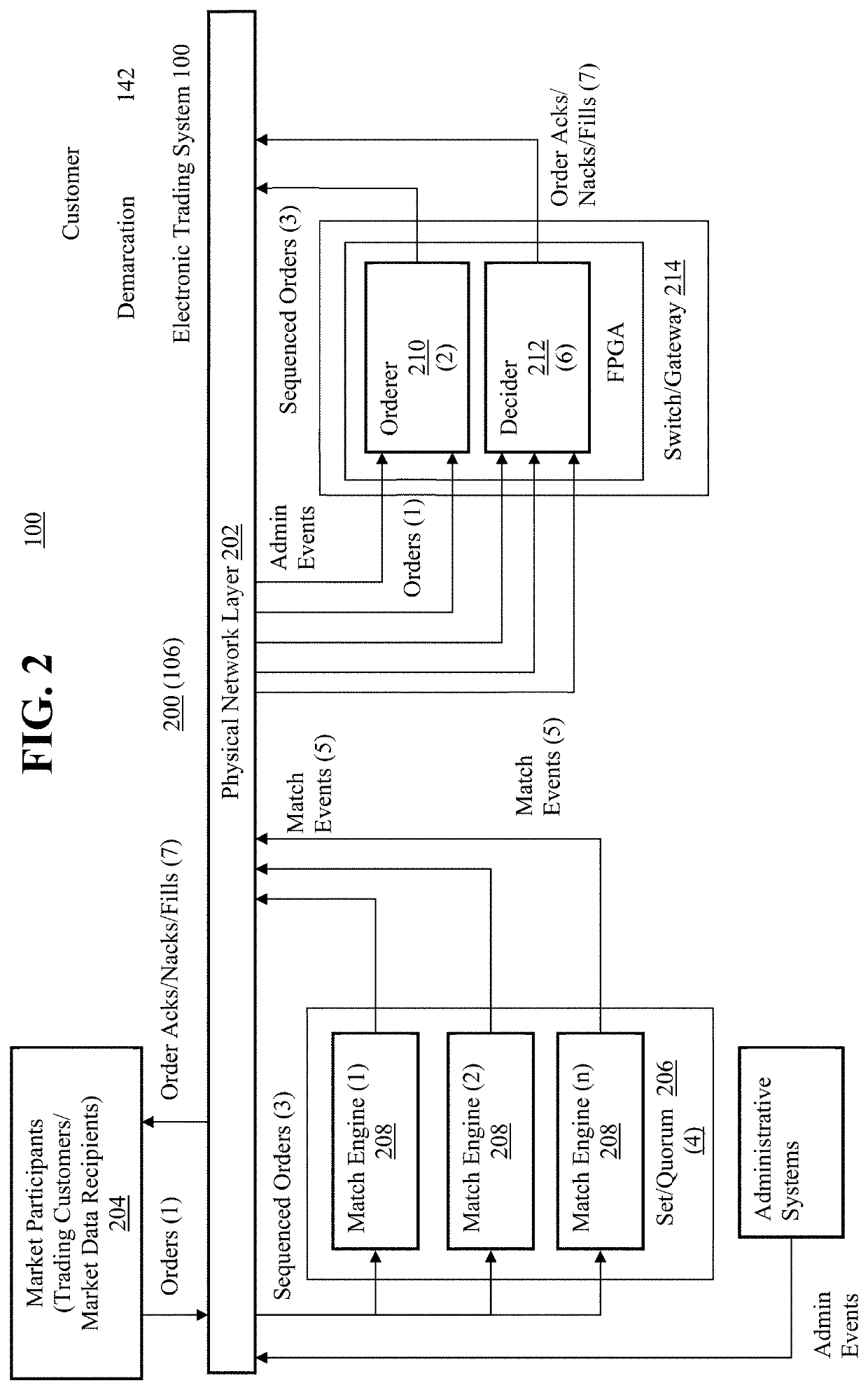

The disclosed embodiments relate to implementation of a trading system, which may also be referred to as a trading system architecture, having improved performance which further assures transactional determinism under increasing processing transaction loads while providing improved trading opportunities, fault tolerance, low latency processing, high volume capacity, risk mitigation and market protections with minimal impact, as well as improved and equitable access to information and opportunities.

Owner:CHICAGO MERCANTILE EXCHANGE INC

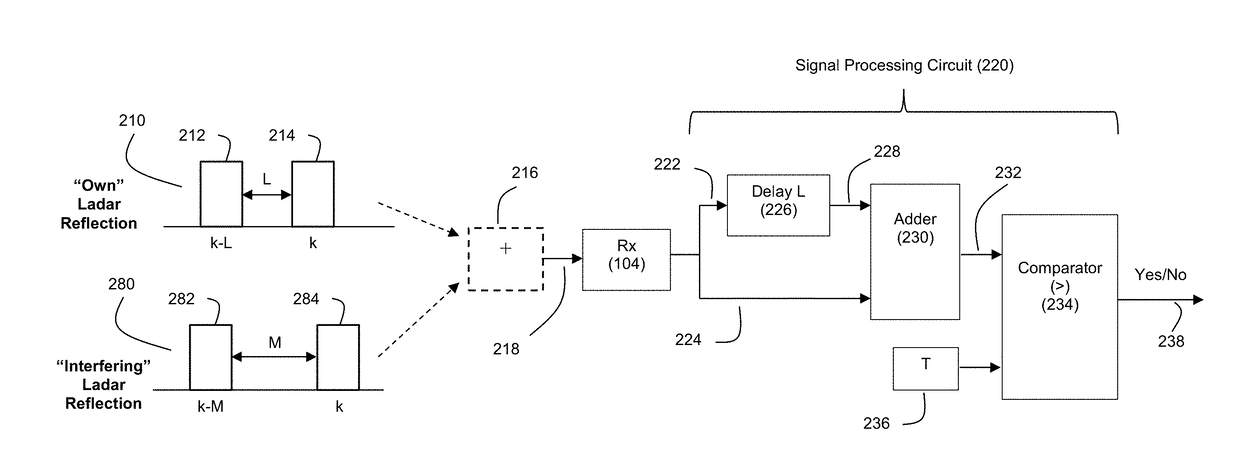

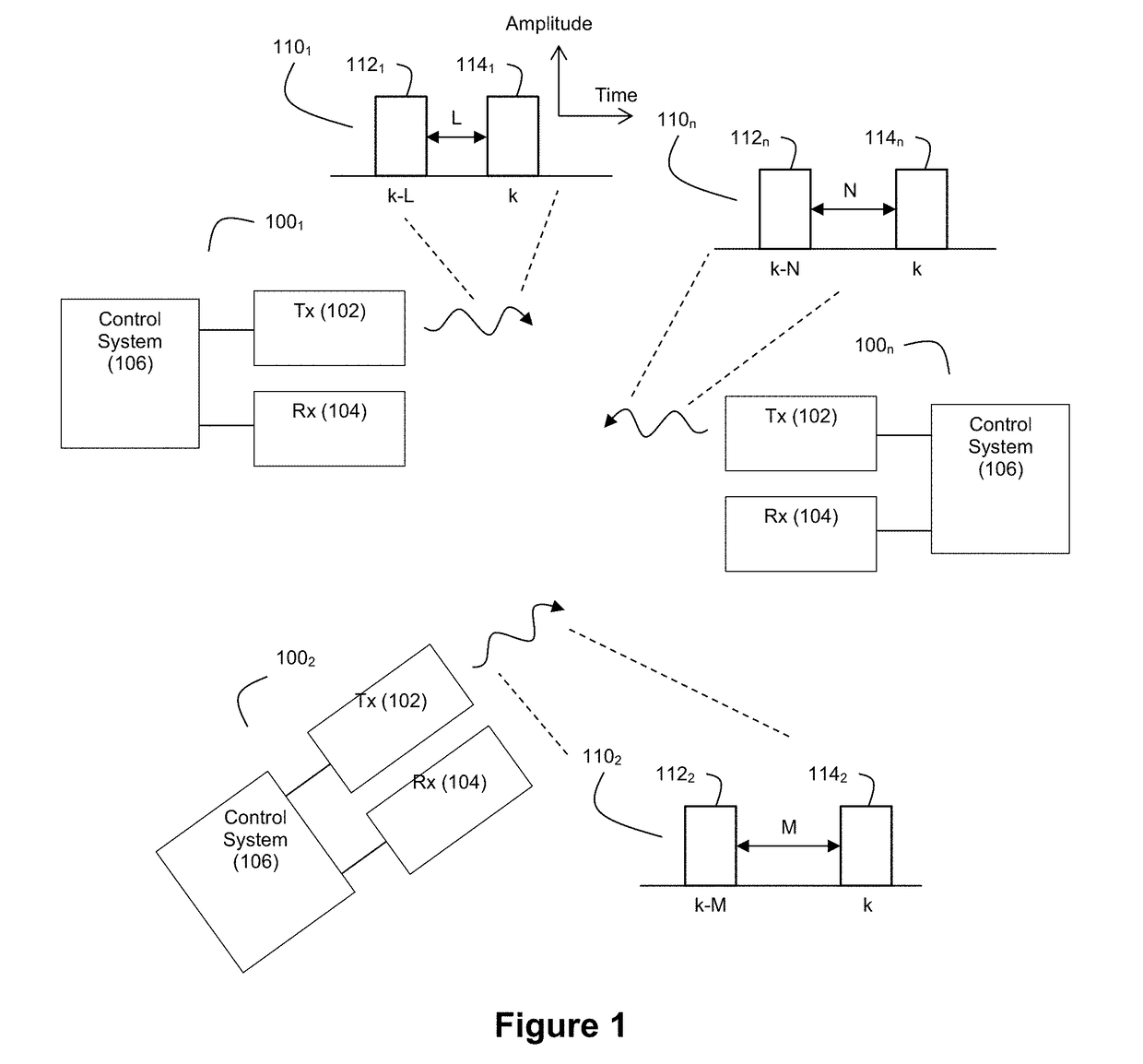

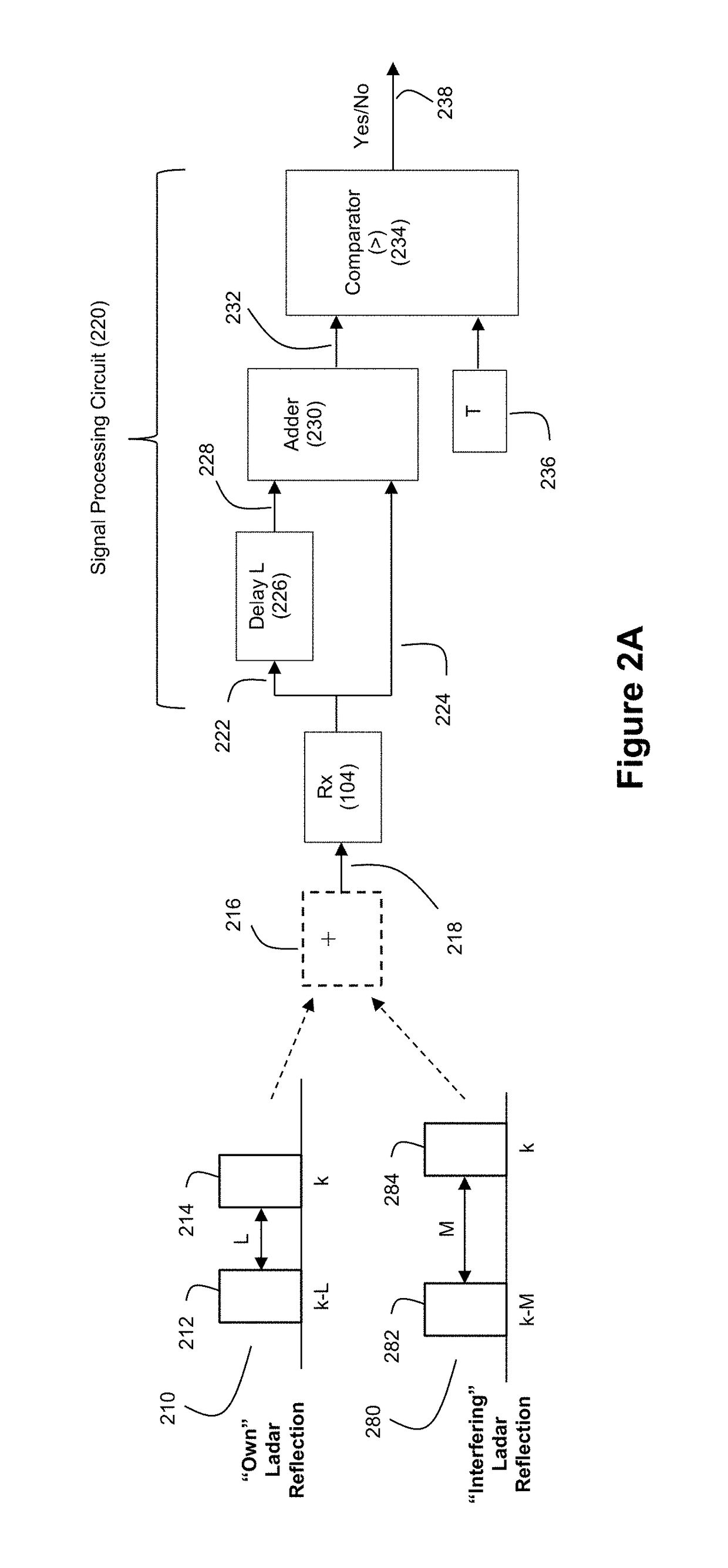

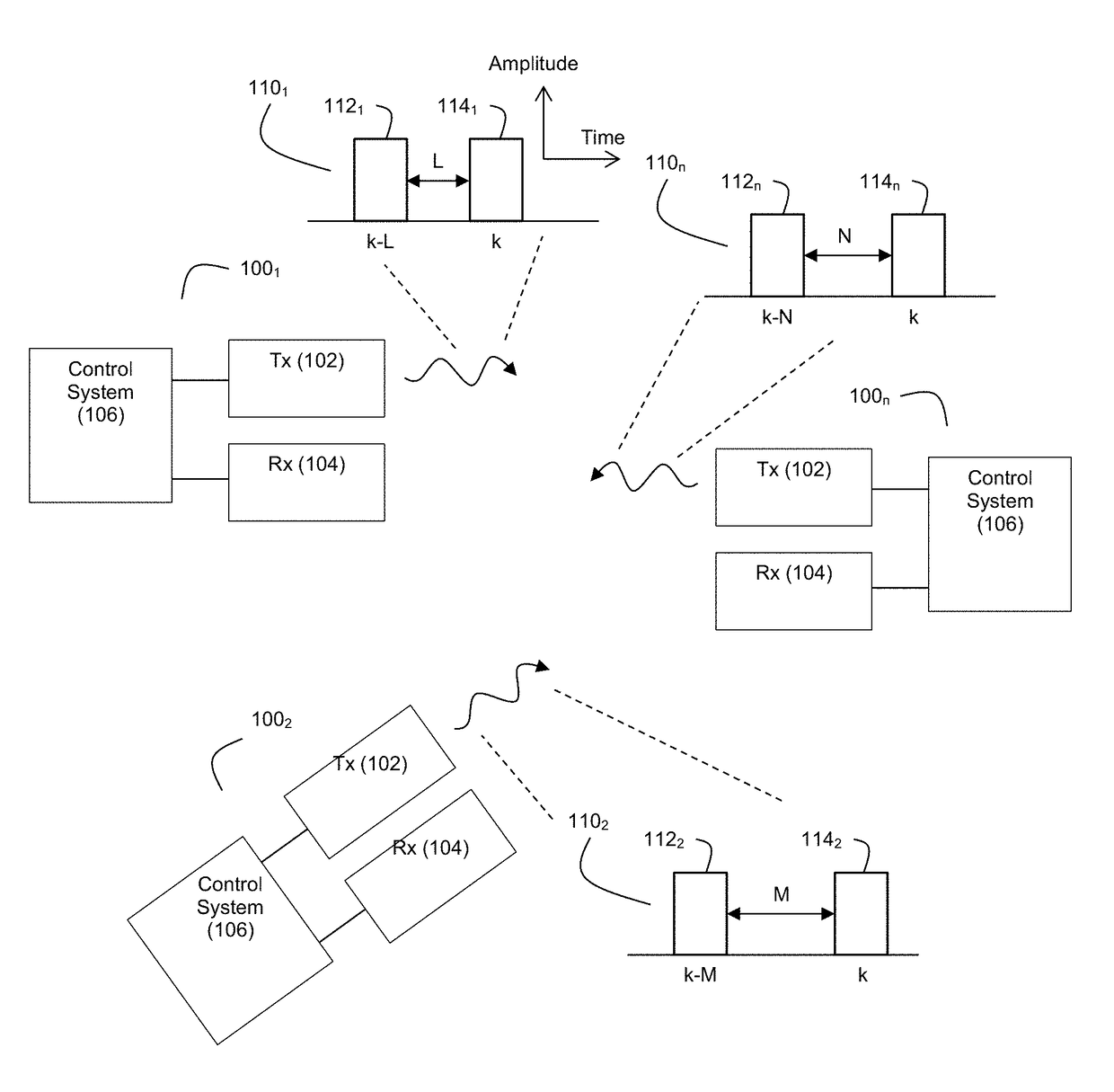

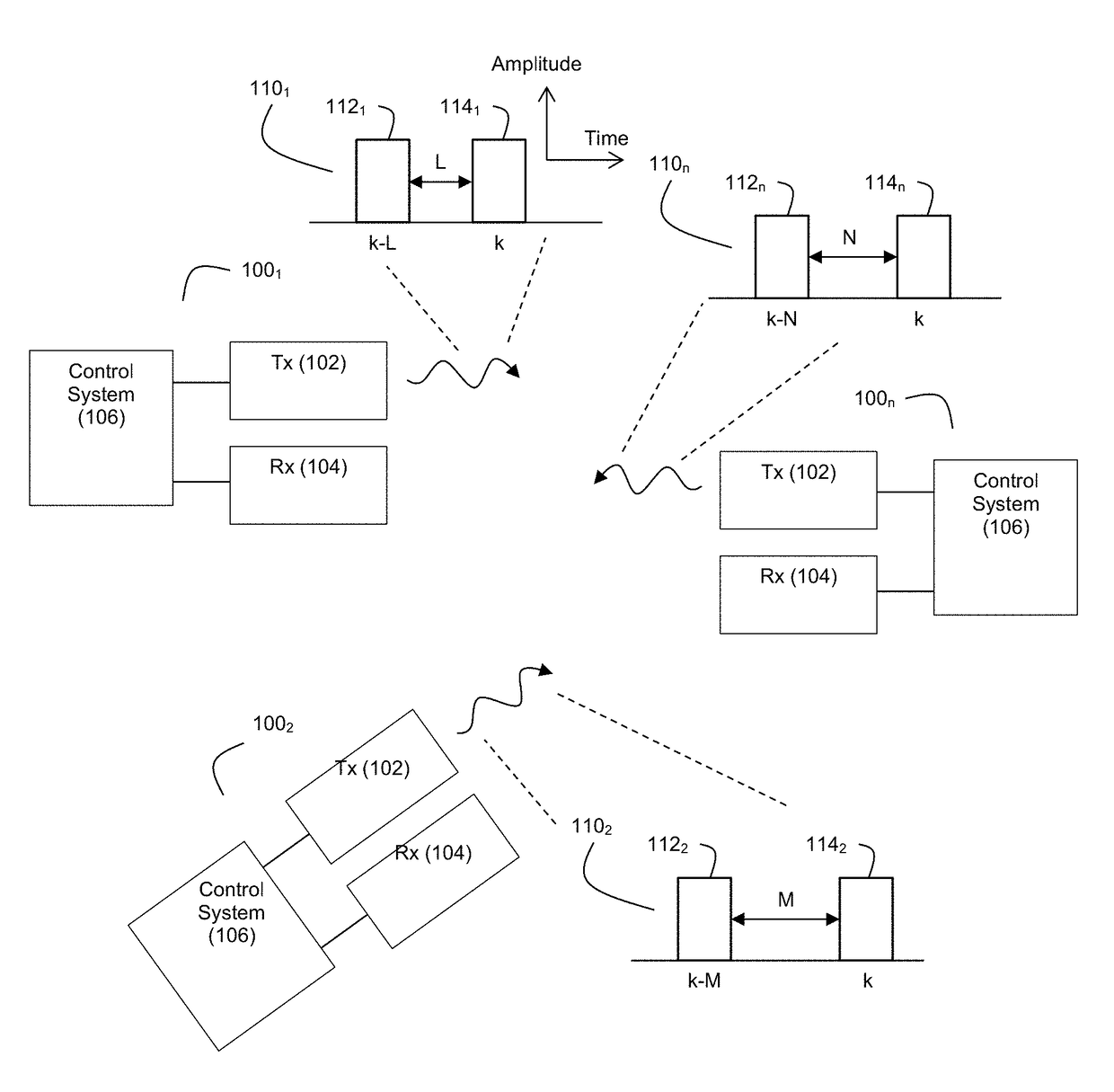

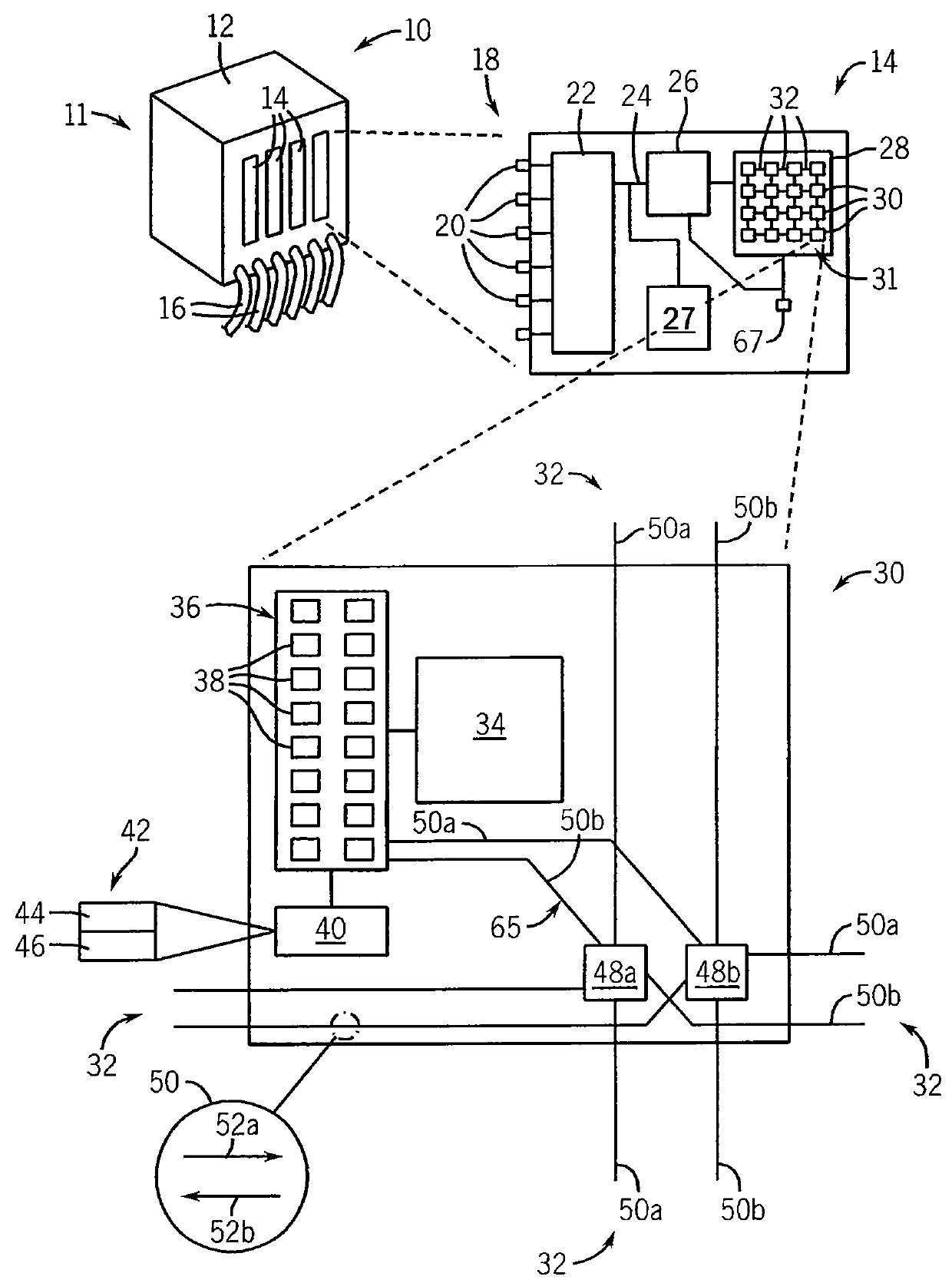

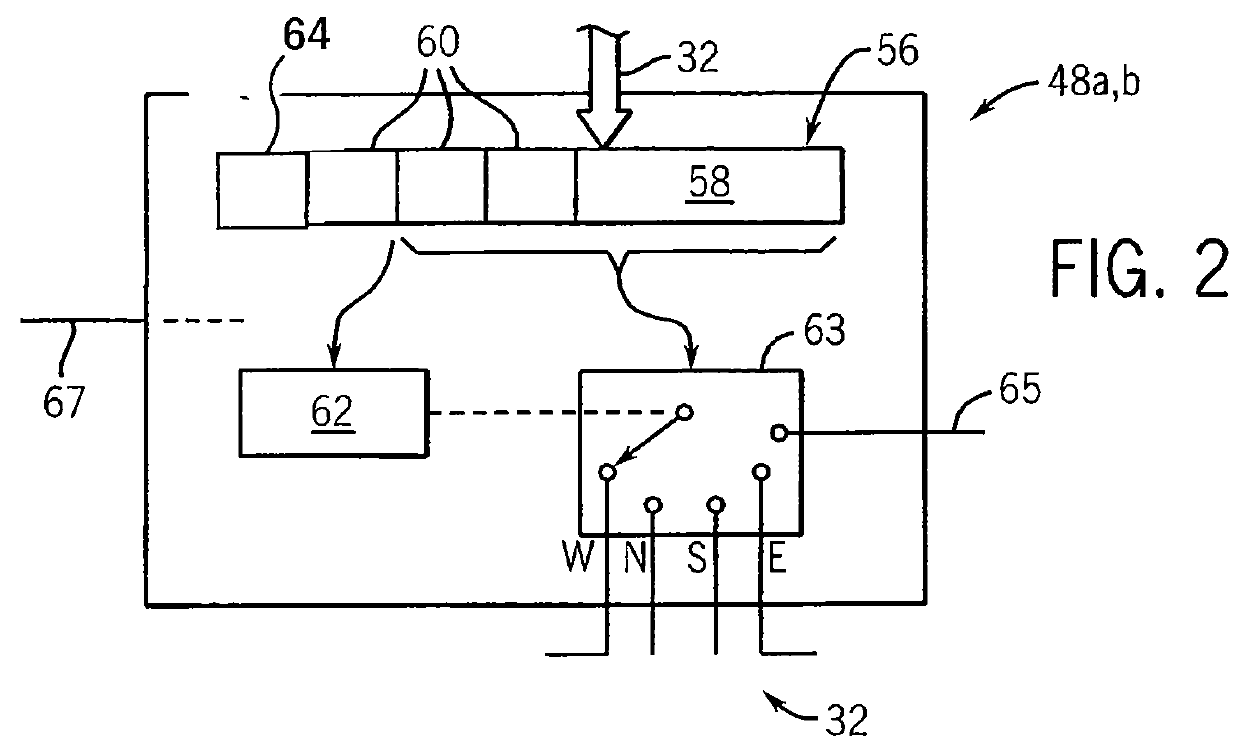

Ladar Pulse Deconfliction Apparatus

ActiveUS20180238998A1Short time intervalReduce the numberElectromagnetic wave reradiationRadio wave reradiation/reflectionCommunications systemRadar systems

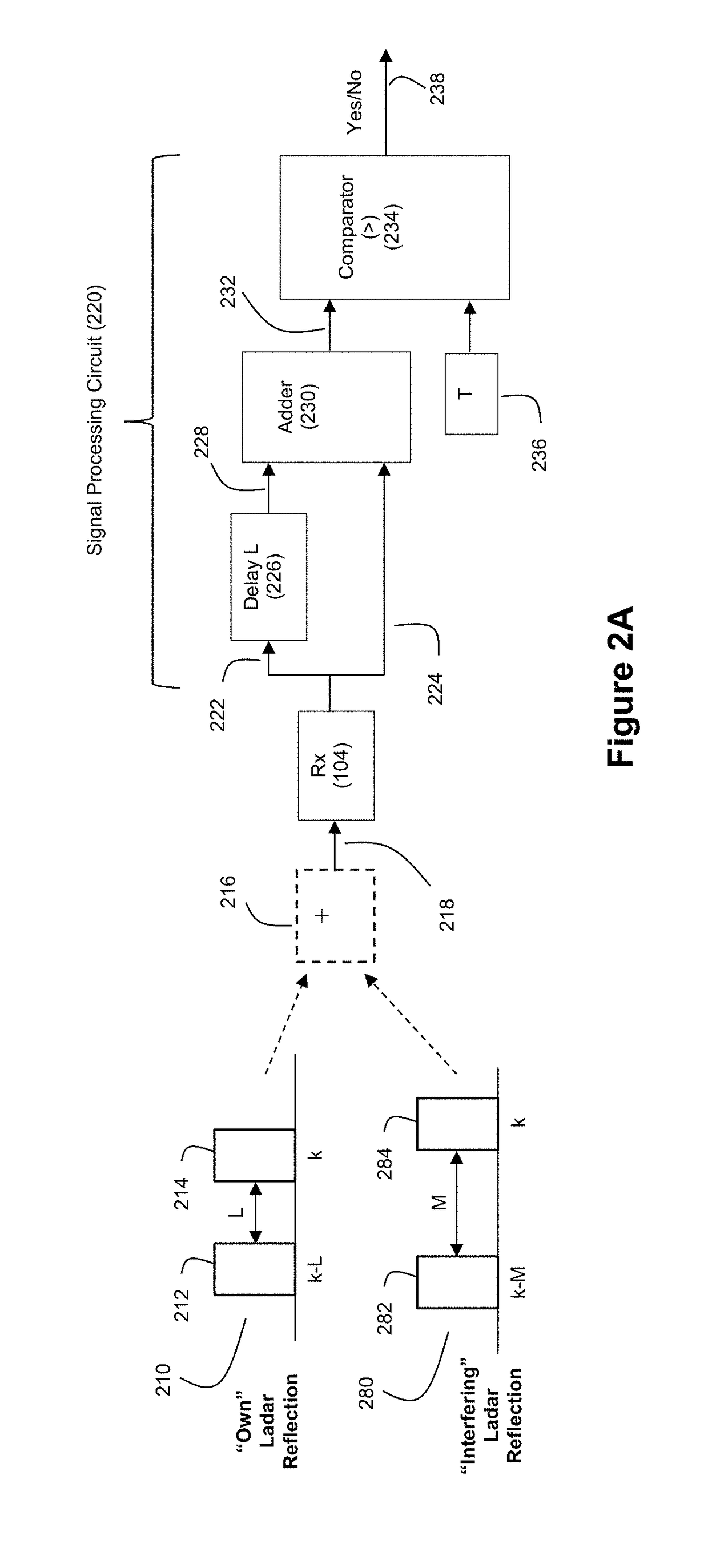

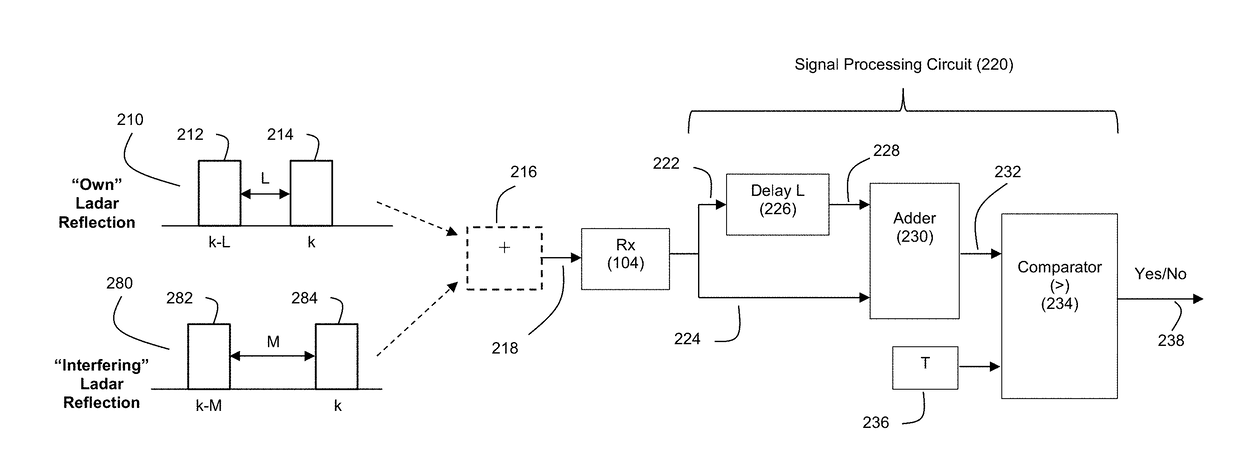

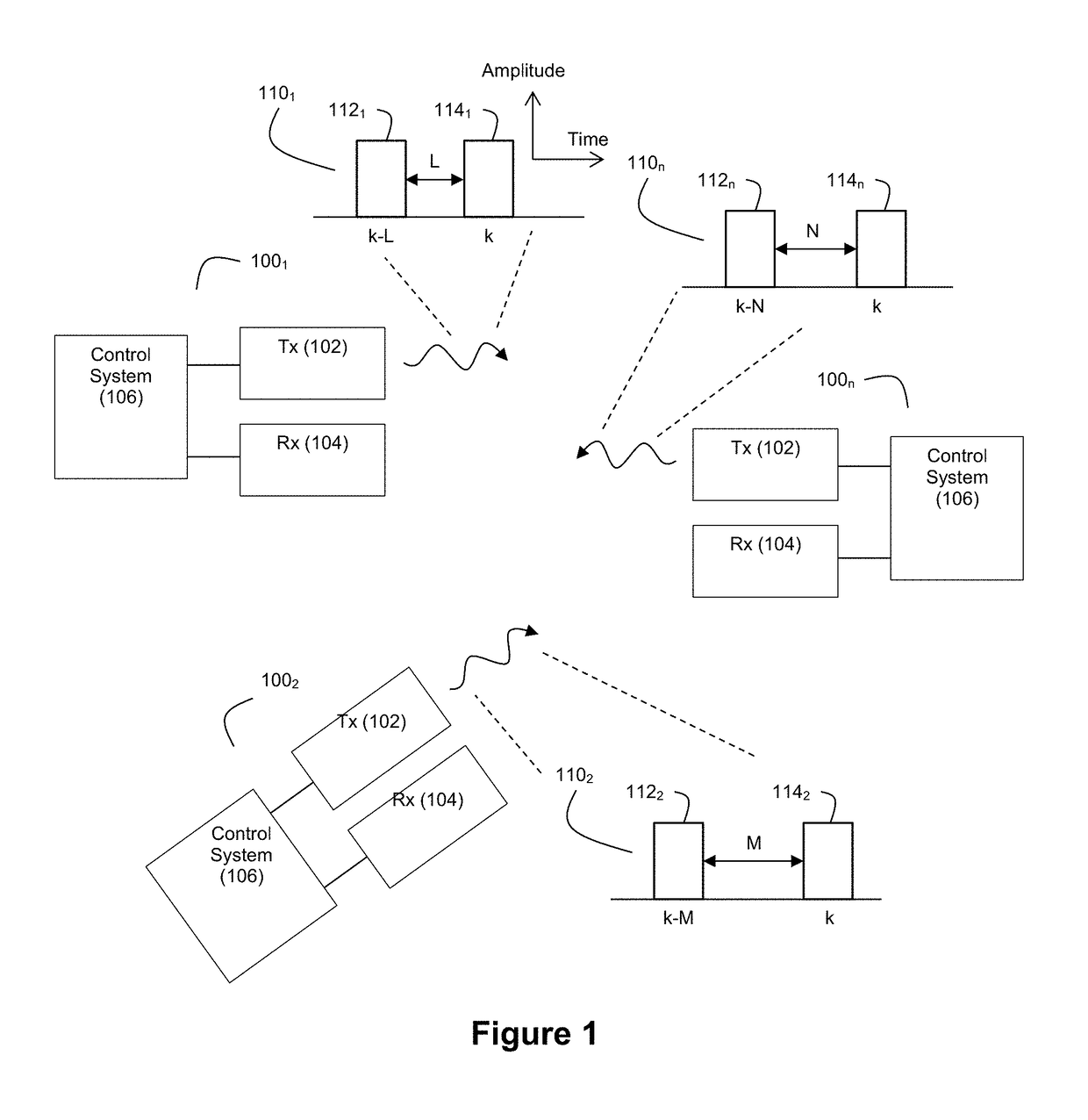

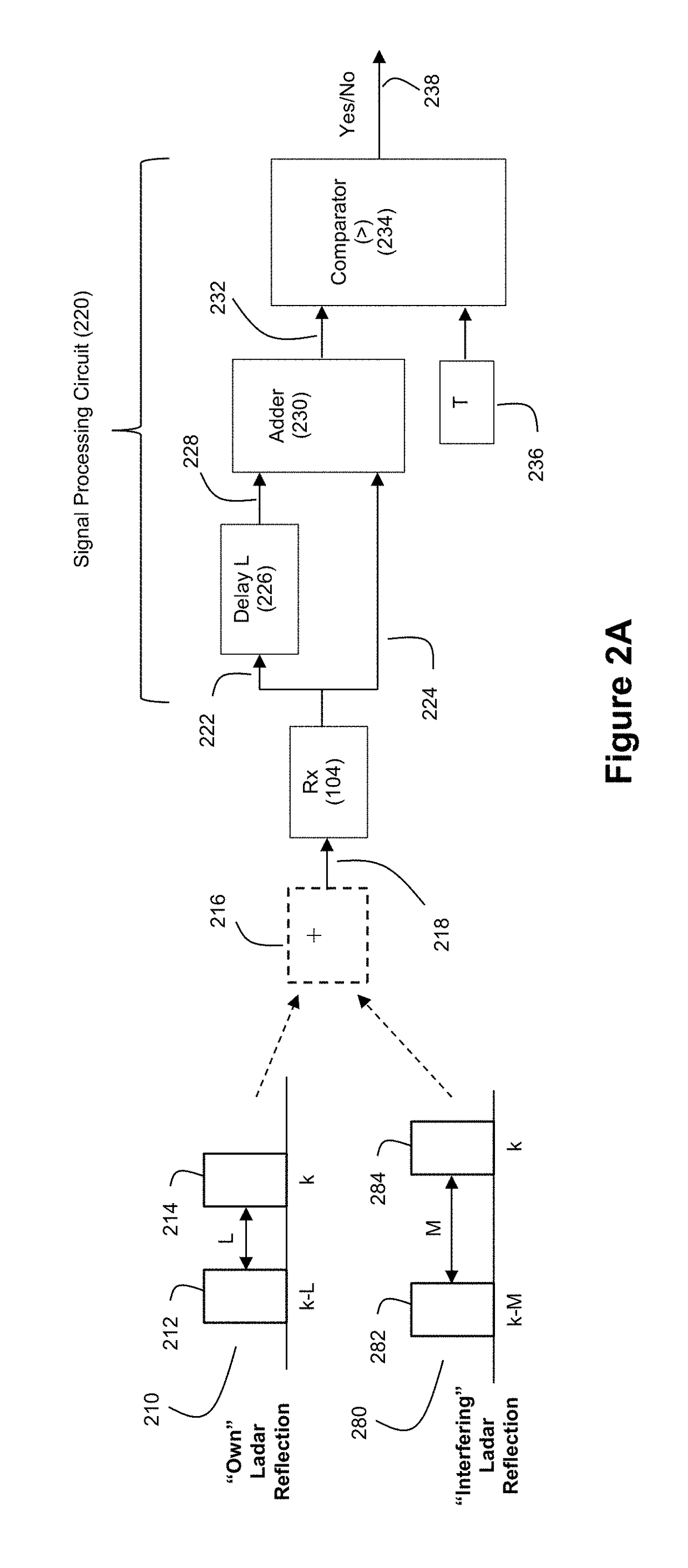

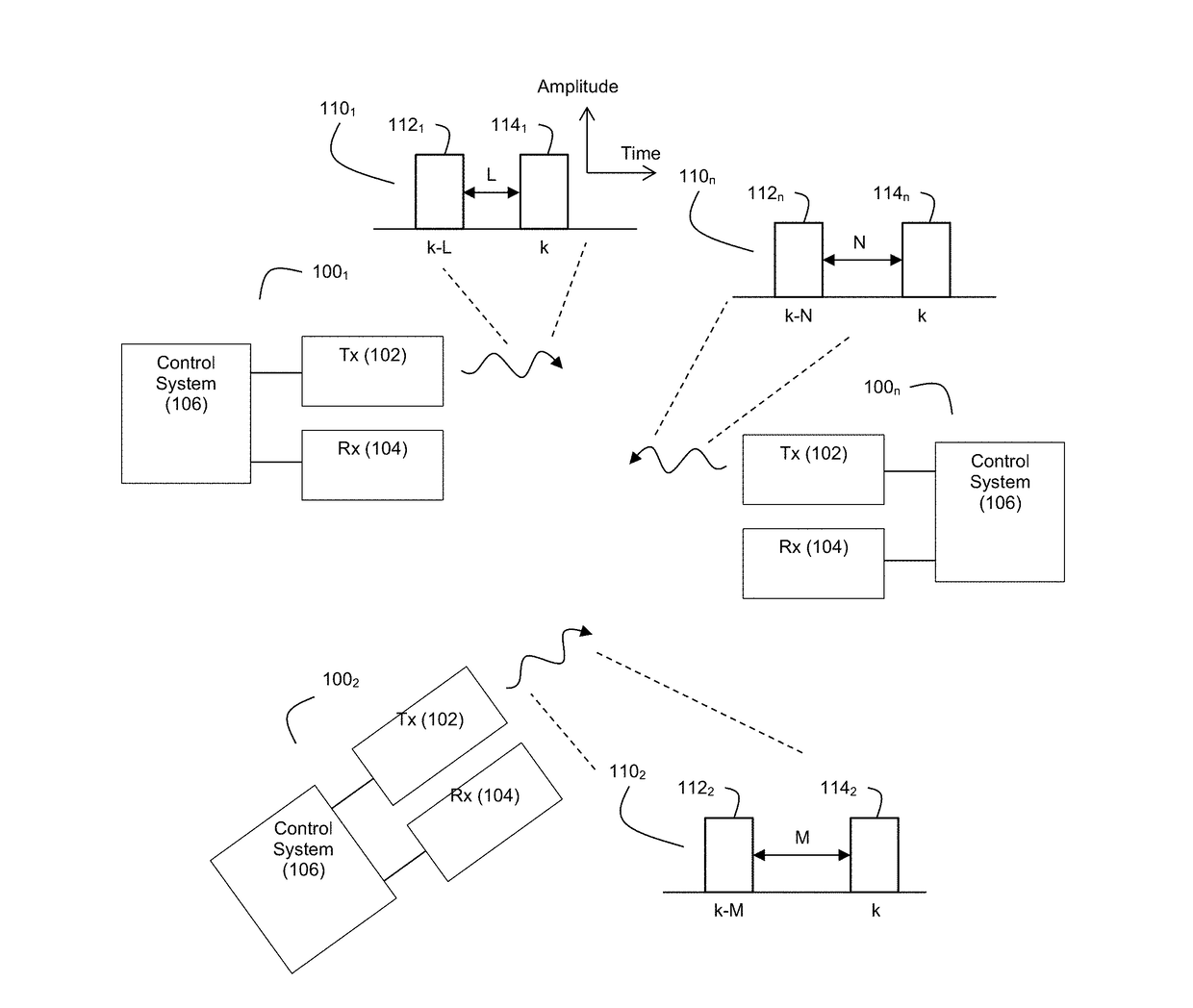

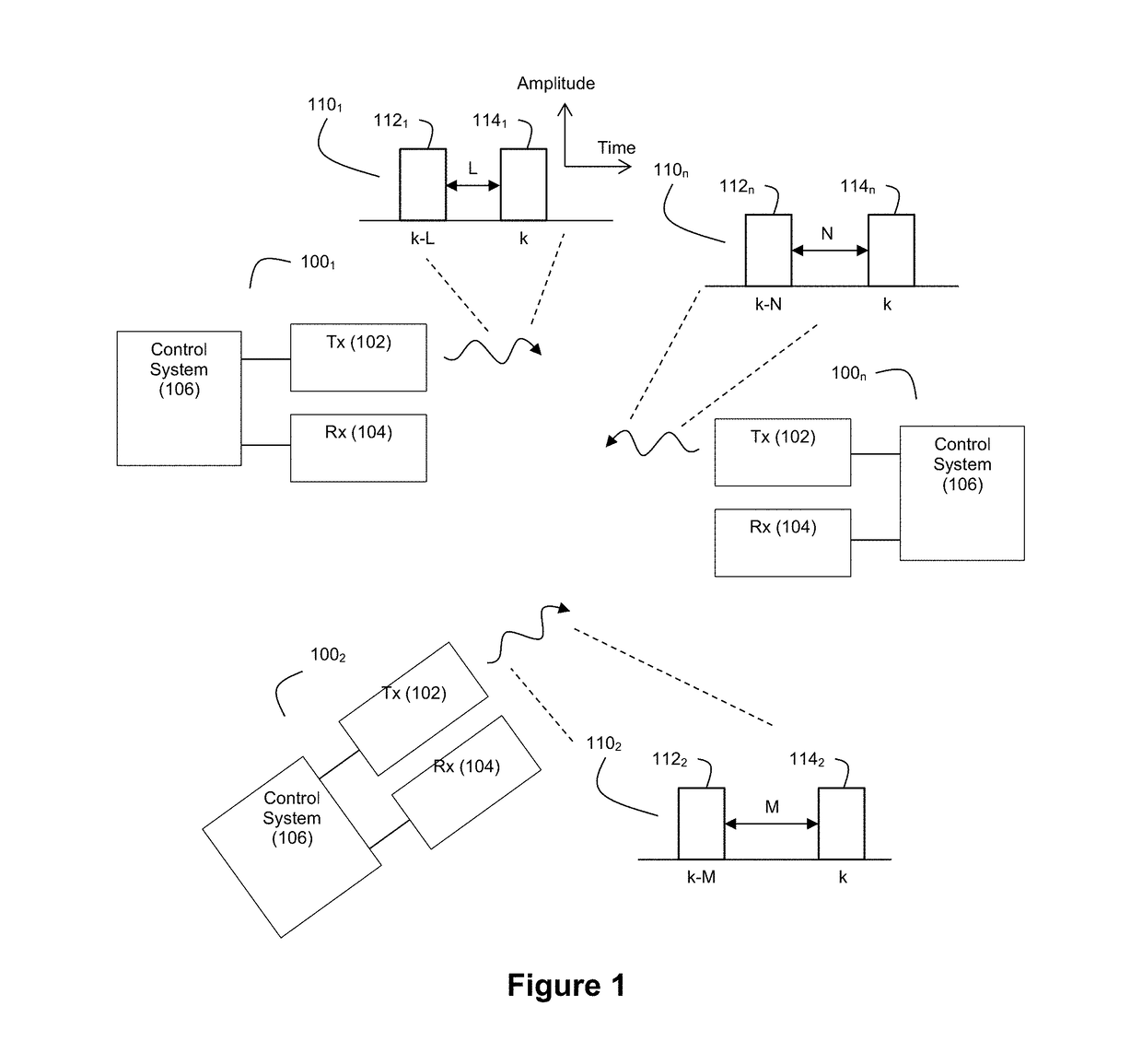

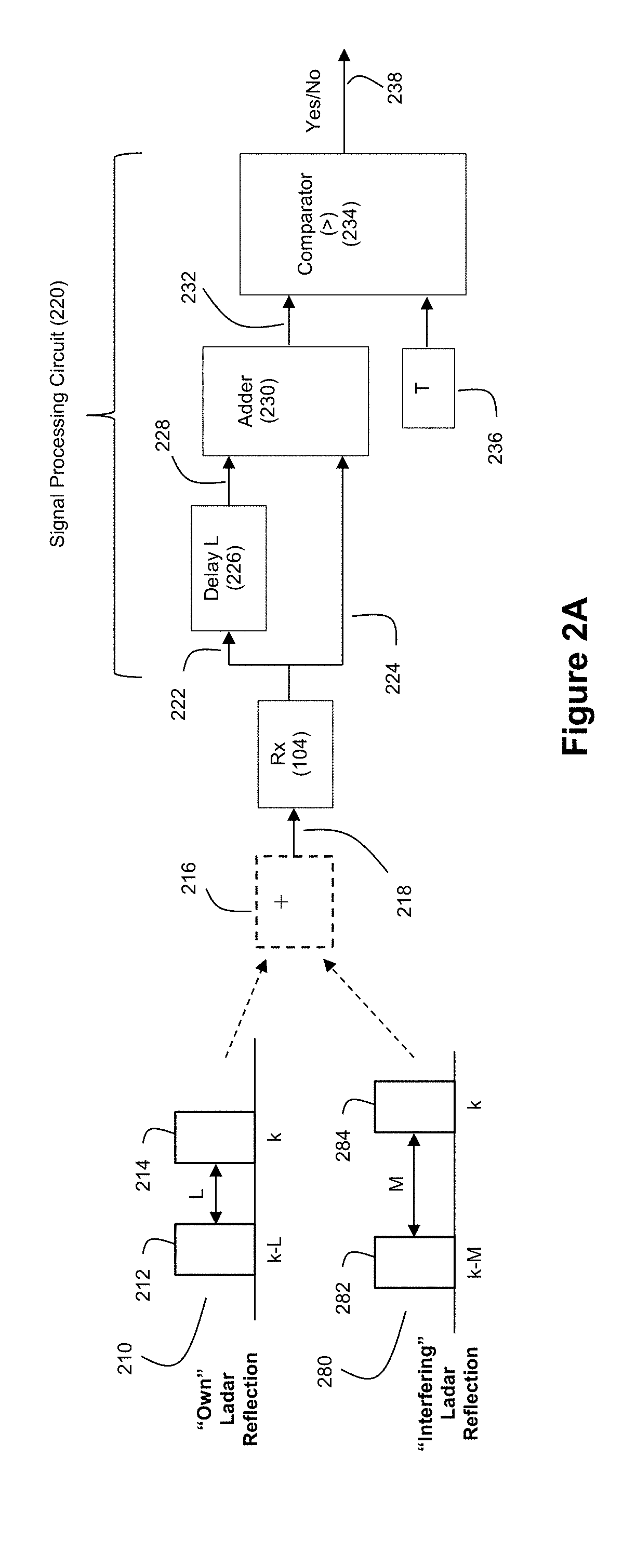

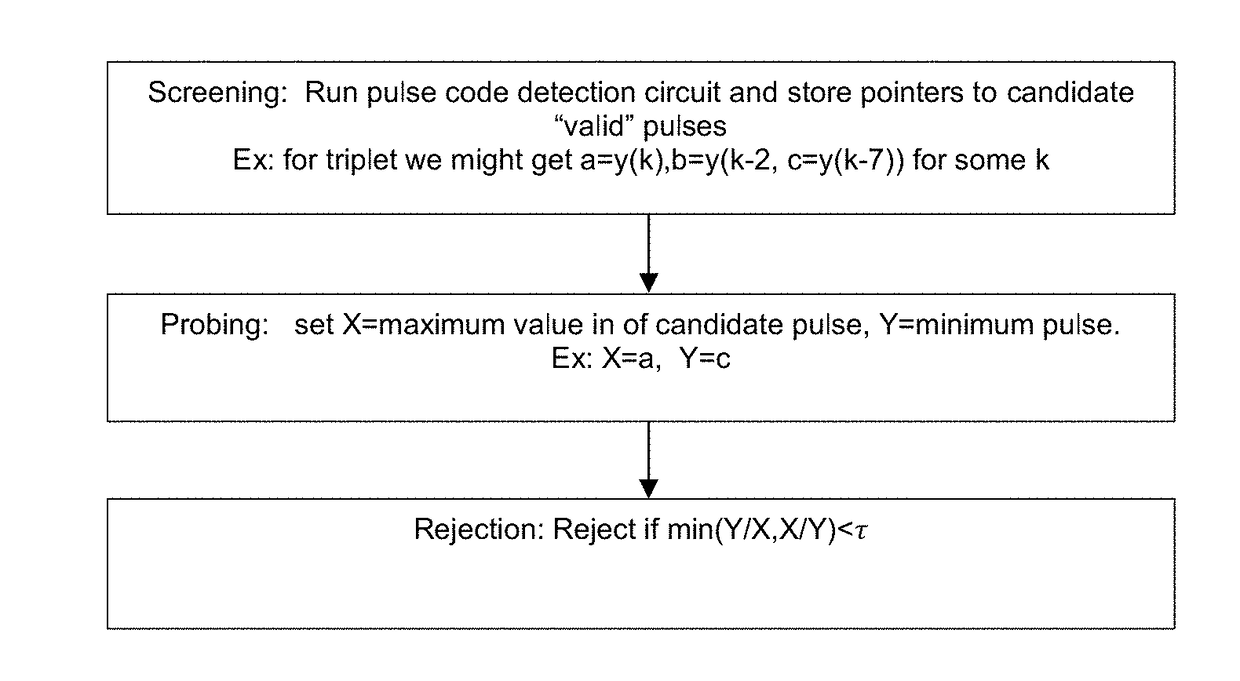

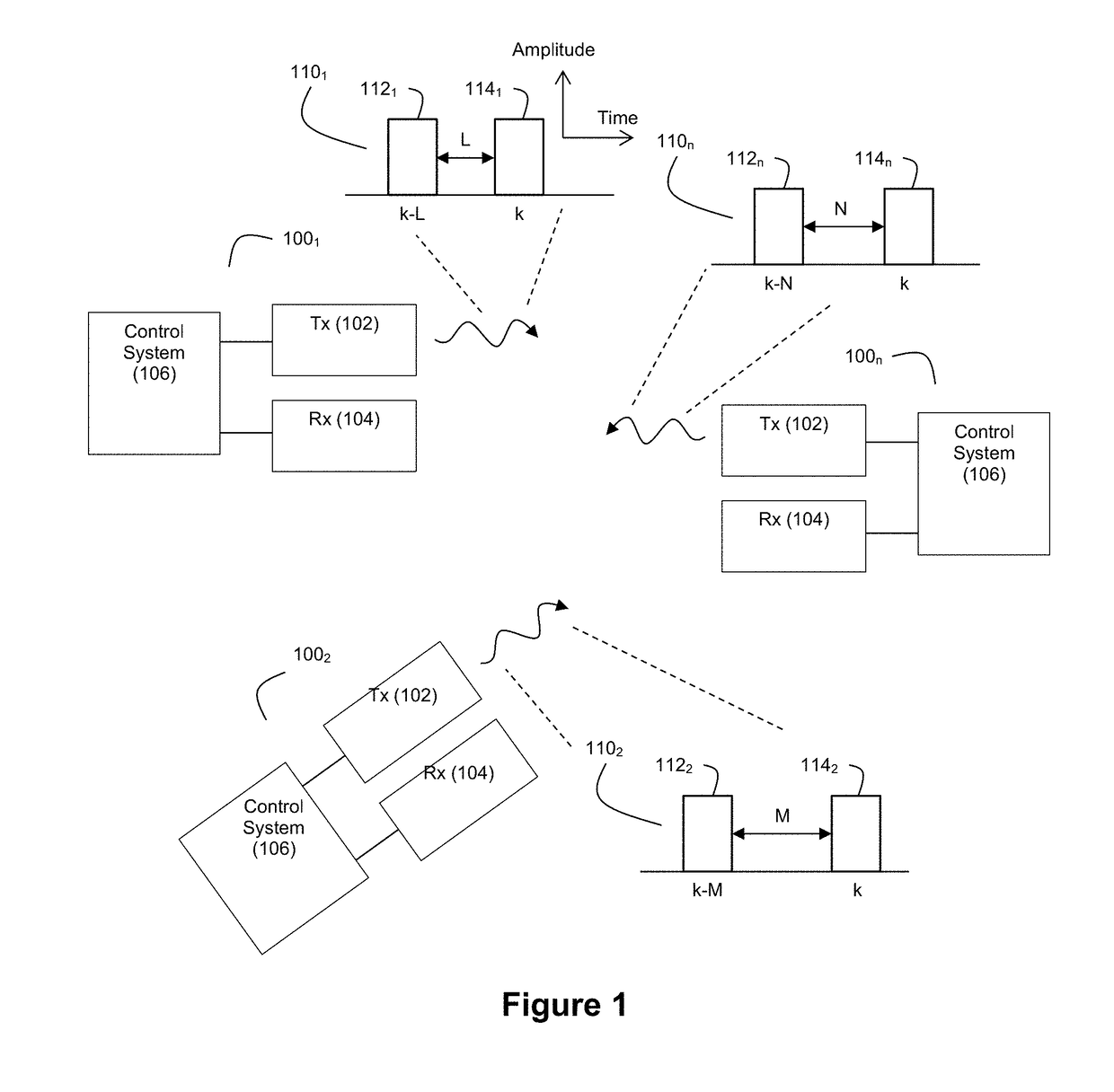

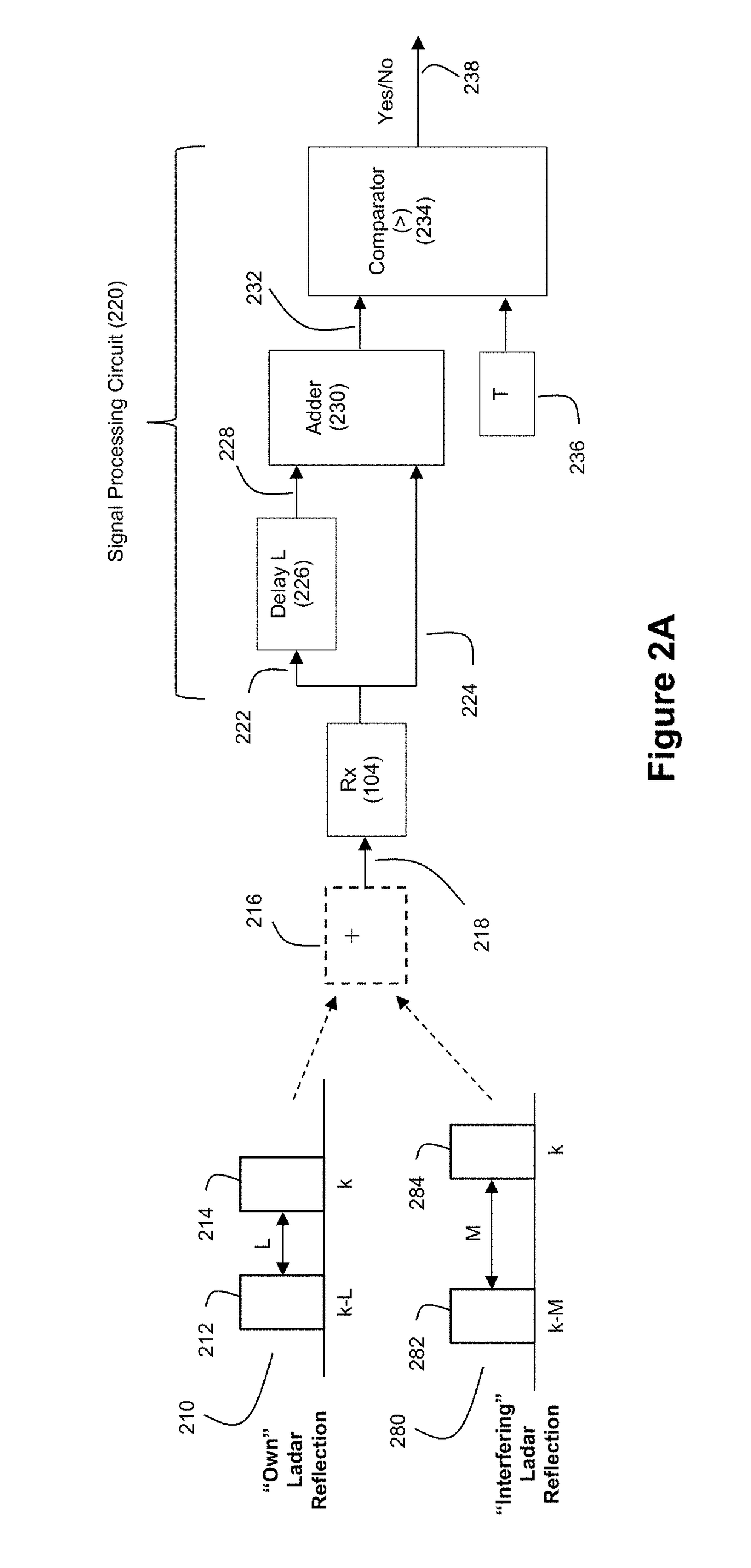

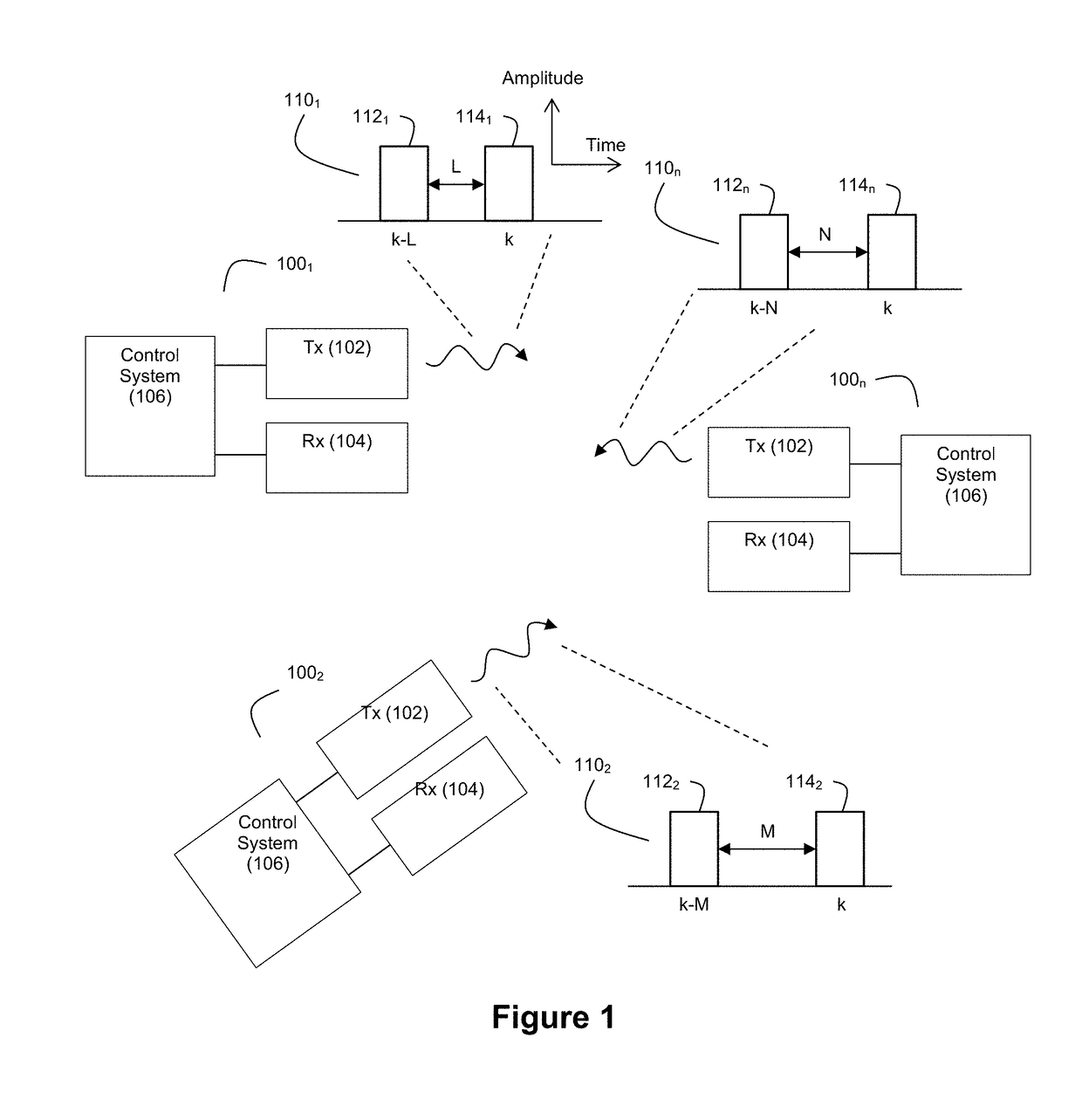

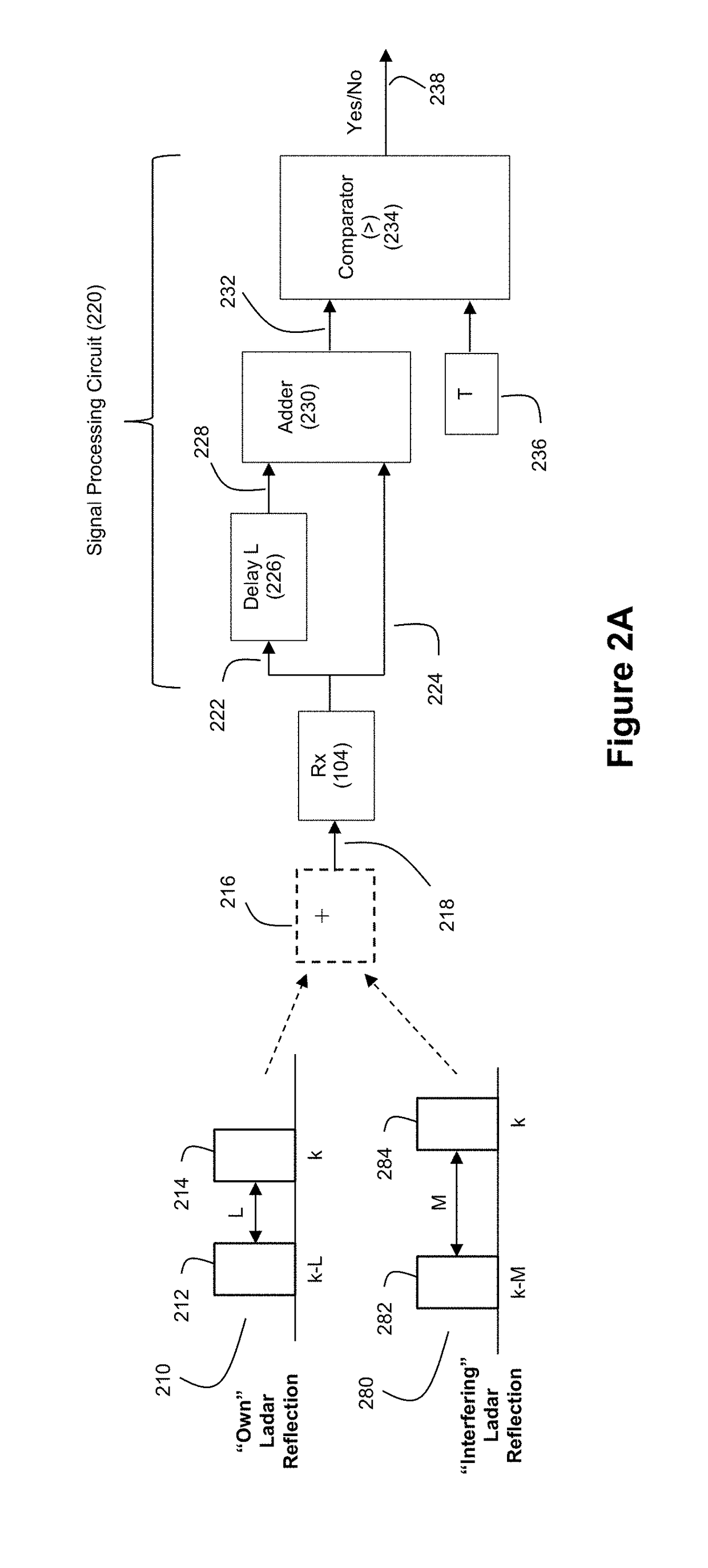

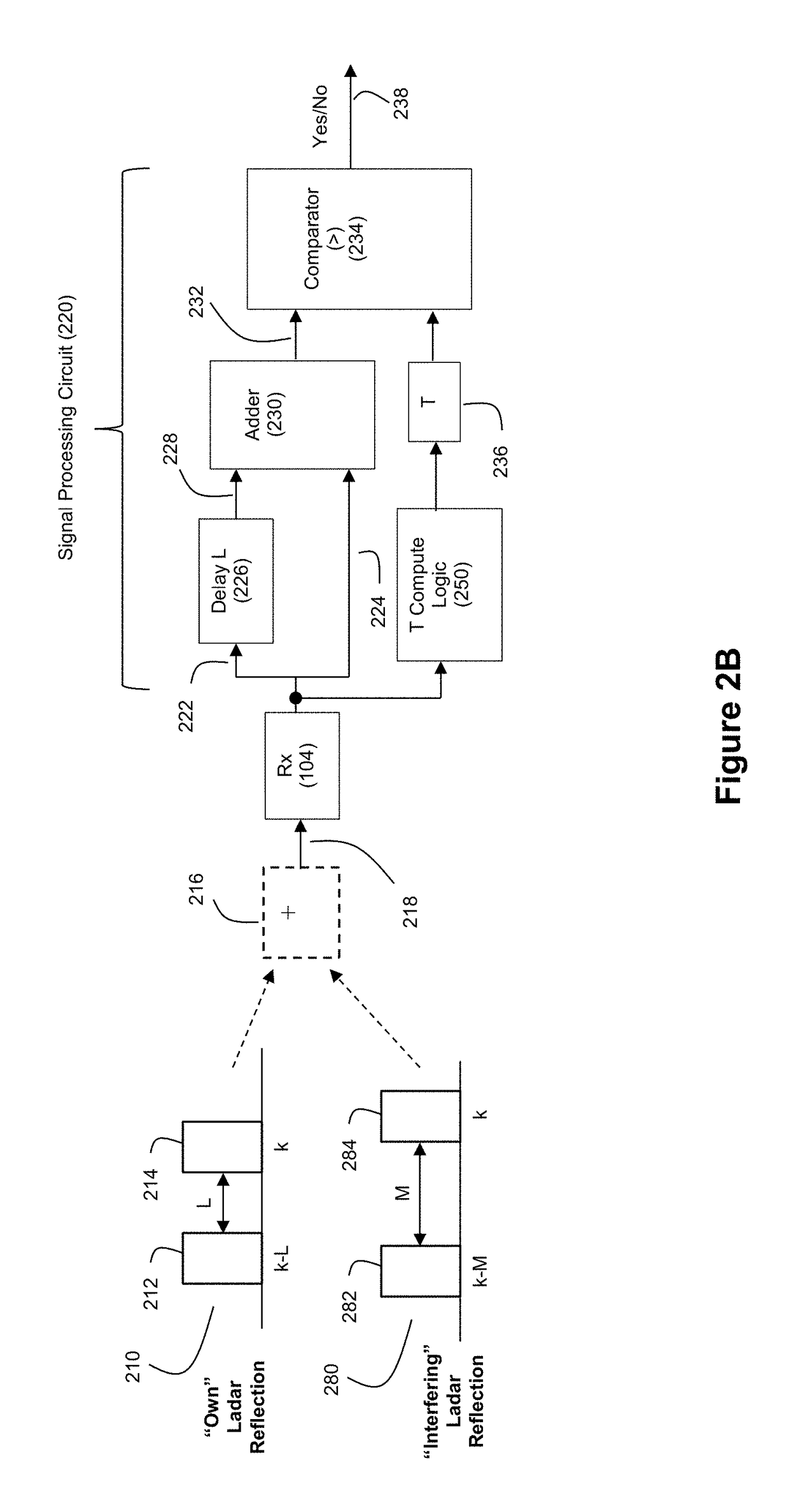

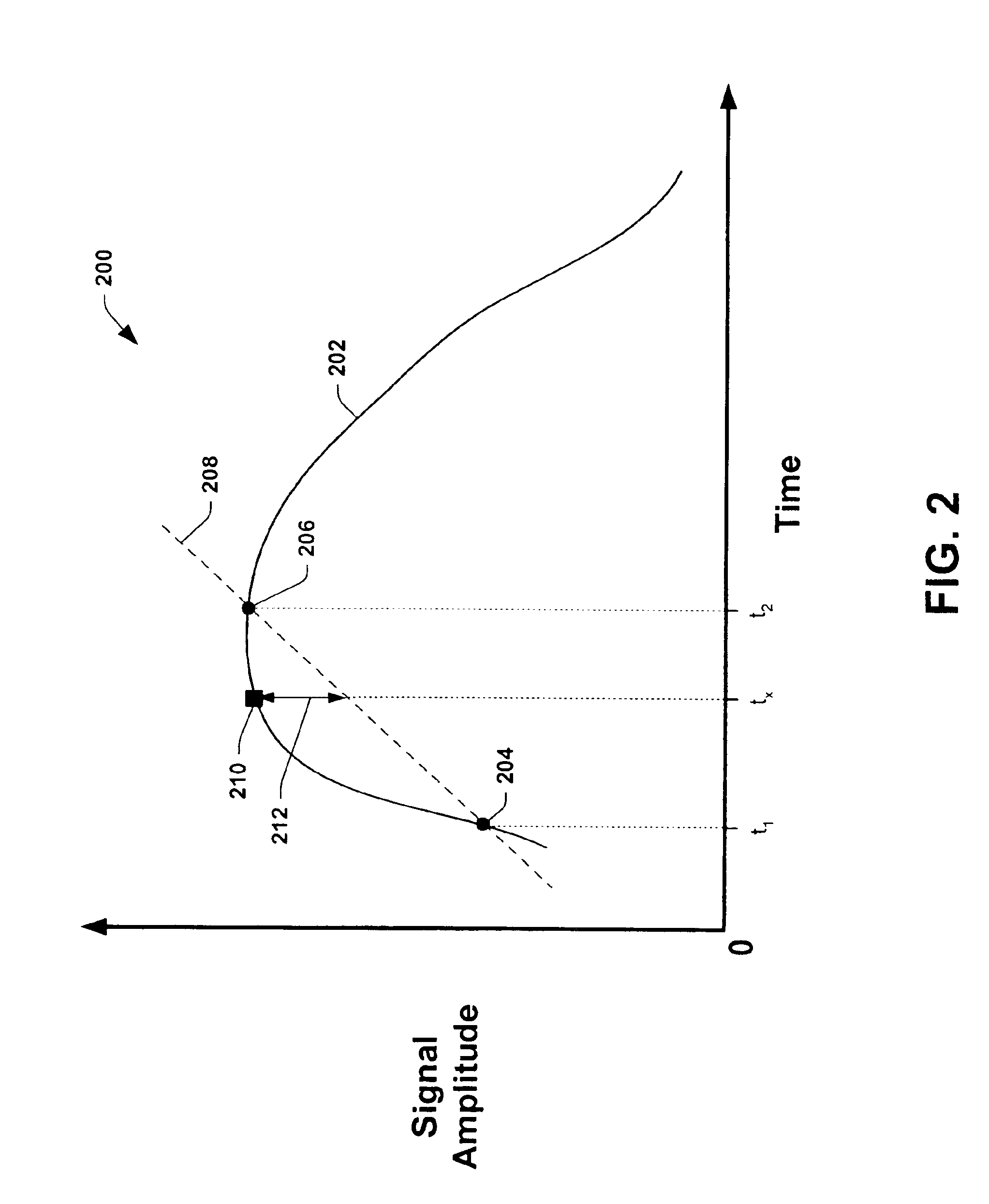

Disclosed herein are a number of example embodiments that employ controllable delays between successive ladar pulses in order to discriminate between “own” ladar pulse reflections and “interfering” ladar pulses reflections by a receiver. Example embodiments include designs where a sparse delay sum circuit is used at the receiver and where a funnel filter is used at the receiver. Also, disclosed are techniques for selecting codes to use for the controllable delays as well as techniques for identifying and tracking interfering ladar pulses and their corresponding delay codes. The use of a ladar system with pulse deconfliction is also disclosed as part of an optical data communication system.

Owner:AEYE INC

Method and System for Ladar Pulse Deconfliction Using Delay Code Selection

ActiveUS20180239000A1Short time intervalReduce the numberElectromagnetic wave reradiationRadio wave reradiation/reflectionRadar systemsCommunications system

Disclosed herein are a number of example embodiments that employ controllable delays between successive ladar pulses in order to discriminate between “own” ladar pulse reflections and “interfering” ladar pulses reflections by a receiver. Example embodiments include designs where a sparse delay sum circuit is used at the receiver and where a funnel filter is used at the receiver. Also, disclosed are techniques for selecting codes to use for the controllable delays as well as techniques for identifying and tracking interfering ladar pulses and their corresponding delay codes. The use of a ladar system with pulse deconfliction is also disclosed as part of an optical data communication system.

Owner:AEYE INC

Method and System for Ladar Pulse Deconfliction to Detect and Track Other Ladar Systems

ActiveUS20180239001A1Short time intervalReduce the numberElectromagnetic wave reradiationRadio wave reradiation/reflectionRadar systemsCommunications system

Disclosed herein are a number of example embodiments that employ controllable delays between successive ladar pulses in order to discriminate between “own” ladar pulse reflections and “interfering” ladar pulses reflections by a receiver. Example embodiments include designs where a sparse delay sum circuit is used at the receiver and where a funnel filter is used at the receiver. Also, disclosed are techniques for selecting codes to use for the controllable delays as well as techniques for identifying and tracking interfering ladar pulses and their corresponding delay codes. The use of a ladar system with pulse deconfliction is also disclosed as part of an optical data communication system.

Owner:AEYE INC

Method and System for Optical Data Communication via Scanning Ladar

ActiveUS20180239005A1Short time intervalReduce the numberElectromagnetic wave reradiationRadio wave reradiation/reflectionCommunications systemRadar systems

Disclosed herein are a number of example embodiments that employ controllable delays between successive ladar pulses in order to discriminate between “own” ladar pulse reflections and “interfering” ladar pulses reflections by a receiver. Example embodiments include designs where a sparse delay sum circuit is used at the receiver and where a funnel filter is used at the receiver. Also, disclosed are techniques for selecting codes to use for the controllable delays as well as techniques for identifying and tracking interfering ladar pulses and their corresponding delay codes. The use of a ladar system with pulse deconfliction is also disclosed as part of an optical data communication system.

Owner:AEYE INC

Ladar Pulse Deconfliction Method

ActiveUS20180239004A1Short time intervalReduce the numberElectromagnetic wave reradiationRadio wave reradiation/reflectionCommunications systemRadar systems

Disclosed herein are a number of example embodiments that employ controllable delays between successive ladar pulses in order to discriminate between “own” ladar pulse reflections and “interfering” ladar pulses reflections by a receiver. Example embodiments include designs where a sparse delay sum circuit is used at the receiver and where a funnel filter is used at the receiver. Also, disclosed are techniques for selecting codes to use for the controllable delays as well as techniques for identifying and tracking interfering ladar pulses and their corresponding delay codes. The use of a ladar system with pulse deconfliction is also disclosed as part of an optical data communication system.

Owner:AEYE INC

Method and system for ladar pulse deconfliction using delay code selection

ActiveUS10185028B2Short time intervalReduce the numberOptical rangefindersElectromagnetic transmissionCommunications systemRadar

Disclosed herein are a number of example embodiments that employ controllable delays between successive ladar pulses in order to discriminate between “own” ladar pulse reflections and “interfering” ladar pulses reflections by a receiver. Example embodiments include designs where a sparse delay sum circuit is used at the receiver and where a funnel filter is used at the receiver. Also, disclosed are techniques for selecting codes to use for the controllable delays as well as techniques for identifying and tracking interfering ladar pulses and their corresponding delay codes. The use of a ladar system with pulse deconfliction is also disclosed as part of an optical data communication system.

Owner:AEYE INC

Transactionally Deterministic High Speed Financial Exchange Having Improved, Efficiency, Communication, Customization, Performance, Access, Trading Opportunities, Credit Controls, and Fault Tolerance

The disclosed embodiments relate to implementation of a trading system, which may also be referred to as a trading system architecture, having improved performance which further assures transactional determinism under increasing processing transaction loads while providing improved trading opportunities, fault tolerance, low latency processing, high volume capacity, risk mitigation and market protections with minimal impact, as well as improved and equitable access to information and opportunities.

Owner:CHICAGO MERCANTILE EXCHANGE

Transactionally Deterministic High Speed Financial Exchange Having Improved, Efficiency, Communication, Customization, Performance, Access, Trading Opportunities, Credit Controls, and Fault Tolerance

The disclosed embodiments relate to implementation of a trading system, which may also be referred to as a trading system architecture, having improved performance which further assures transactional determinism under increasing processing transaction loads while providing improved trading opportunities, fault tolerance, low latency processing, high volume capacity, risk mitigation and market protections with minimal impact, as well as improved and equitable access to information and opportunities.

Owner:CHICAGO MERCANTILE EXCHANGE

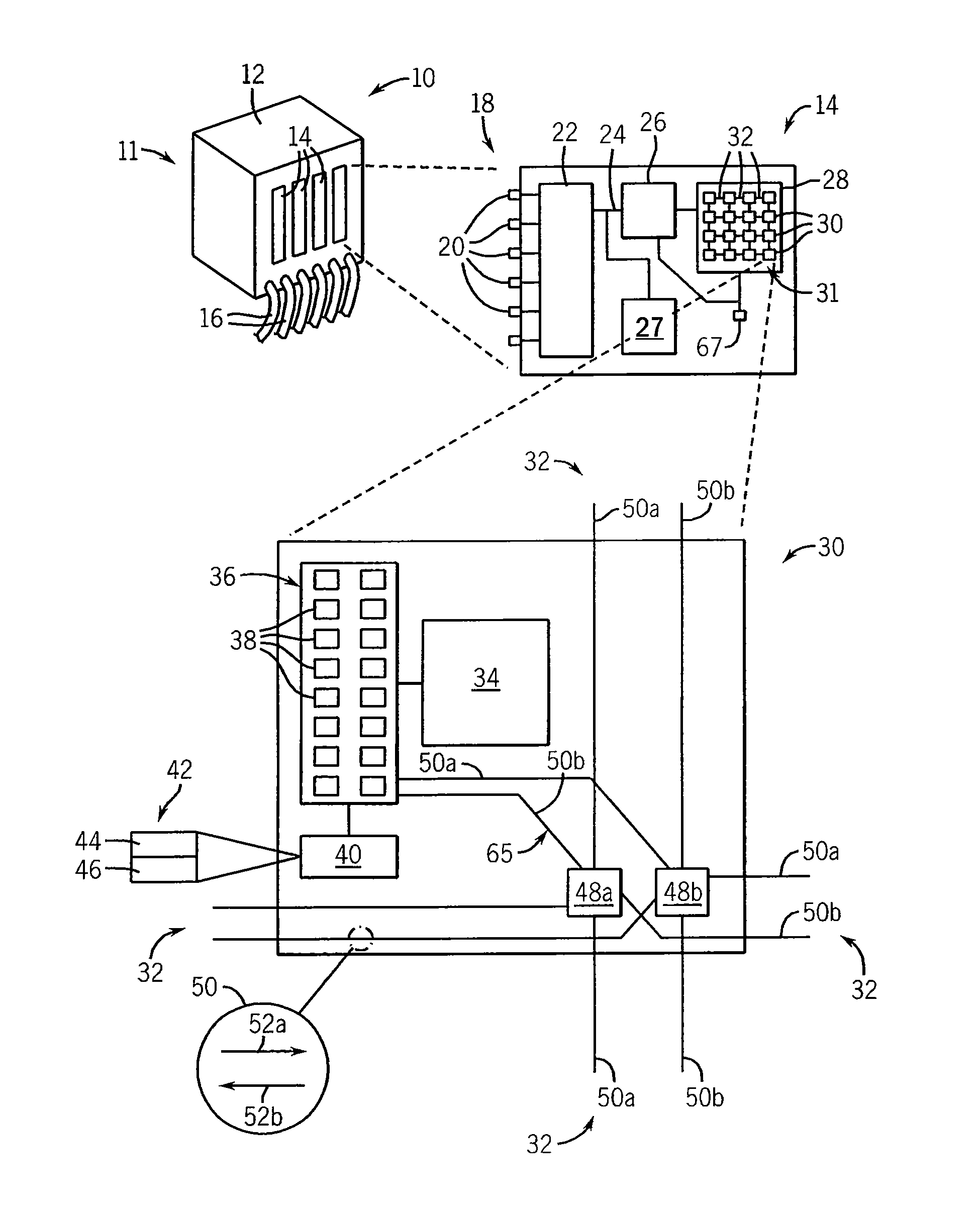

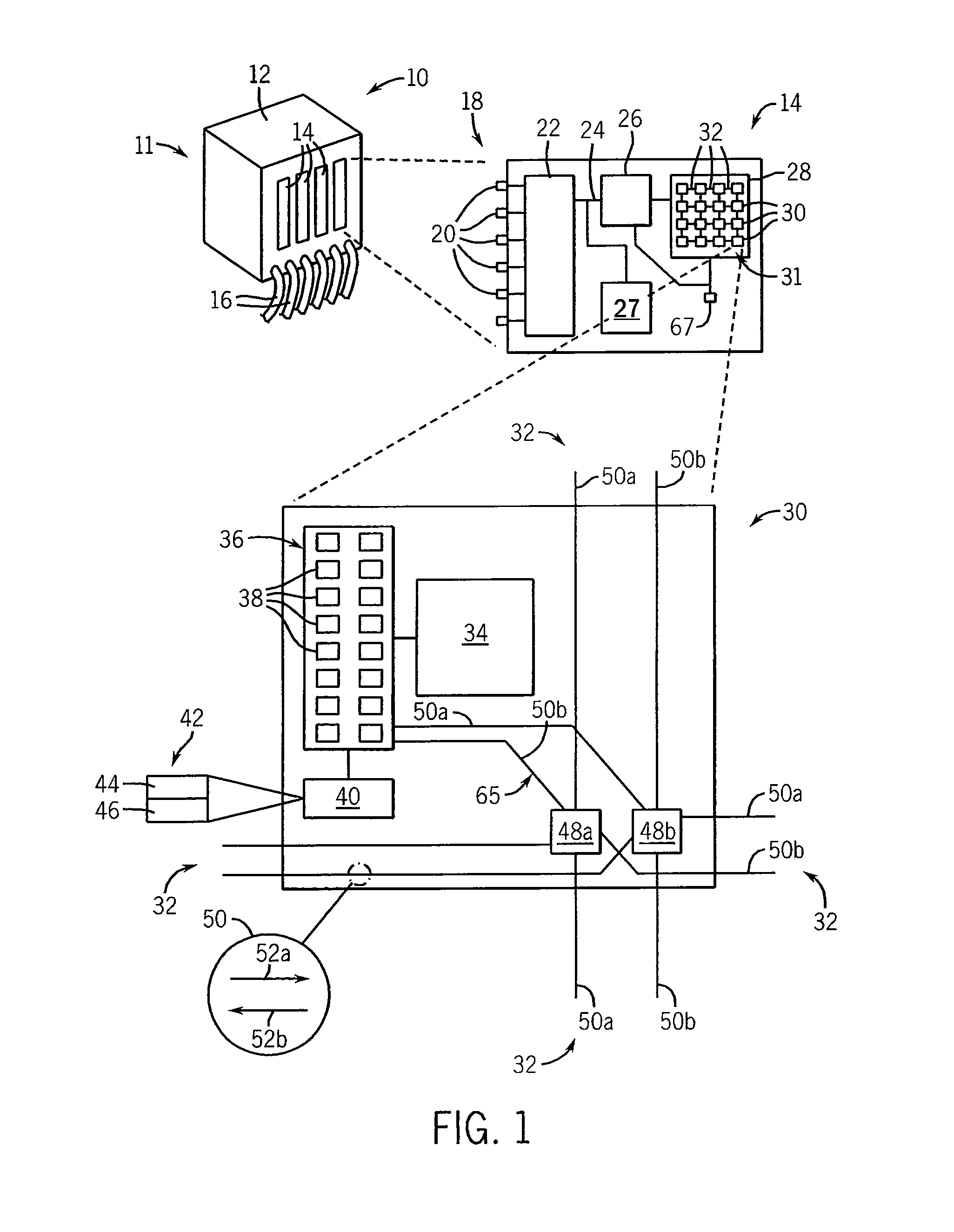

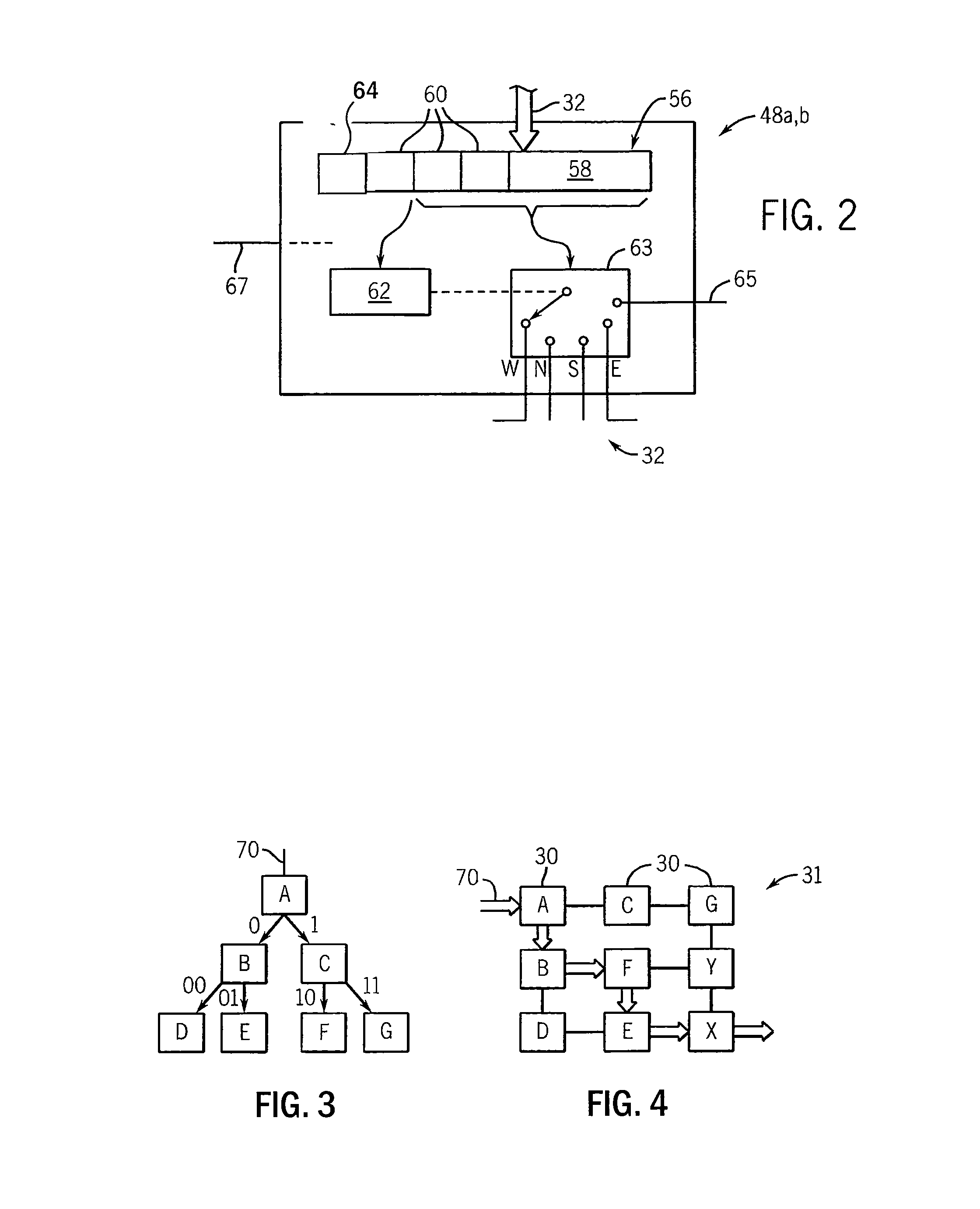

Lookup Engine with Reconfigurable Low Latency Computational Tiles

ActiveUS20140044135A1Lower latencyIncrease the number ofWide area networksMultiway switchingGate array

An architecture for a specialized electronic computer for high-speed data lookup employs a set of tiles each with independent logic elements lookup memory portions. The tiles may each comprise gate-array-like functional units that may be wired together by a multi-way switch for extremely low latency.

Owner:WISCONSIN ALUMNI RES FOUND

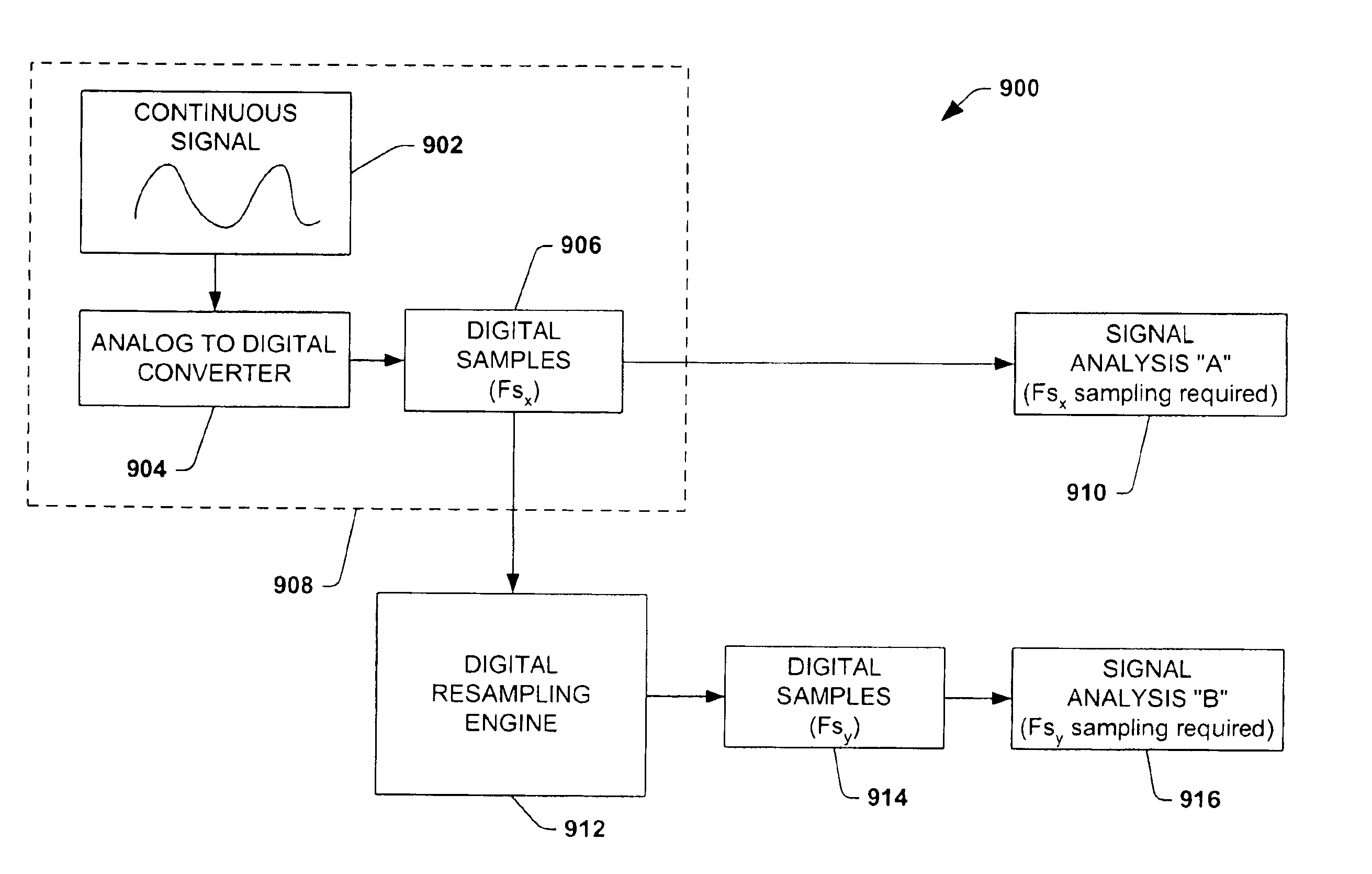

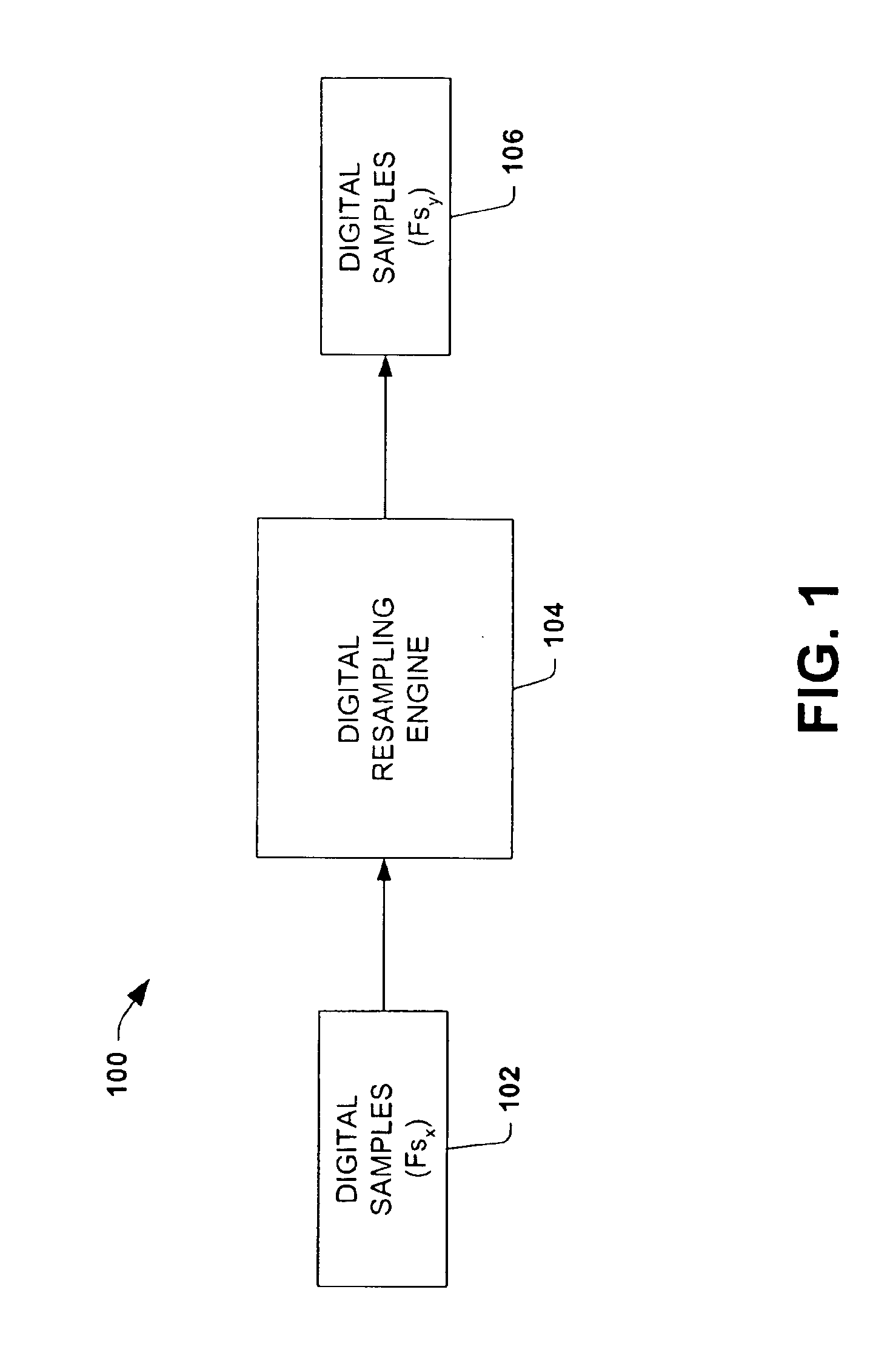

Method, apparatus and system for digital data resampling utilizing fourier series based interpolation

InactiveUS6915225B2Facilitates inherent valueResampled fasterSpectral/fourier analysisDigital technique networkDigital dataSeries expansion

The present invention provides a methodology, apparatus and system for resampling digital data utilizing a Fourier series based interpolation engine 104. A quick means to up-sample or down-sample data is provided without requiring computationally intensive processing. This is accomplished by utilizing low order coefficients of terms of a complete Fourier series expansion for a continuous signal. The summation of the expansion is limited to input samples immediately adjacent in time to the desired output. Generally speaking, the output is normally required to be a constant sampling rate, therefore, the input and output rates are related by an integer ratio. This ratio can be greater or smaller than one, providing up-sampling or down-sampling as appropriate. By employing the present invention, a DSP engine can be constructed that is adjustable to any ratio of sampling rates in a computationally efficient manner with low RMS error while preserving convolution through the resampling process.

Owner:NORTHROP GRUMMAN SYST CORP

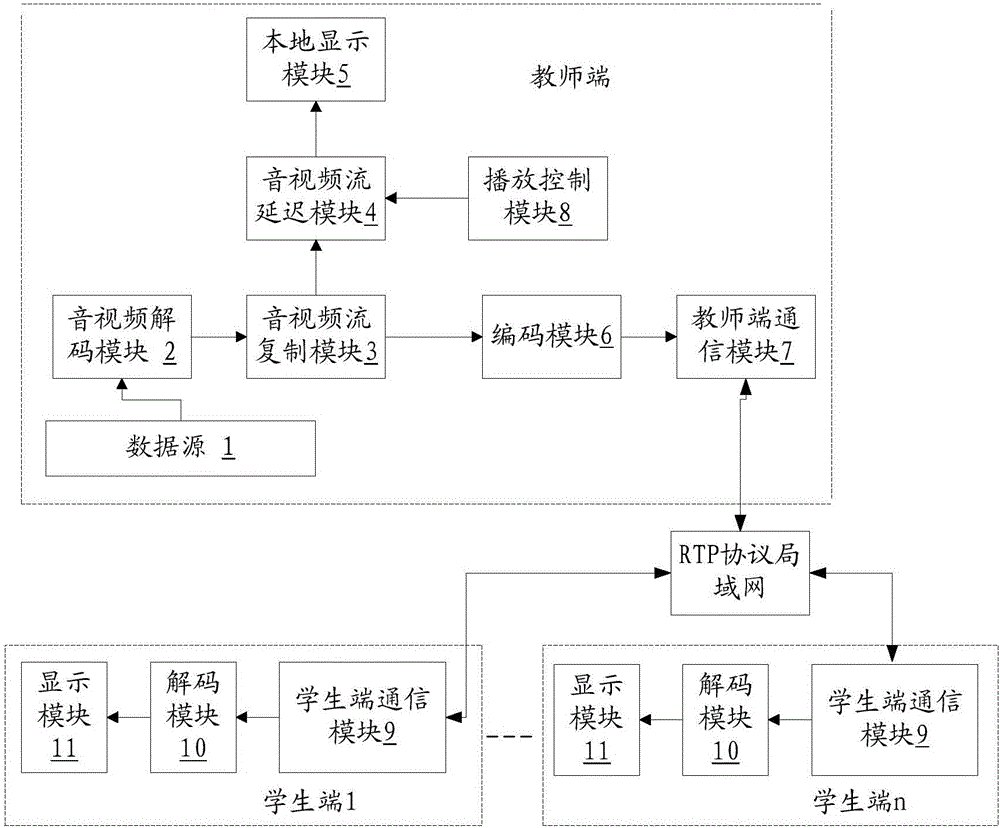

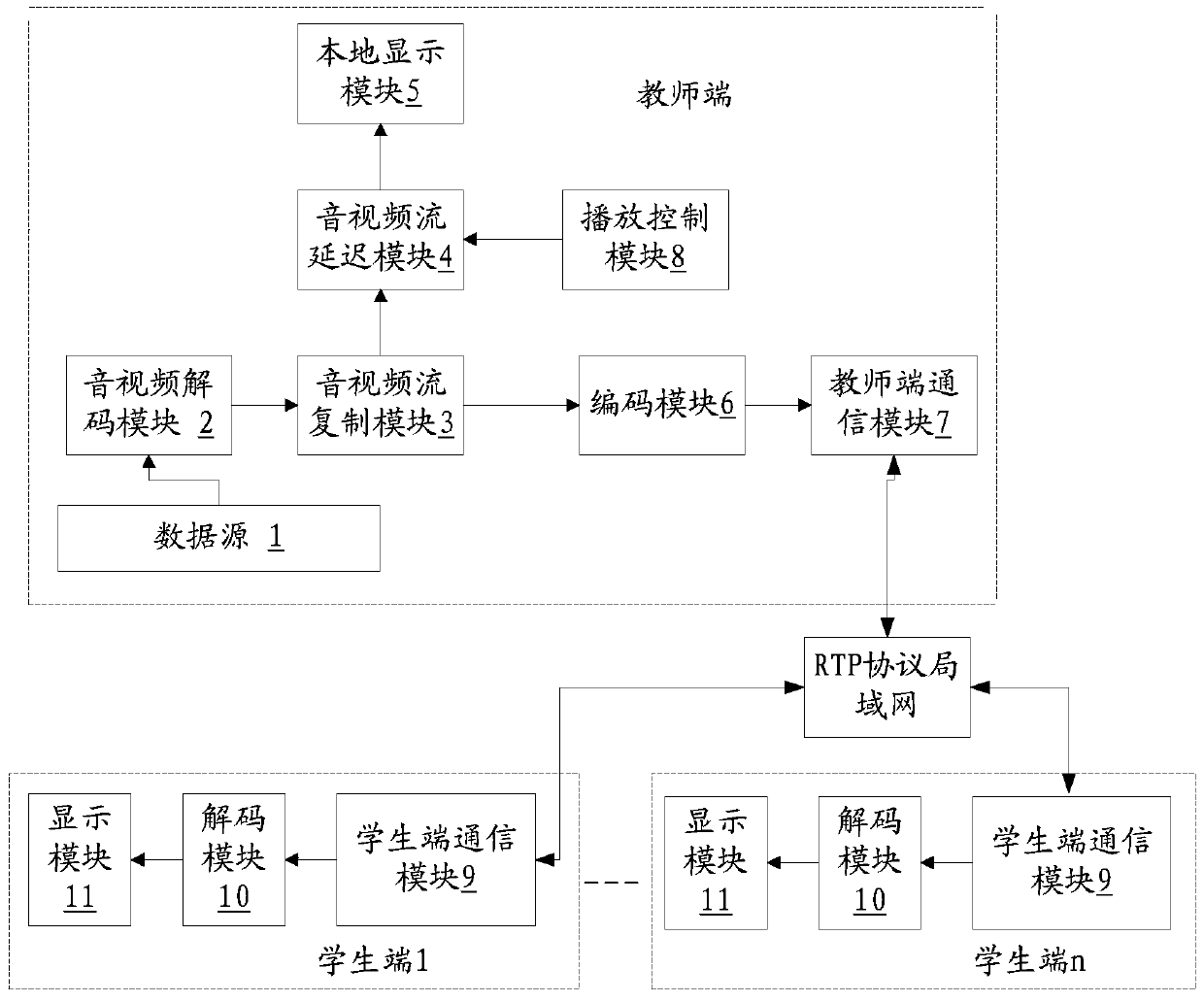

Method for realizing network cinema fluent playing based on cloud classroom scene

ActiveCN106231352AReduce trafficOptimize codec parametersSelective content distributionElectrical appliancesSynchronous controlOpen source

The invention provides a method for realizing network cinema fluent playing based on a cloud classroom scene. The system according to the method comprises at least one teacher side and multiple student sides. The teacher side uses a standard RTP protocol and broadcasts audio and video streams to the student sides in a multicast manner by using the multicast function of the router in a local area network so as to reduce network traffic. The teacher side is customized based on a VLC open source player and comprises a customized player interface and optimized coding and decoding parameters, and the standard H264 stream is used for coding of the teacher side. The video streams to be played are decoded on the student sides by using hardware, and audios and videos are added in the playing process to perform synchronous control playing. The problem of low fluency in playing 1080P high-definition videos of the network cinema under the cloud classroom can be solved so that fluent playing of the student sides can be realized.

Owner:FUJIAN CENTM INFORMATION

Transactionally deterministic high speed financial exchange having improved, efficiency, communication, customization, performance, access, trading opportunities, credit controls, and fault tolerance

The disclosed embodiments relate to implementation of a trading system, which may also be referred to as a trading system architecture, having improved performance which further assures transactional determinism under increasing processing transaction loads while providing improved trading opportunities, fault tolerance, low latency processing, high volume capacity, risk mitigation and market protections with minimal impact, as well as improved and equitable access to information and opportunities.

Owner:CHICAGO MERCANTILE EXCHANGE INC

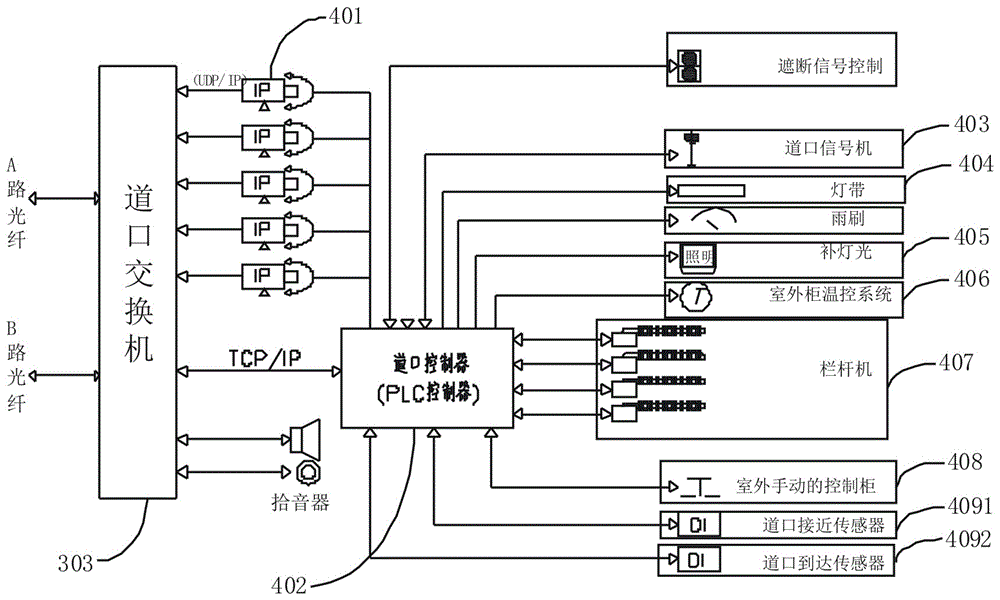

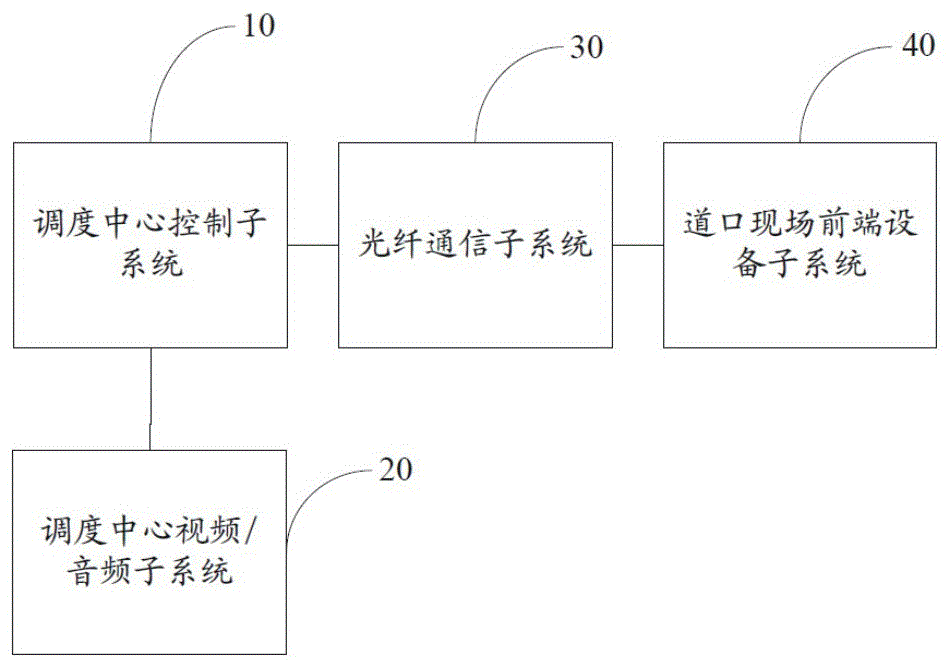

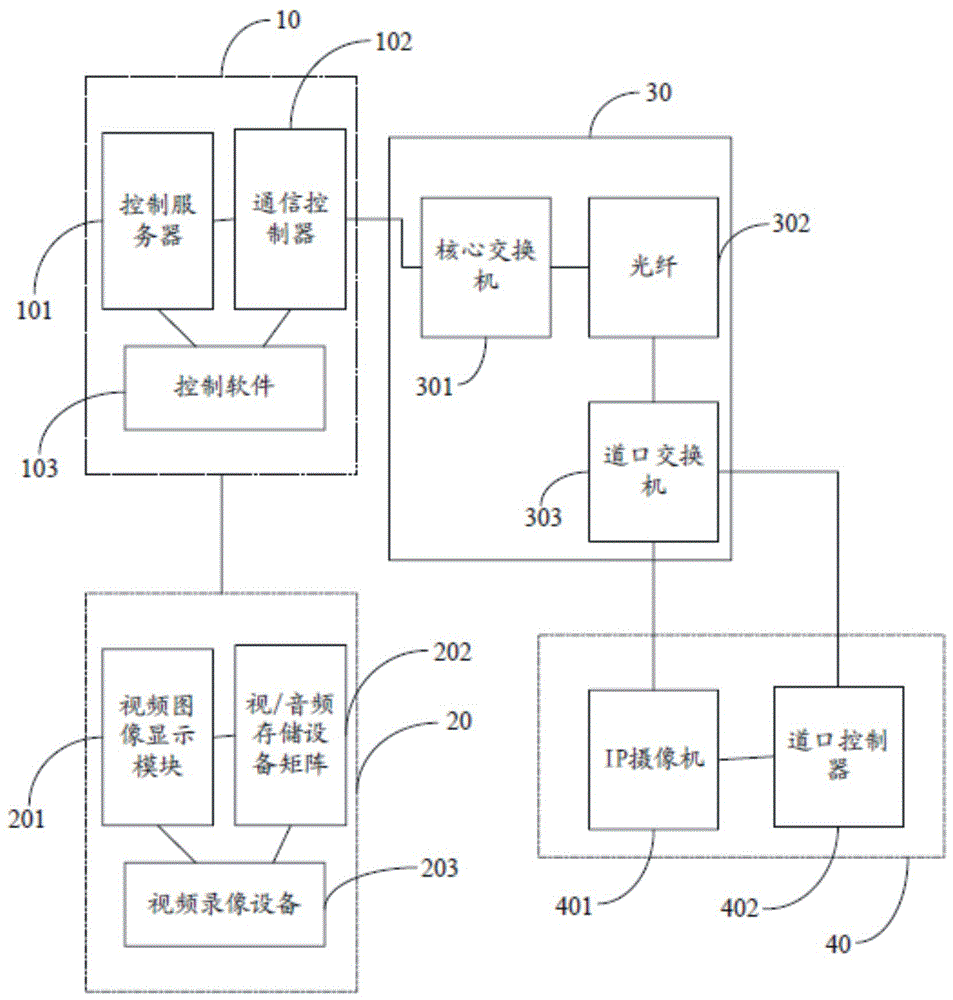

Railway crossing remote centralized control and intelligent early warning integrated system

InactiveCN106274997AImprove efficiencyEasy to operateAutomatic systemsRoad traffic warning meansLevel crossingMonitoring and control

The invention discloses a railway crossing remote centralized control and intelligent early warning integrated system. The system comprises a dispatching center control subsystem, a dispatching center video / audio subsystem, a crossing field front-end device subsystem and an optical fiber communication subsystem. The dispatching center video / audio subsystem is connected with the dispatching center control subsystem. The crossing field front-end device subsystem is connected with the dispatching center control subsystem through the optical fiber communication subsystem. The dispatching center control subsystem comprises a control server and a communication controller, achieves monitoring and control over all devices of the other three subsystems and completes remote control command for dispatching operators. The dispatching center video / audio subsystem comprises a video image display module and a video / audio storage device matrix. Remote videos, remotes audios and remote control are centralized and integrated into the system, the efficiency is improved, the operation is facilitated, and the system is safer and more reliable.

Owner:淄博矿业集团有限责任公司济宁北矿区铁路运销处

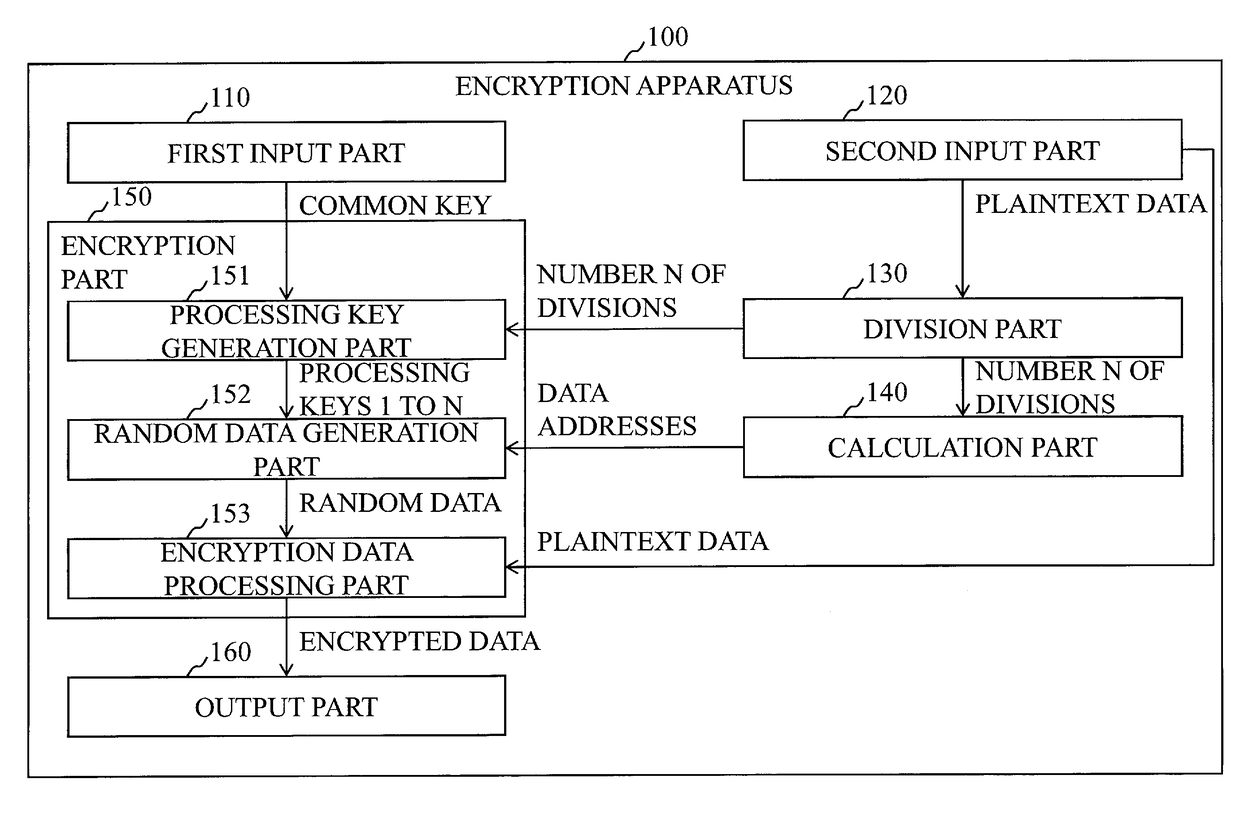

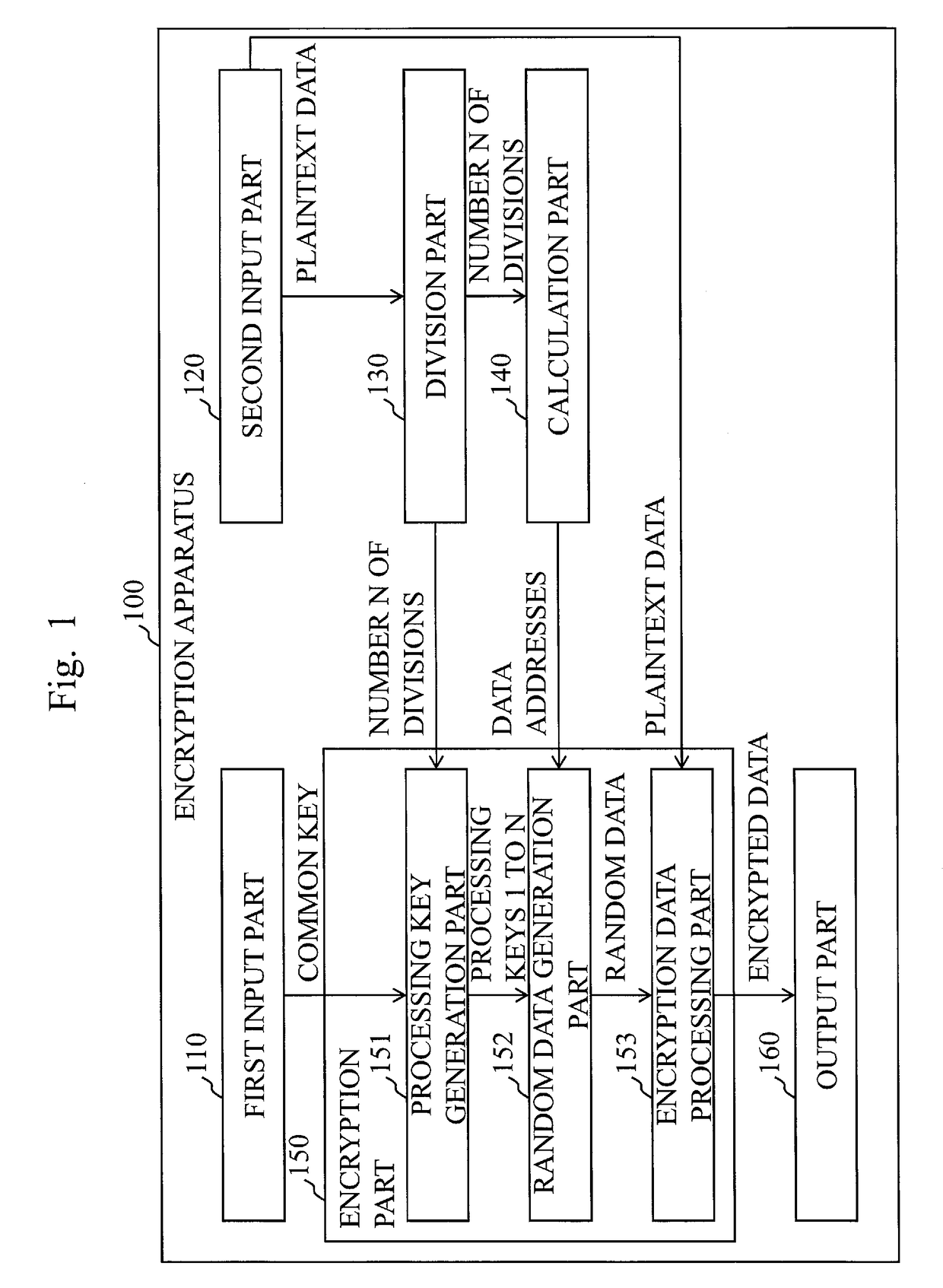

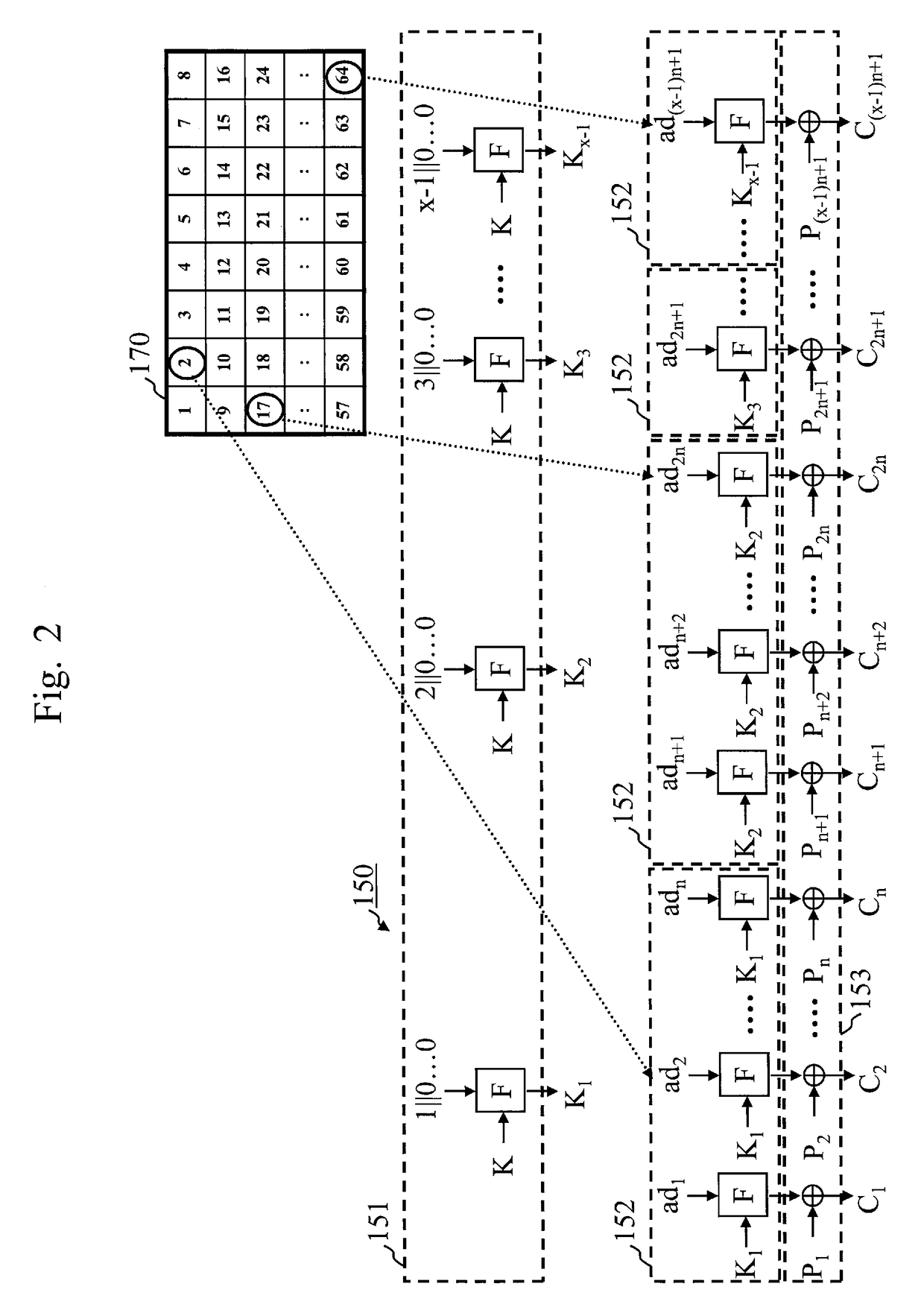

Encryption apparatus, storage system, decryption apparatus, encryption method, decryption method, and computer readable medium

InactiveUS20170126399A1Low latency processingHigh latencyKey distribution for secure communicationEncryption apparatus with shift registers/memoriesCommon keyData input

In an encryption apparatus, a division part determines as a unit of processing, the number of blocks to be encrypted using the same key, and divides plaintext data input from a second input part by the unit of processing. An encryption part generates from a common key input from a first input part, processing keys 1 to N which are different from each other and the number of which is the same as the number N of divisions of the plaintext data at the division part, and generates encrypted data by encrypting for each unit of processing determined by the division part, individual blocks of the plaintext data input from the second input part, by means of a block cipher F using the same generated processing key I.

Owner:MITSUBISHI ELECTRIC CORP

Transactionally deterministic high speed financial exchange having improved, efficiency, communication, customization, performance, access, trading opportunities, credit controls, and fault tolerance

Owner:CHICAGO MERCANTILE EXCHANGE INC

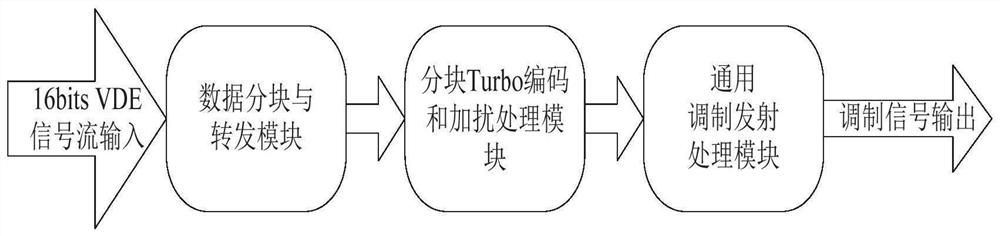

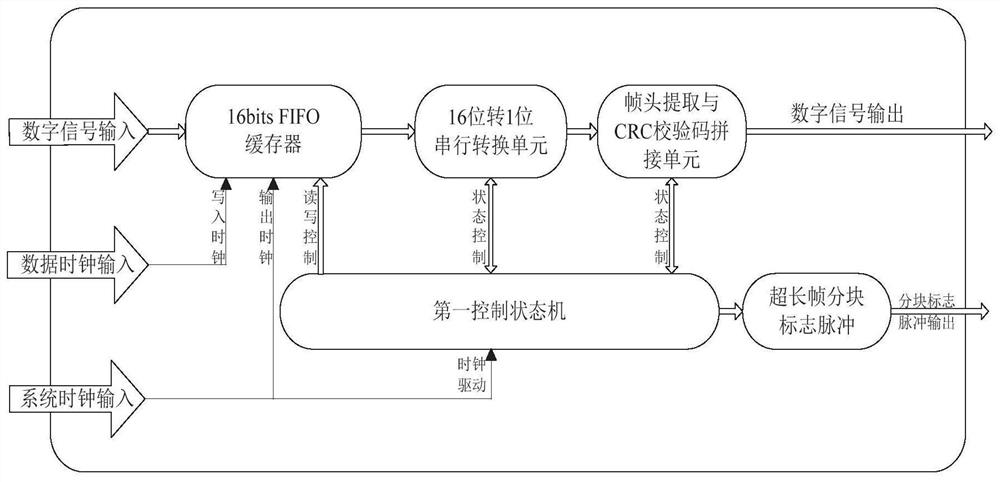

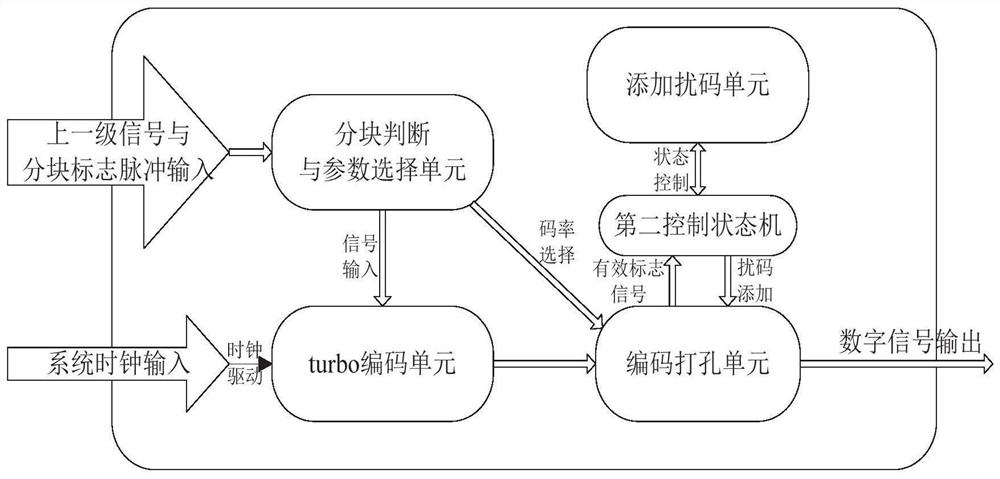

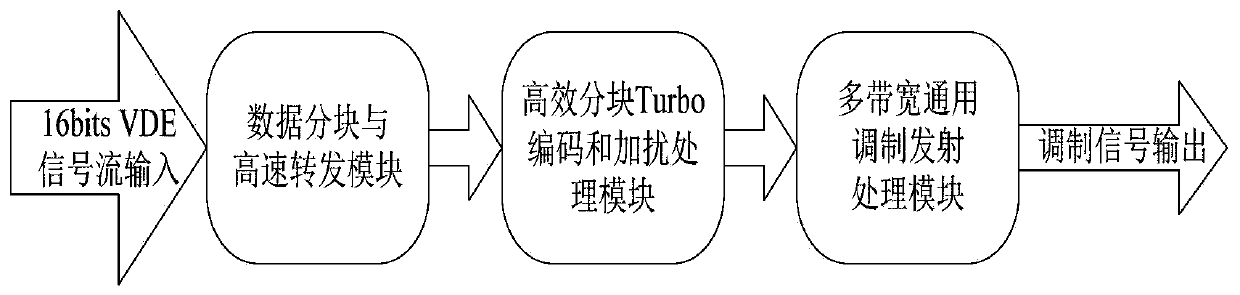

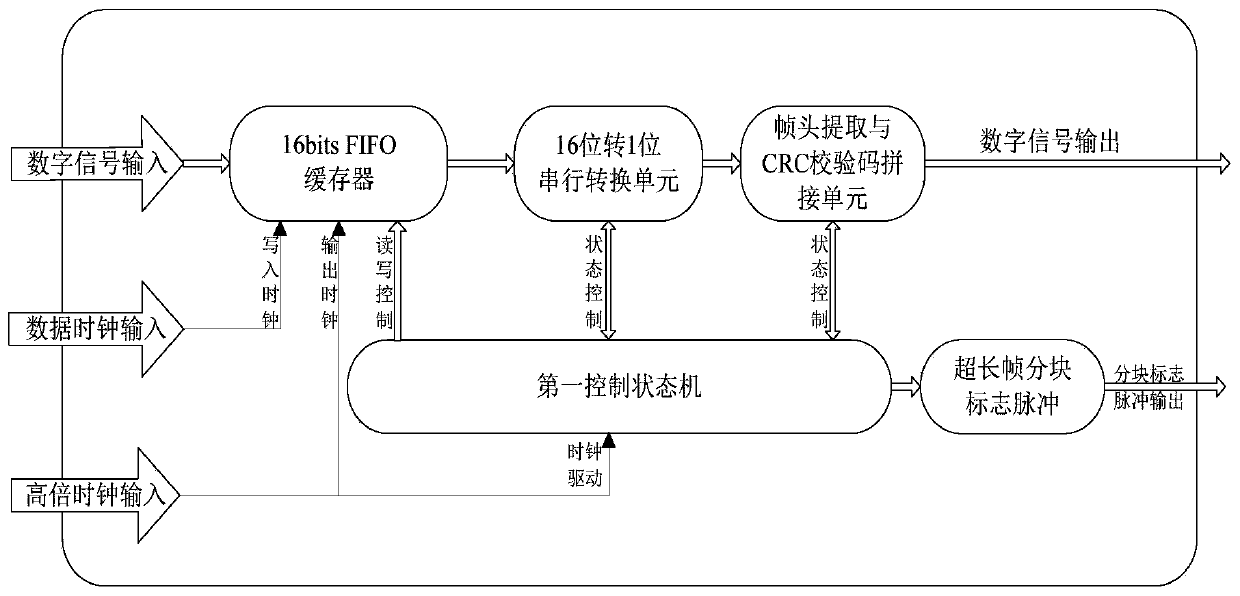

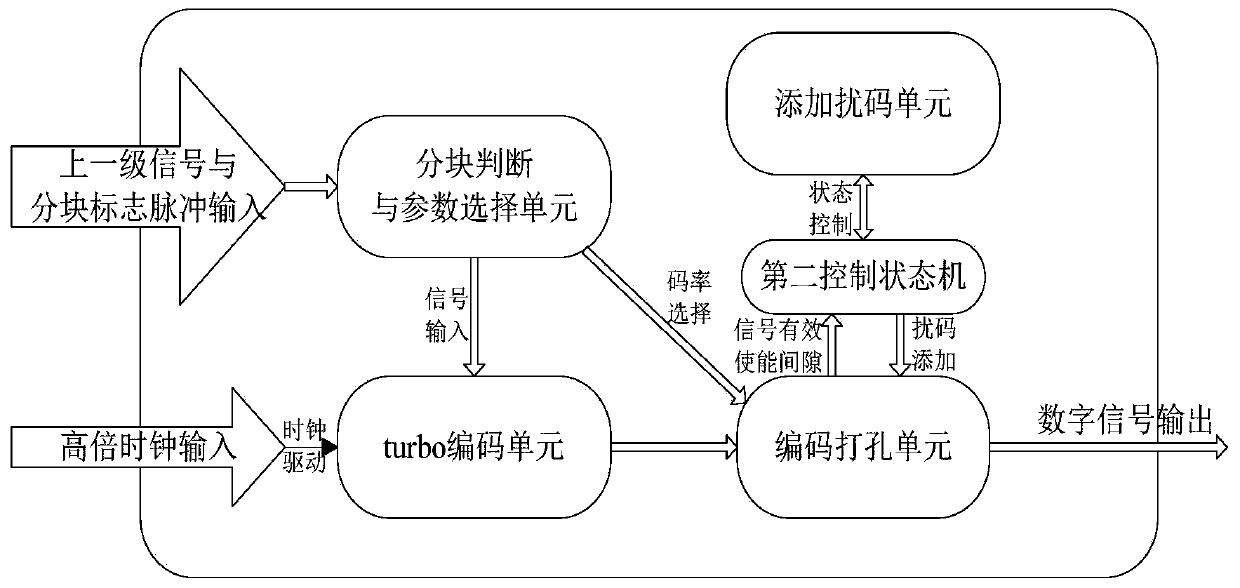

Low-delay VDE satellite-borne downlink digital signal processing system based on FPGA

ActiveCN112532306AReduce sending delayImprove digital signal processing capabilitiesRadio transmissionChannel coding adaptationDigital signal processingEngineering

The invention provides a low-delay VDE satellite-borne downlink digital signal processing system based on an FPGA, and the system is characterized in that the system comprises a data partitioning andforwarding module, a partitioning Turbo coding and scrambling processing module, and a general modulation transmission processing module; and according to the low-delay digital signal processing method and module design based on the VDE communication protocol mechanism, VDE modulation signal sending delay is greatly reduced, FPGA resource occupation is reduced, and the low-delay digital signal processing method and module design can be applied to a VDE satellite-borne downlink digital signal processing scene.

Owner:SHANGHAI SPACEFLIGHT ELECTRONICS & COMM EQUIP RES INST

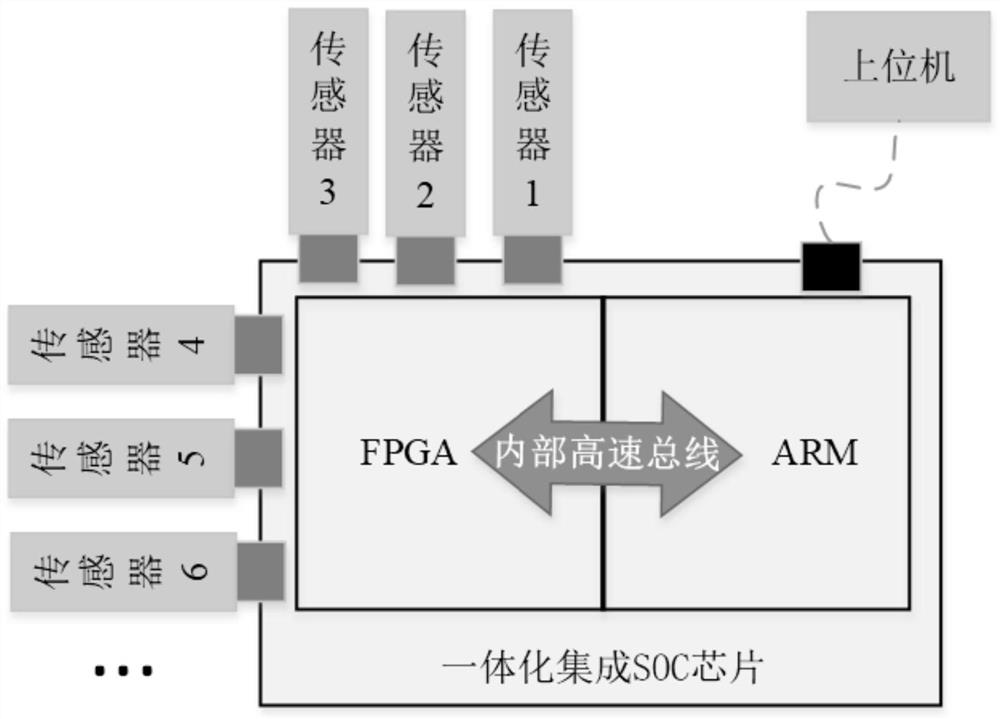

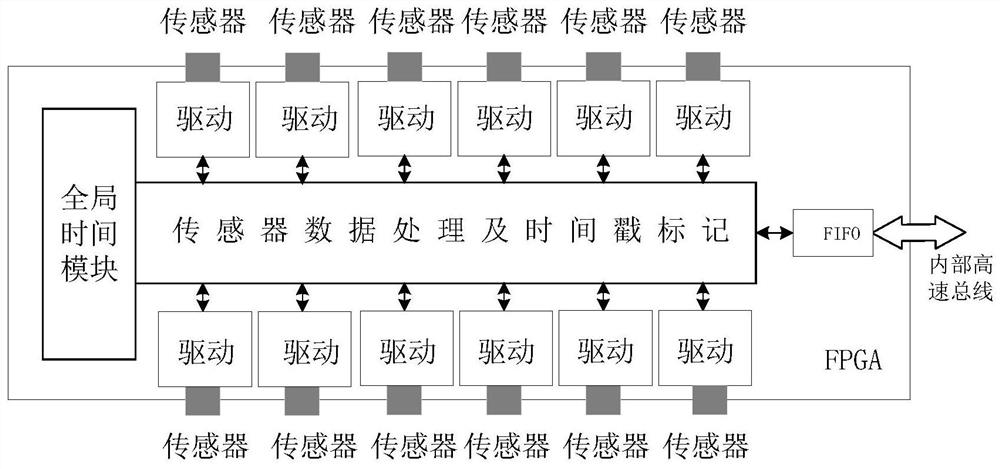

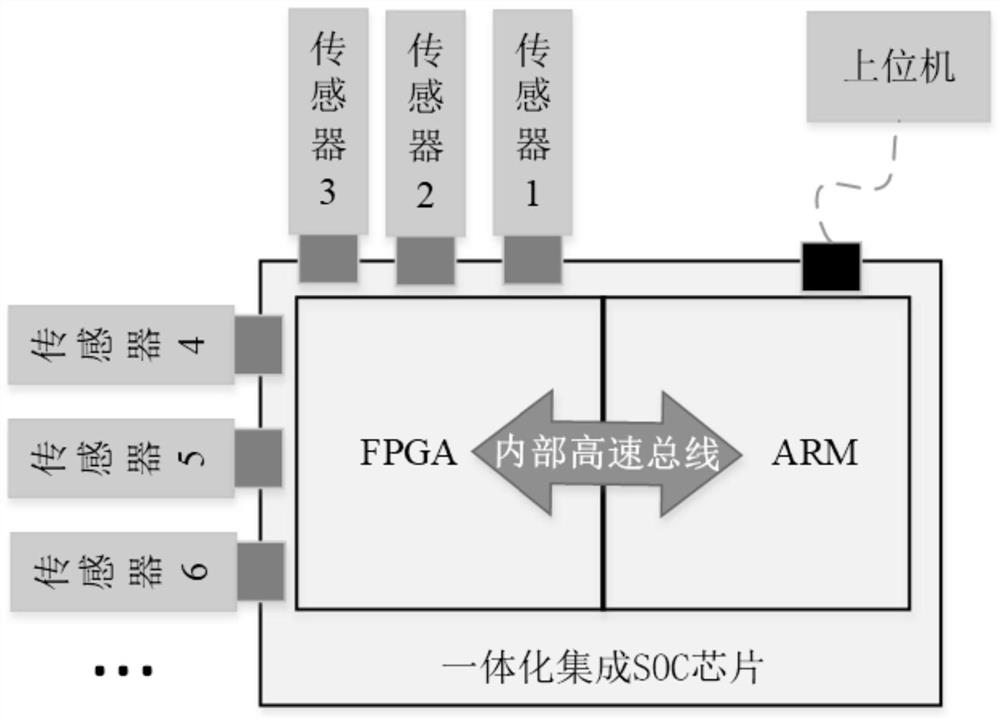

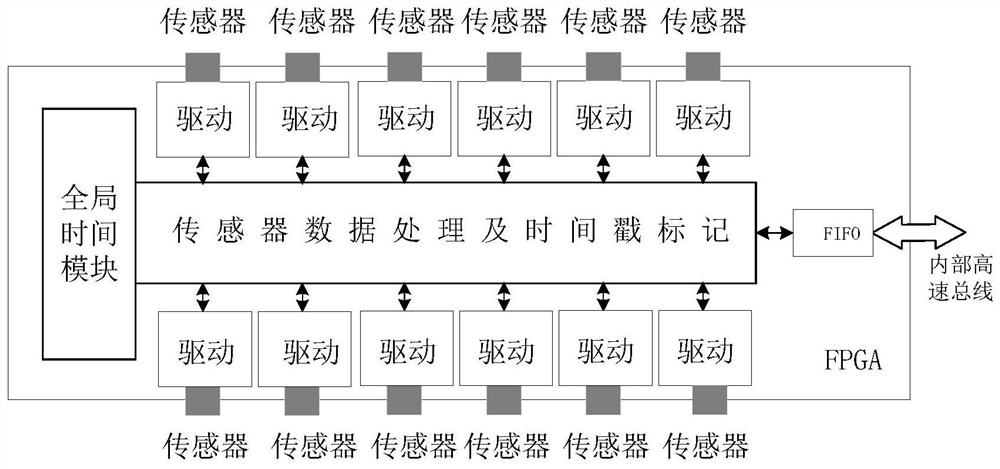

Robot chassis control system and method based on time hard synchronization

ActiveCN111791232AIncrease the speed of communication and interconnectionHigh precisionProgramme-controlled manipulatorArchitecture with single central processing unitControl systemNetwork Communication Protocols

The invention discloses a robot chassis control system and method based on time hard synchronization, and the system and method carry all sensors based on a high-speed processing SOC chip with an embedded FPGA + ARM core, and achieve the algorithm of the whole chassis control system. Compared with an FPGA + ARM heterogeneous separation scheme, the integration level and the communication interconnection rate of the system can be further improved. Data requests and responses of all sensors can be processed in real time by means of the efficient and powerful parallel processing capacity of the FPGA; meanwhile, a global clock module is constructed in the FPGA, and the FPGA automatically marks timestamps according to the clock module when processing the sensor data, assembles all the sensor data into frames and sends the frames to the ARM core. The ARM is responsible for logic protocol analysis and control process scheduling, plays a connection link role, and performs encapsulation and uploading of a lower computer network communication protocol and analysis and task scheduling of an instruction issued by an upper computer. The method ensures that the robot chassis control system can effectively solve the problem of data transmission delay, and has a good application prospect.

Owner:武汉威文科技有限公司

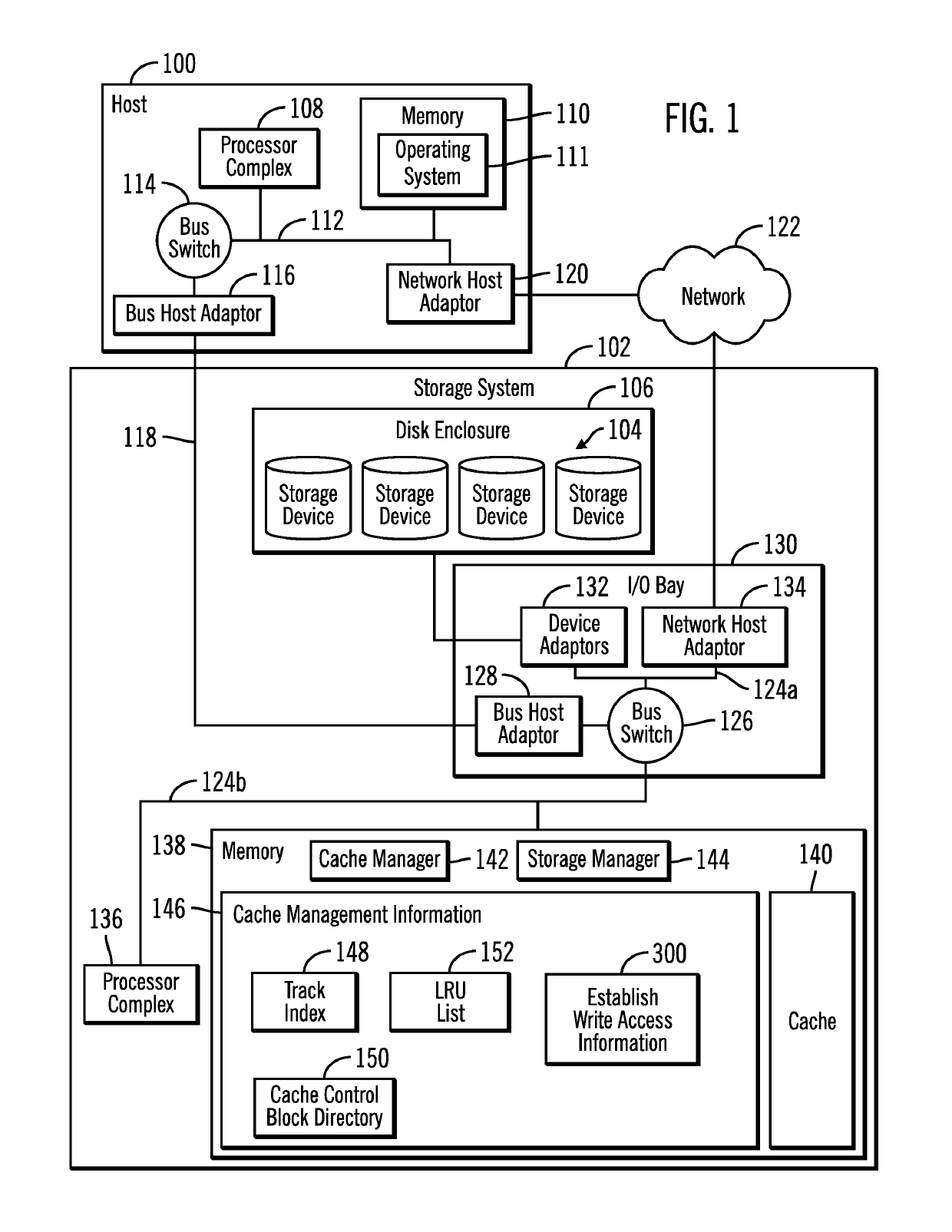

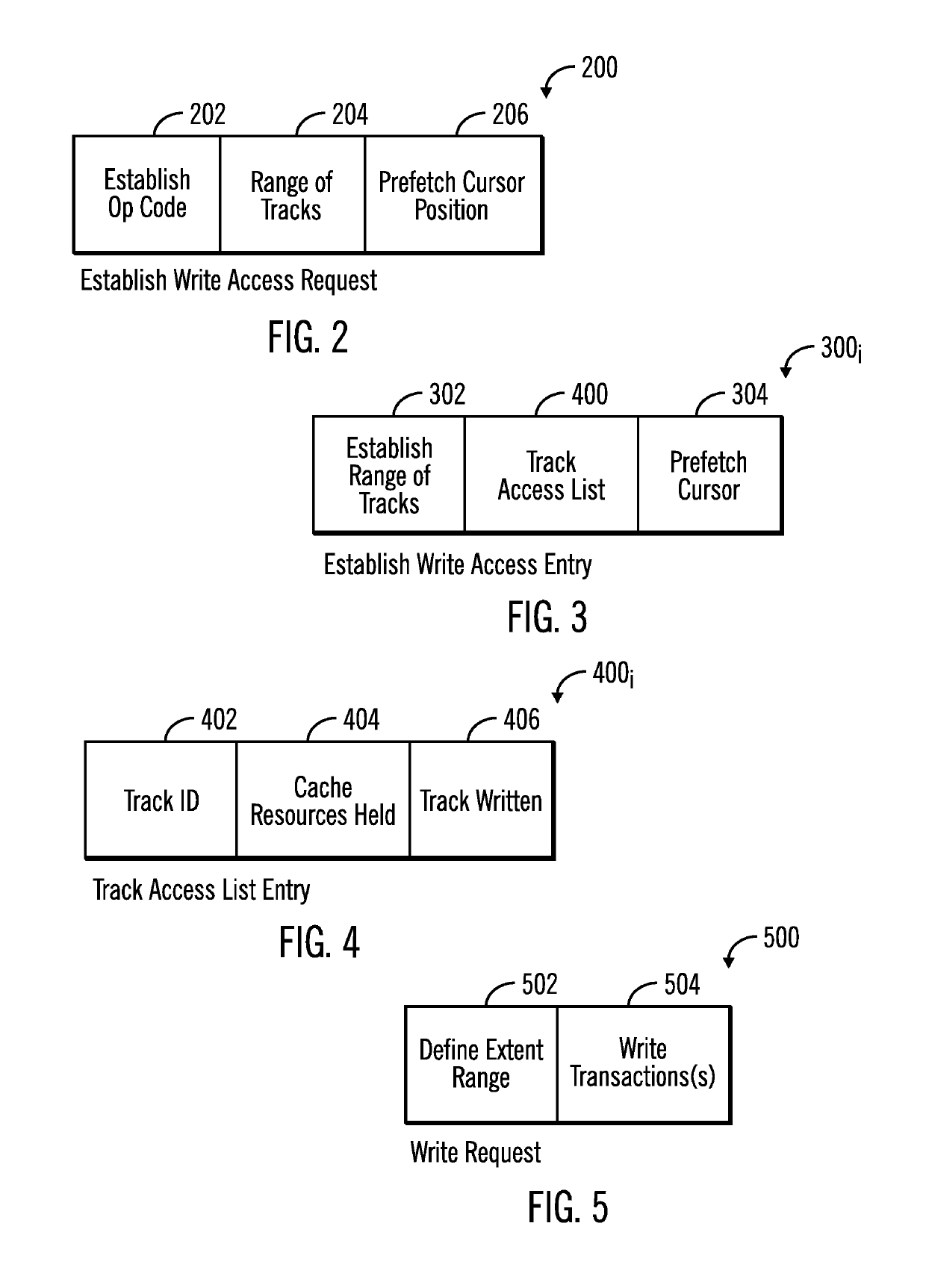

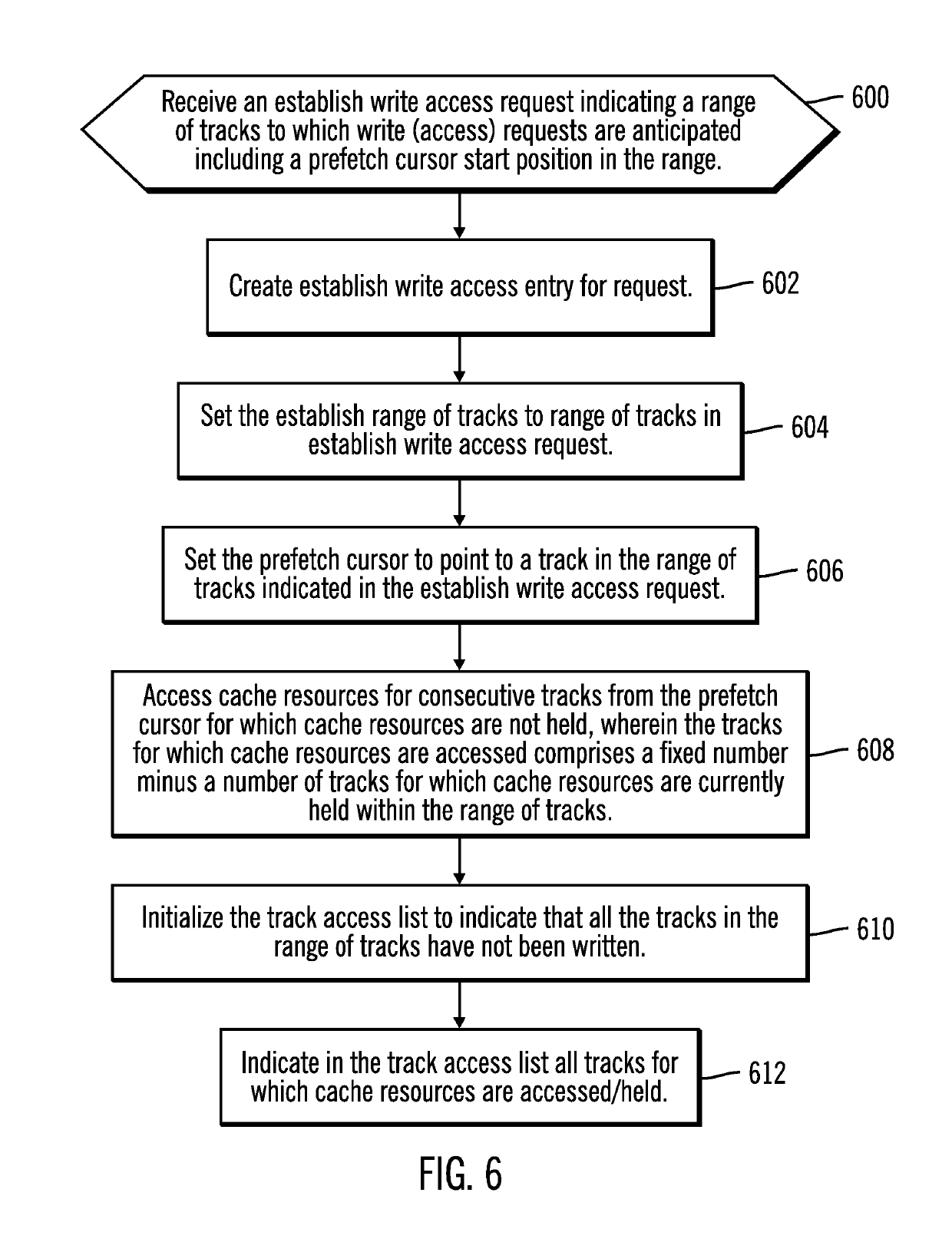

Pre-allocating cache resources for a range of tracks in anticipation of access requests to the range of tracks

ActiveUS10528474B2Lower latencySimple processMemory architecture accessing/allocationInput/output to record carriersCache accessTrackway

Provided are a computer program product, system, and method for managing access requests from a host to tracks in storage. A cursor is set to point to a track in a range of tracks established for sequential accesses. Cache resources are accessed for the cache for tracks in the range of tracks in advance of processing access requests to the range of tracks. Indication is received of a subset of tracks in the range of tracks for subsequent access transactions and a determination is made whether the cursor points to a track in the subset of tracks. The cursor is set to point to a track in the subset of tracks and cache resources are accessed for tracks in the subset of tracks for anticipation of access transactions to tracks in the subset of tracks.

Owner:INT BUSINESS MASCH CORP

Lookup engine with reconfigurable low latency computational tiles

An architecture for a specialized electronic computer for high-speed data lookup employs a set of tiles each with independent logic elements lookup memory portions. The tiles may each comprise gate-array-like functional units that may be wired together by a multi-way switch for extremely low latency.

Owner:WISCONSIN ALUMNI RES FOUND

Transactionally deterministic high speed financial exchange having improved, efficiency, communication, customization, performance, access, trading opportunities, credit controls, and fault tolerance

The disclosed embodiments relate to implementation of a trading system, which may also be referred to as a trading system architecture, having improved performance which further assures transactional determinism under increasing processing transaction loads while providing improved trading opportunities, fault tolerance, low latency processing, high volume capacity, risk mitigation and market protections with minimal impact, as well as improved and equitable access to information and opportunities.

Owner:CHICAGO MERCANTILE EXCHANGE INC

Low-delay VDE satellite-borne downlink digital signal processing system based on FPGA

InactiveCN111431579AReduce resource usageLow latency processingRadio transmissionChannel coding adaptationDigital signal processingEngineering

The invention provides a low-delay VDE satellite-borne downlink digital signal processing system based on an FPGA, and the system is characterized in that the system comprises a data partitioning andhigh-speed forwarding module, an efficient partitioning Turbo coding and scrambling processing module, and a multi-bandwidth universal modulation transmission processing module. According to the low-delay digital signal processing method and module design based on the VDE communication protocol mechanism, VDE modulation signal sending delay is greatly reduced, FPGA resource occupation is reduced,and the low-delay digital signal processing method and module design can be applied to a VDE satellite-borne downlink digital signal processing scene.

Owner:SHANGHAI SPACEFLIGHT ELECTRONICS & COMM EQUIP RES INST

Transactionally deterministic high speed financial exchange having improved, efficiency, communication, customization, performance, access, trading opportunities, credit controls, and fault tolerance

The disclosed embodiments relate to implementation of a trading system, which may also be referred to as a trading system architecture, having improved performance which further assures transactional determinism under increasing processing transaction loads while providing improved trading opportunities, fault tolerance, low latency processing, high volume capacity, risk mitigation and market protections with minimal impact, as well as improved and equitable access to information and opportunities.

Owner:CHICAGO MERCANTILE EXCHANGE INC

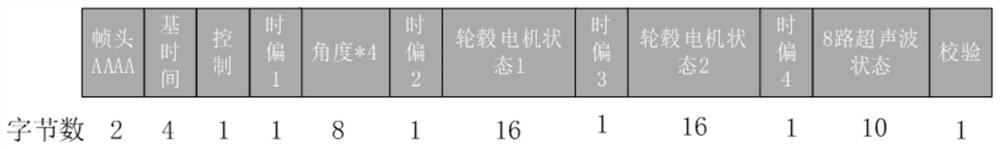

A robot chassis control system and method based on time hard synchronization

ActiveCN111791232BIncrease the speed of communication and interconnectionHigh precisionProgramme-controlled manipulatorArchitecture with single central processing unitControl systemNetwork communication

The invention discloses a robot chassis control system and method based on time hard synchronization. The system and method are based on a high-speed processing SOC chip embedded with FPGA+ARM cores equipped with all sensors to realize the algorithm of the entire chassis control system. Compared with the heterogeneous separation scheme of FPGA+ARM, the present invention can further improve the integration degree of the system and the communication interconnection rate. With the efficient and powerful parallel processing capability of FPGA, data requests and responses of all sensors can be processed in real time; at the same time, a global clock module is built in FPGA, and FPGA automatically marks time stamps according to the clock module when processing sensor data, and assembles all sensor data Framing is sent to the ARM core. ARM is responsible for logical protocol analysis and control process scheduling, and acts as a link between the preceding and the following. It performs the encapsulation and uploading of the network communication protocol of the lower computer, as well as the analysis and task scheduling of the instructions issued by the upper computer. The invention ensures that the control of the robot chassis control system can effectively solve the problem of data transmission delay, and has good application prospects.

Owner:武汉威文科技有限公司

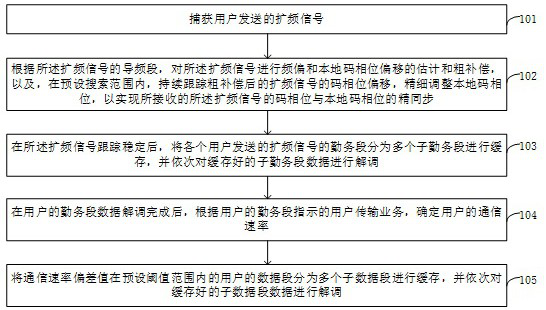

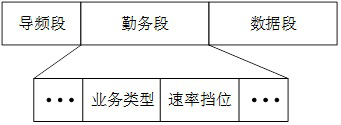

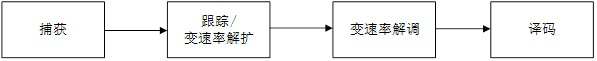

Signal processing method, device, electronic equipment and storage medium of spaceborne receiver

The present application provides a signal processing method, device, electronic equipment and storage medium of a satellite-borne receiver. The method includes: capturing the spread spectrum signal sent by the user; according to the pilot band of the spread spectrum signal, estimating and roughly compensating the frequency offset and local code phase offset of the spread spectrum signal, and tracking the code phase of the roughly compensated spread spectrum signal Offset, finely adjust the local code phase; after the spread spectrum signal is tracked and stabilized, the service segment of the spread spectrum signal sent by each user is divided into multiple sub-service segments for buffering, and the cached sub-service segment data is sequentially demodulated; Determine the user's communication rate according to the user's transmission service indicated by the user's service segment; divide the user's data segment with a communication rate deviation value within the preset threshold range into multiple sub-data segments for caching, and sequentially cache the cached sub-services The segment data is demodulated. The application can realize low-delay processing of signals of different communication services, adapt to multi-rate signal demodulation of different services, and has low complexity.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

Transactionally deterministic high speed financial exchange having improved, efficiency, communication, customization, performance, access, trading opportunities, credit controls, and fault tolerance

Owner:CHICAGO MERCANTILE EXCHANGE INC

Method of realizing smooth playback of network theater based on cloud classroom scene

ActiveCN106231352BReduce trafficOptimize codec parametersSelective content distributionElectrical appliancesInternet trafficEngineering

The invention provides a method for realizing network cinema fluent playing based on a cloud classroom scene. The system according to the method comprises at least one teacher side and multiple student sides. The teacher side uses a standard RTP protocol and broadcasts audio and video streams to the student sides in a multicast manner by using the multicast function of the router in a local area network so as to reduce network traffic. The teacher side is customized based on a VLC open source player and comprises a customized player interface and optimized coding and decoding parameters, and the standard H264 stream is used for coding of the teacher side. The video streams to be played are decoded on the student sides by using hardware, and audios and videos are added in the playing process to perform synchronous control playing. The problem of low fluency in playing 1080P high-definition videos of the network cinema under the cloud classroom can be solved so that fluent playing of the student sides can be realized.

Owner:FUJIAN CENTM INFORMATION

Transactionally deterministic high speed financial exchange having improved, efficiency, communication, customization, performance, access, trading opportunities, credit controls, and fault tolerance

The disclosed embodiments relate to implementation of a trading system, which may also be referred to as a trading system architecture, having improved performance which further assures transactional determinism under increasing processing transaction loads while providing improved trading opportunities, fault tolerance, low latency processing, high volume capacity, risk mitigation and market protections with minimal impact, as well as improved and equitable access to information and opportunities.

Owner:CHICAGO MERCANTILE EXCHANGE INC

Transactionally deterministic high speed financial exchange having improved efficiency, communication, customization, performance, access, trading opportunities, credit controls, and fault tolerance

The disclosed embodiments relate to implementation of a trading system, which may also be referred to as a trading system architecture, having improved performance which further assures transactional determinism under increasing processing transaction loads while providing improved trading opportunities, fault tolerance, low latency processing, high volume capacity, risk mitigation and market protections with minimal impact, as well as improved and equitable access to information and opportunities.

Owner:CHICAGO MERCANTILE EXCHANGE INC

Transactionally deterministic high speed financial exchange having improved, efficiency, communication, customization, performance, access, trading opportunities, credit controls, and fault tolerance

The disclosed embodiments relate to implementation of a trading system, which may also be referred to as a trading system architecture, having improved performance which further assures transactional determinism under increasing processing transaction loads while providing improved trading opportunities, fault tolerance, low latency processing, high volume capacity, risk mitigation and market protections with minimal impact, as well as improved and equitable access to information and opportunities.

Owner:CHICAGO MERCANTILE EXCHANGE INC