Bit cell applied to in-memory computation and memory computation array device

A bit unit and storage unit technology, applied in the field of in-memory computing, can solve the problems of high power consumption and large area of the six-tube structure, and achieve the effects of reducing power consumption, simplifying structure, and improving calculation accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

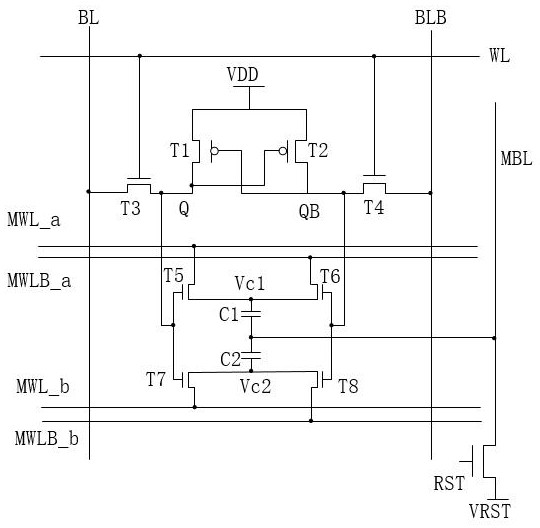

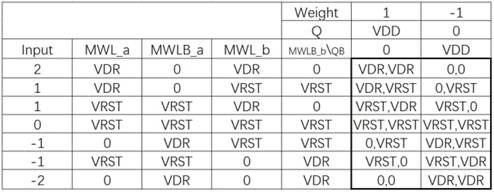

[0060] Such as figure 1 As shown, the present invention provides a bit unit applied to in-memory calculation, the bit unit includes: a four-pipe storage unit and a peripheral storage operation for accumulating and adding the activation signal and the weight output by the four-pipe storage unit circuit; the weight output end of the four-tube storage unit is connected to the weight input end of the four-tube storage unit, and the inverse weight output end of the four-tube storage unit is connected to the inverse weight of the four-tube storage unit The input terminal is connected; the word line control terminal (the control terminal of the transistor T3 and the transistor T4) of the four-tube memory unit is connected to the word line WL, and the bit line control terminal (the input terminal of the transistor T3) of the four-tube memory unit is connected to the The bit line BL is connected, and the reverse bit line control terminal (input terminal of transistor T4) of the four-tu...

Embodiment 2

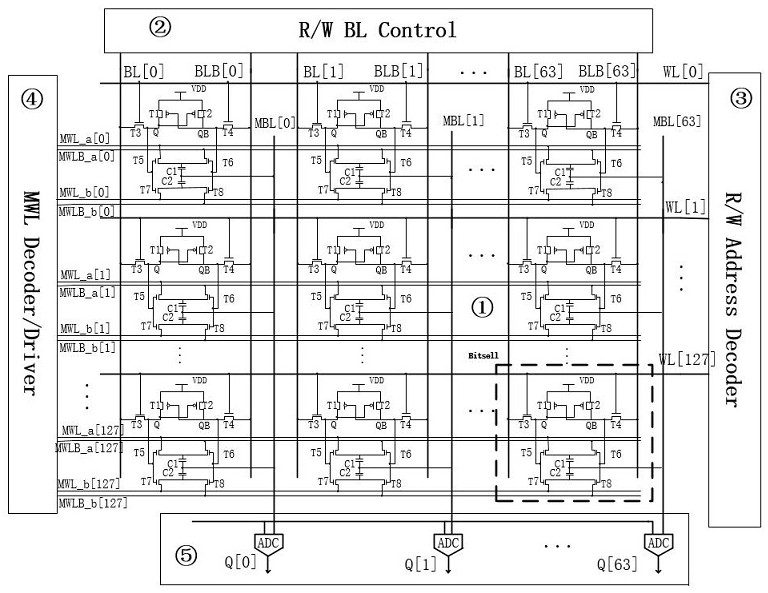

[0070] The present invention also provides a storage and calculation array device, and the storage and calculation array device includes:

[0071] Storage array module ①, column decoding module ②, row decoding module ③, input activation drive module ④ and analog-to-digital conversion output module ⑤; the storage array module includes A bit unit applied to memory calculation; n bit line output terminals of the column decoding module are respectively connected to n bit lines, and n reverse bit line output terminals of the column decoding module are respectively connected to n reverse bit lines; The m word line output terminals of the row decoding module are respectively connected to the m word lines; the m first activation signal output terminals of the memory array module are respectively connected to the m first activation signal lines; The deactivation signal output terminals are respectively connected to the m first deactivation signal lines; the m second activation signal ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More