Nano CMOS circuit fault-tolerant mapping method capable of optimizing time delay

A mapping method, nanotechnology, applied in nanotechnology CAD, electrical digital data processing, instruments, etc., can solve problems such as poor solution speed and quality, poor delay performance, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

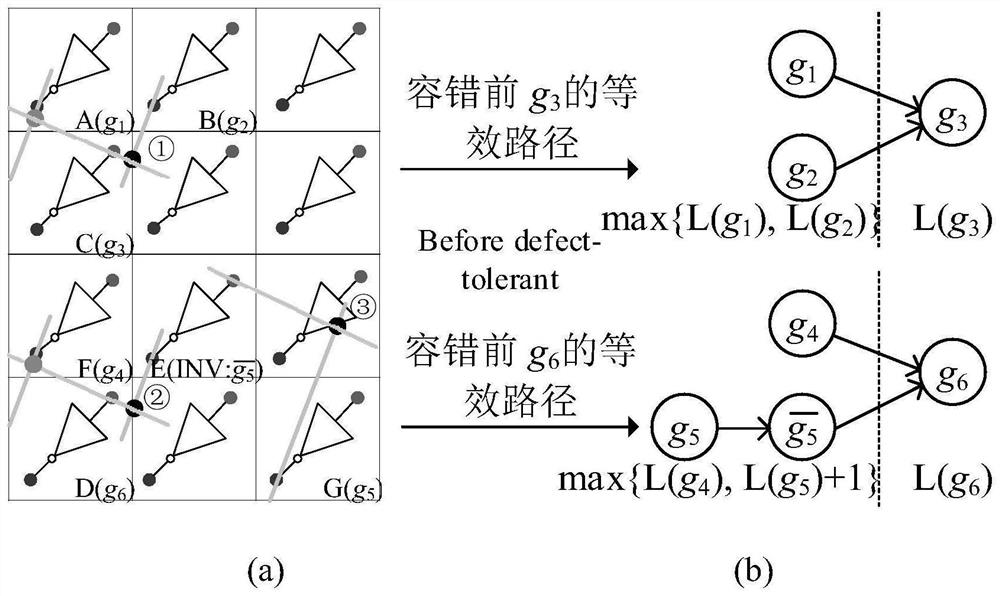

[0077] Embodiment 1: with Figure 6 The s27 circuit in the shown ISCAS'89 reference circuit is taken as an example, and the method of the present invention is used for fault-tolerant mapping.

[0078] According to topological sorting, the s27 circuit contains 7 original inputs and 3 original outputs O 0 , O 1 , O 2 , 12 logic gates. According to the original output O 0 , O 1 , O 2 Can build 3 path tree PO 0 、PO 1 and PO 2 . where O 1 and O 2 The corresponding logic gate g 18 and g 19 The logic level is the highest, L(g 18 ) = L(g 19 )=7, so there are two critical path trees, g 11 、g 18 and g 19 are the root logic gates of the three path trees respectively. The division method of the three path trees includes the following steps:

[0079] Step ①: According to the descending order of logical level, use the breadth search algorithm to calculate the logic gate g located in L6 17 The degree of association with its output logic gate, where, calculated according ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More