Patents

Literature

41results about How to "Improve mapping ability" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Rolling bearing fault diagnosis method in various working conditions based on feature transfer learning

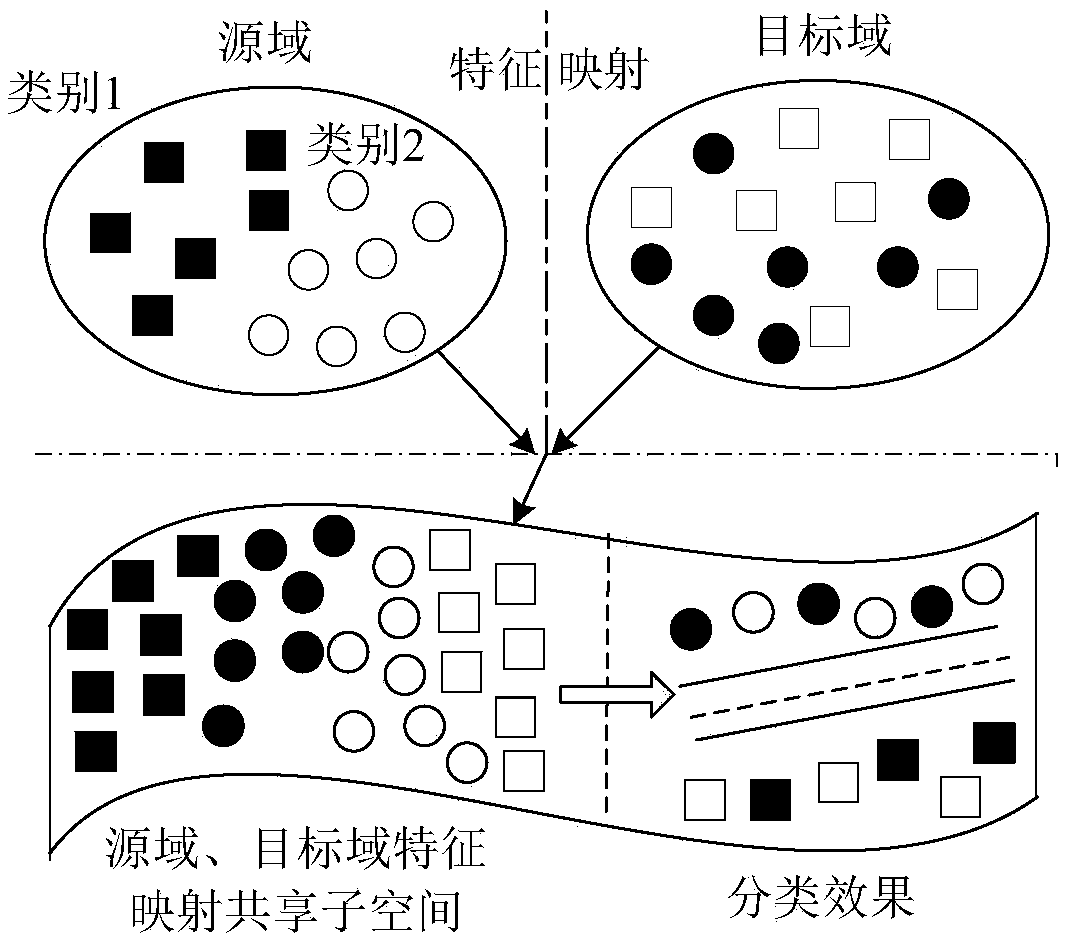

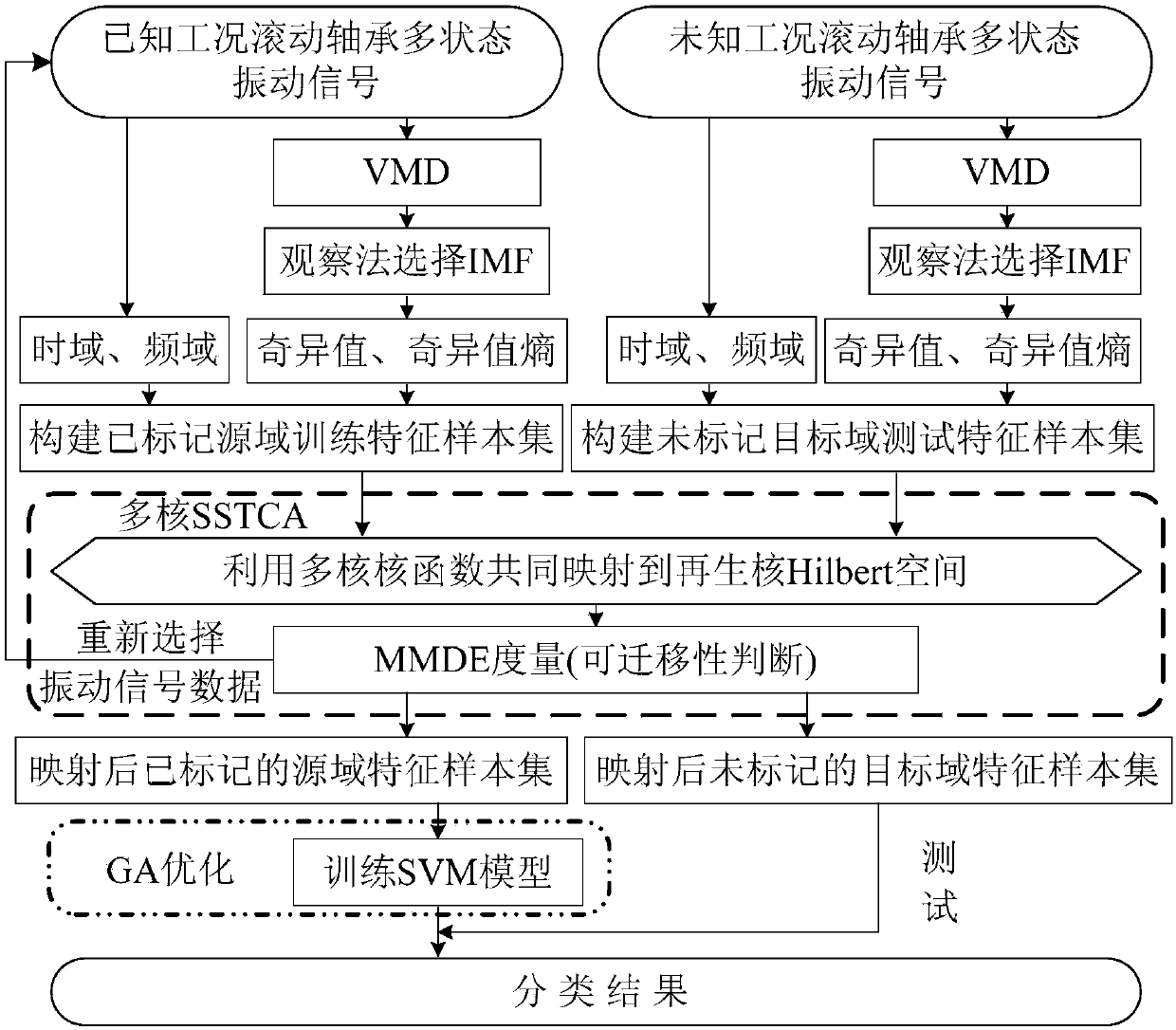

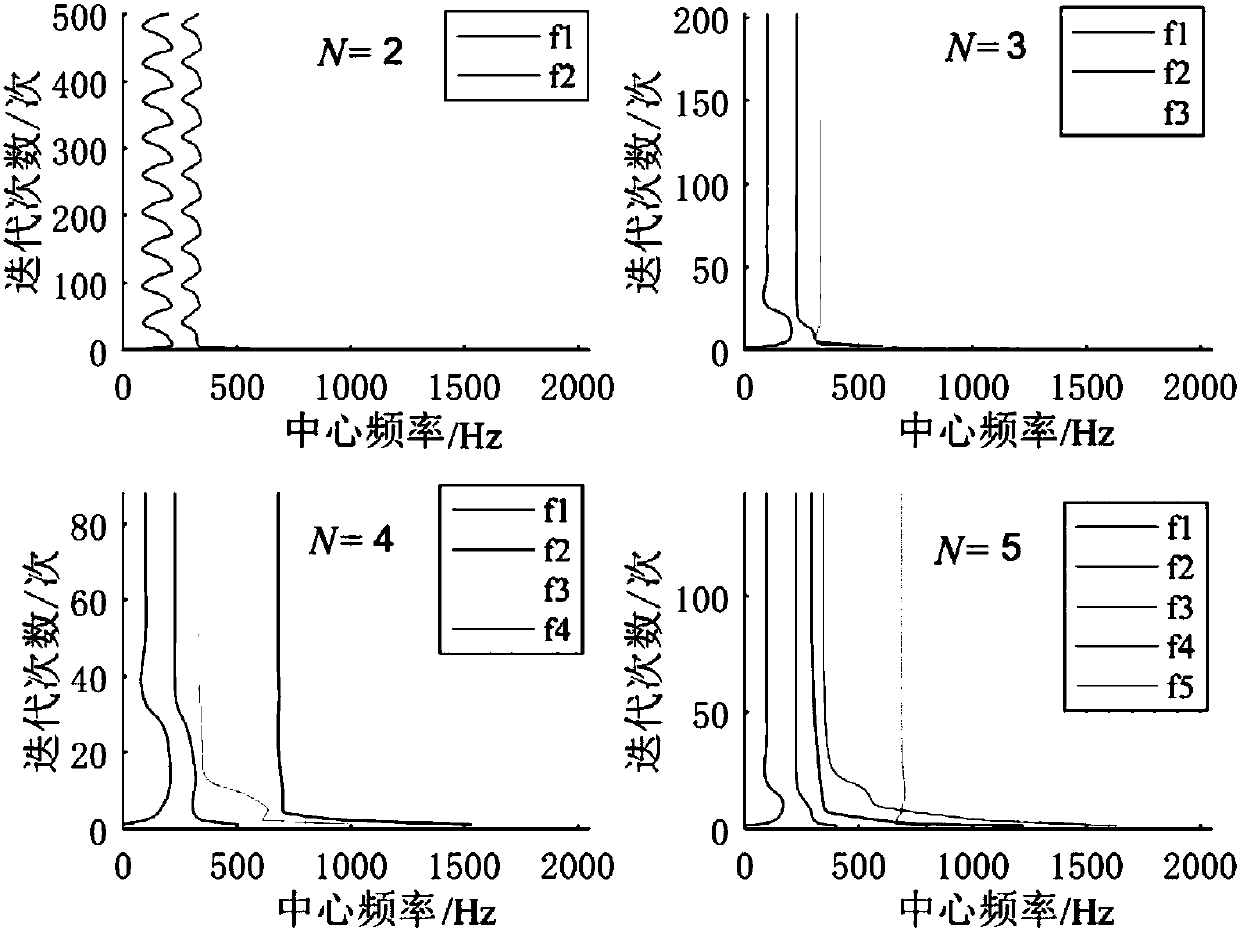

ActiveCN108414226ABest mapped kernel matrixImprove accuracyMachine bearings testingSingular value decompositionDecomposition

The present invention provides a rolling bearing fault diagnosis method in various working conditions based on feature transfer learning, and relates to the field of fault diagnosis. The objective ofthe invention is to solve the problem that a rolling bearing, especially to various working conditions, is low in accuracy of diagnosis. The method comprise the steps of: employing a VMD (VariationalMode Decomposition) to perform decomposition of vibration signals of a rolling bearing in each state to obtain a series of intrinsic mode functions, performing singular value decomposition of a matrixformed by the intrinsic mode functions to solve a singular value or a singular value entropy, combining time domain features and frequency domain features of the vibration signals to construct a multi-feature set; introducing a semisupervised transfer component analysis method to perform multinuclear construction of a kernel function thereof, sample features of different working conditions are commonly mapped to a shared reproducing kernel Hilbert space so as to improve the data intra-class compactness and the inter-class differentiation; and employing the maximum mean discrepancy embedding to select more efficient data as a source domain, inputting source domain feature samples into a SVM (Support Vector Machine) for training, and testing target domain feature samples after mapping. Therolling bearing fault diagnosis method in various working conditions has higher accuracy in the rolling bearing multi-state classification in various working conditions.

Owner:HARBIN UNIV OF SCI & TECH

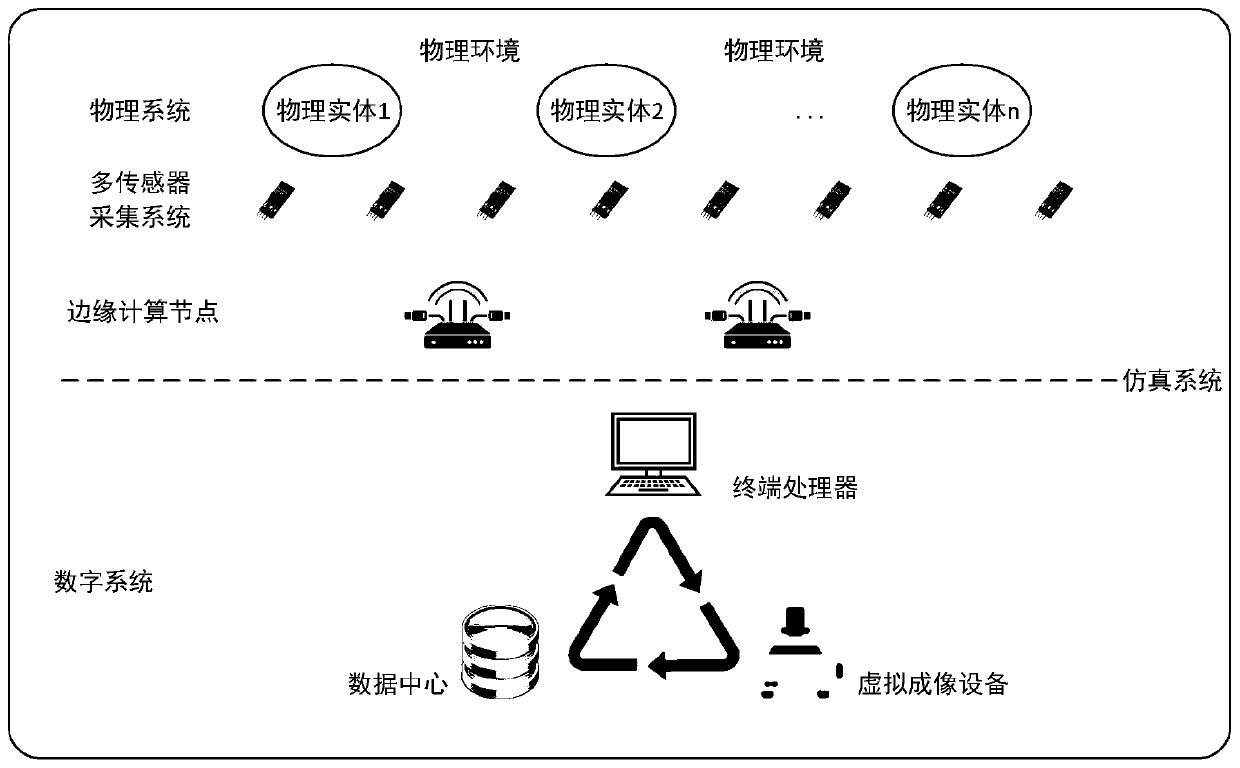

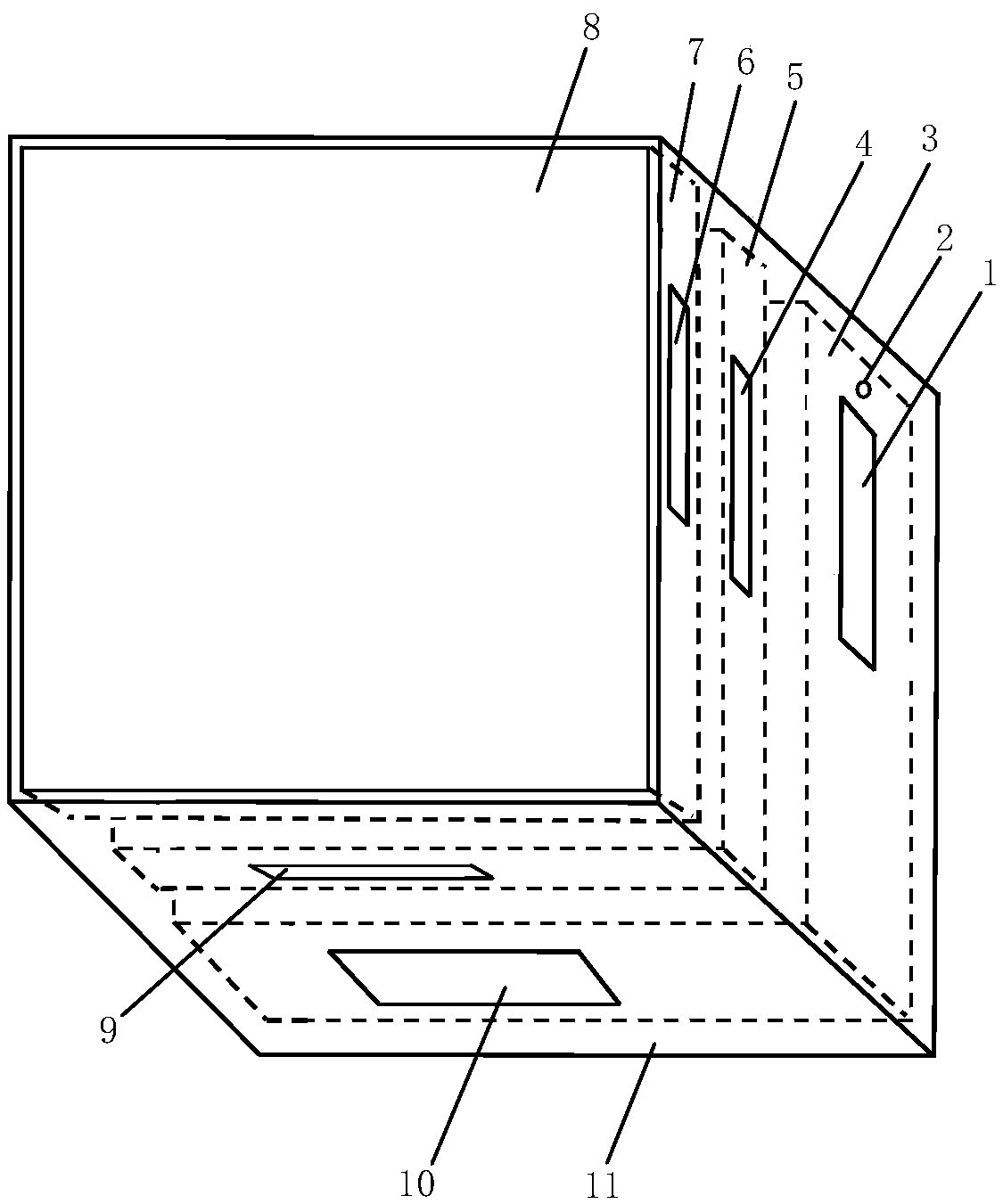

A digital twinning system based on a virtual imaging technology

ActiveCN109819233ASolve the strength problemSolve the incomplete display of digital entity informationTransmissionImage data processingEdge computingMultiple sensor

The invention relates to a strong mapping digital twin system based on a virtual imaging technology. According to the system, a multi-information cooperative communication mechanism is established between digital twin bodies, morphological information, state information and behavior information of a physical entity system are collected through multiple sensors and sent to an edge computing node, and the edge computing node is responsible for receiving sensor information and carrying out edge computing processing on the received information; A virtual imaging technology is applied to project digital entities of the digital twin system into a real space in a three-dimensional visualization mode, meanwhile, state information of the physical entities is displayed in a virtual reality mode, thedetail display effect of the digital twin system is enhanced, and the requirements for multi-view observation and immersion experience are met; According to the system, strong information mapping isestablished between a physical entity and a digital entity through the process, and it is guaranteed that information is transmitted between twin bodies in real time at a high speed in an undistortedmode.

Owner:合肥哈工热气球数字科技有限公司

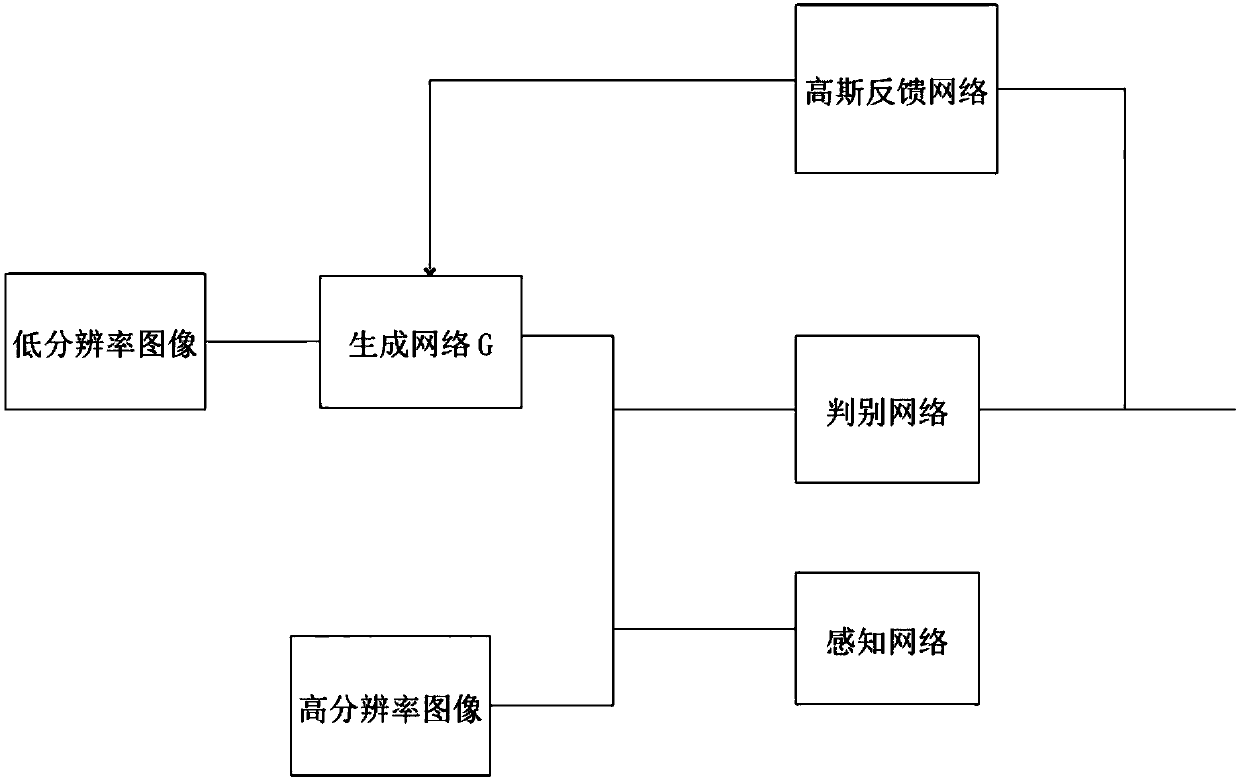

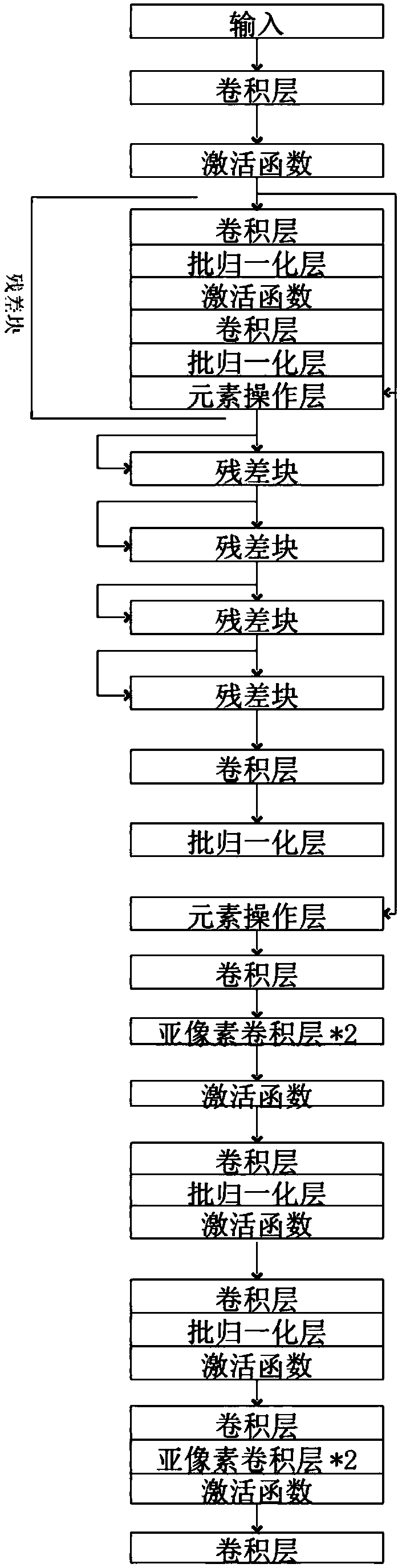

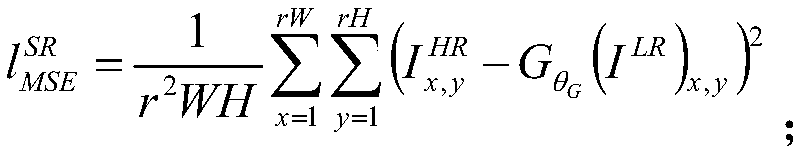

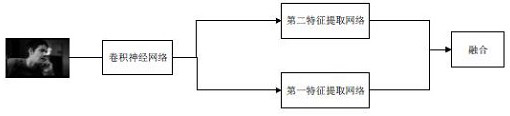

An image super-resolution reconstruction method of a generative adversarial network based on Gaussian coding feedback

ActiveCN109685716AImprove mapping abilityReduce useless informationGeometric image transformationNeural architecturesPattern recognitionData set

The invention discloses an image super-resolution reconstruction method of a generative adversarial network based on Gaussian coding feedback, and the method comprises the steps: carrying out the preprocessing of an ImageNet data set, and manufacturing a reconstruction data set in one-to-one correspondence with a low-resolution image and a high-resolution image; Constructing a generative adversarial network model for training, and introducing a Gaussian coding feedback network into the model; Sequentially inputting the data sets obtained in the step A into a generative adversarial network formodel training; And inputting the low-resolution image to be processed into a trained generative adversarial network to obtain a high-resolution image. A generative adversarial network is formed by constructing a generation network and a discrimination network, a Gaussian coding feedback loop is added between the generation network and the discrimination network, more information is added to the generation network to guide the generation network to carry out training, and important features are added by improving a sub-pixel convolutional layer structure, so that useless information is reduced, and the reconstruction effect is improved.

Owner:DALIAN MARITIME UNIVERSITY

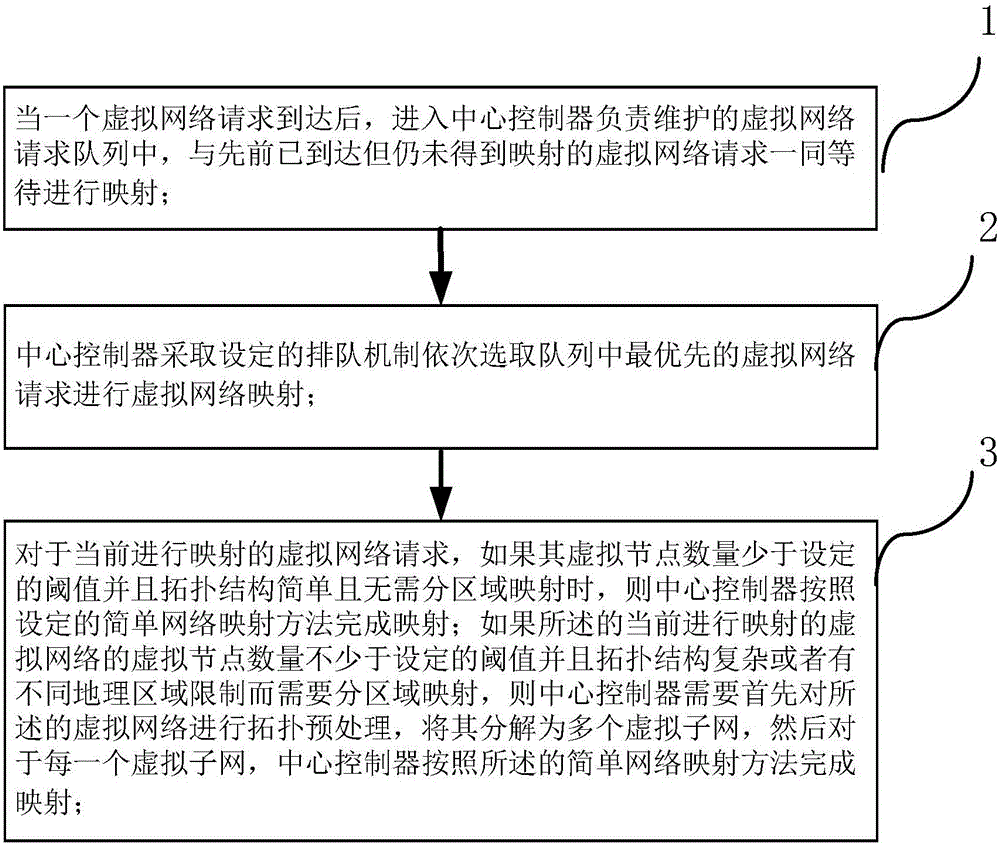

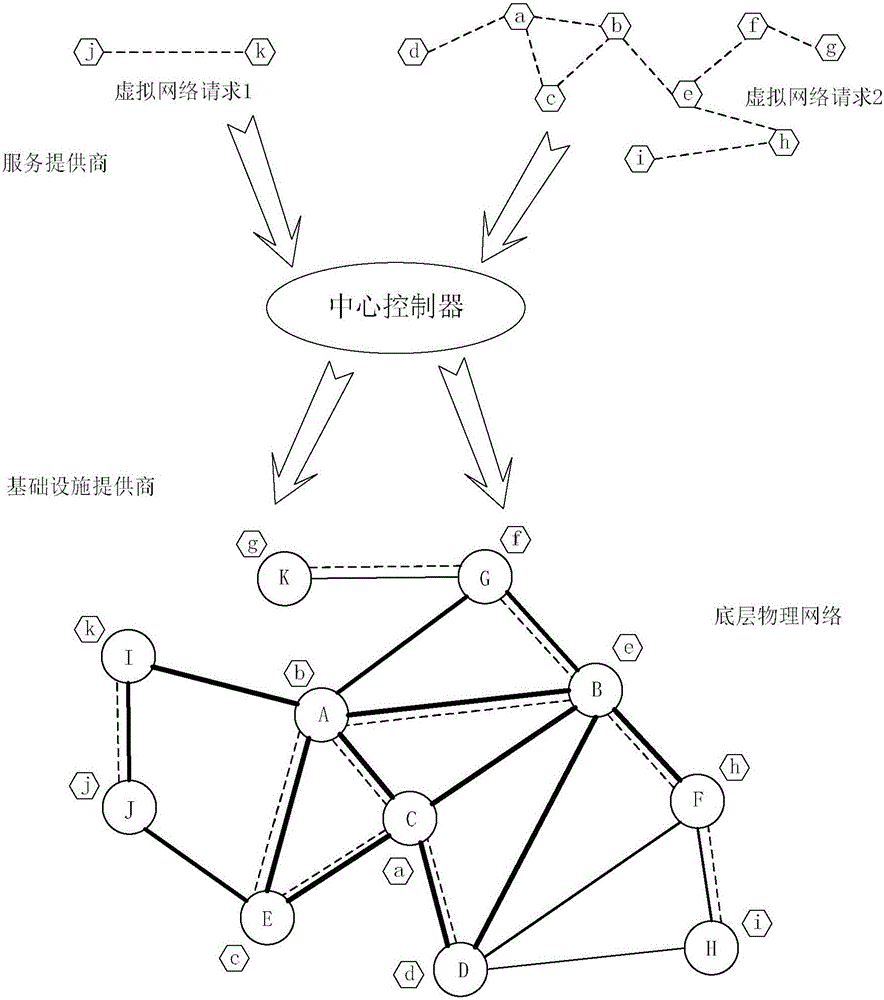

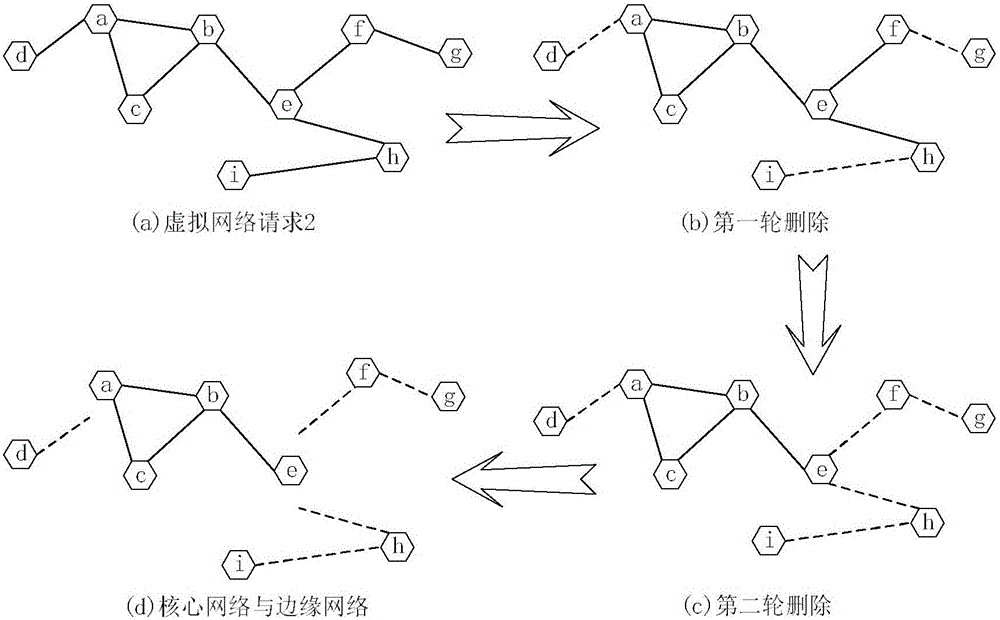

Collaborative virtual network mapping method

InactiveCN105939244AReduce loadScalability problem mitigationNetworks interconnectionVirtual networkNetwork mapping

The invention provides a collaborative virtual network mapping method, comprising the following steps: (1) when a virtual network request arrives, entering a central controller to wait for mapping; (2) selecting an virtual network request with the top priority in a queue by the central controller to carry out mapping; (3) for the virtual network request, if the number of virtual nodes thereof is smaller than a set threshold, a topological structure is simple, and no subregional mapping is needed, accomplishing mapping according to a simple network mapping method; and otherwise, carrying out topology preprocessing on the virtual network request by the central controller to decompose the same into a plurality of virtual sub-networks, and mapping each virtual sub-network according to the simple network mapping method by the central controller. According to the method provided by the invention, relative advantages of a centralized algorithm and a distributed algorithm are fully integrated to achieve better mapping performance.

Owner:BEIJING UNIV OF POSTS & TELECOMM

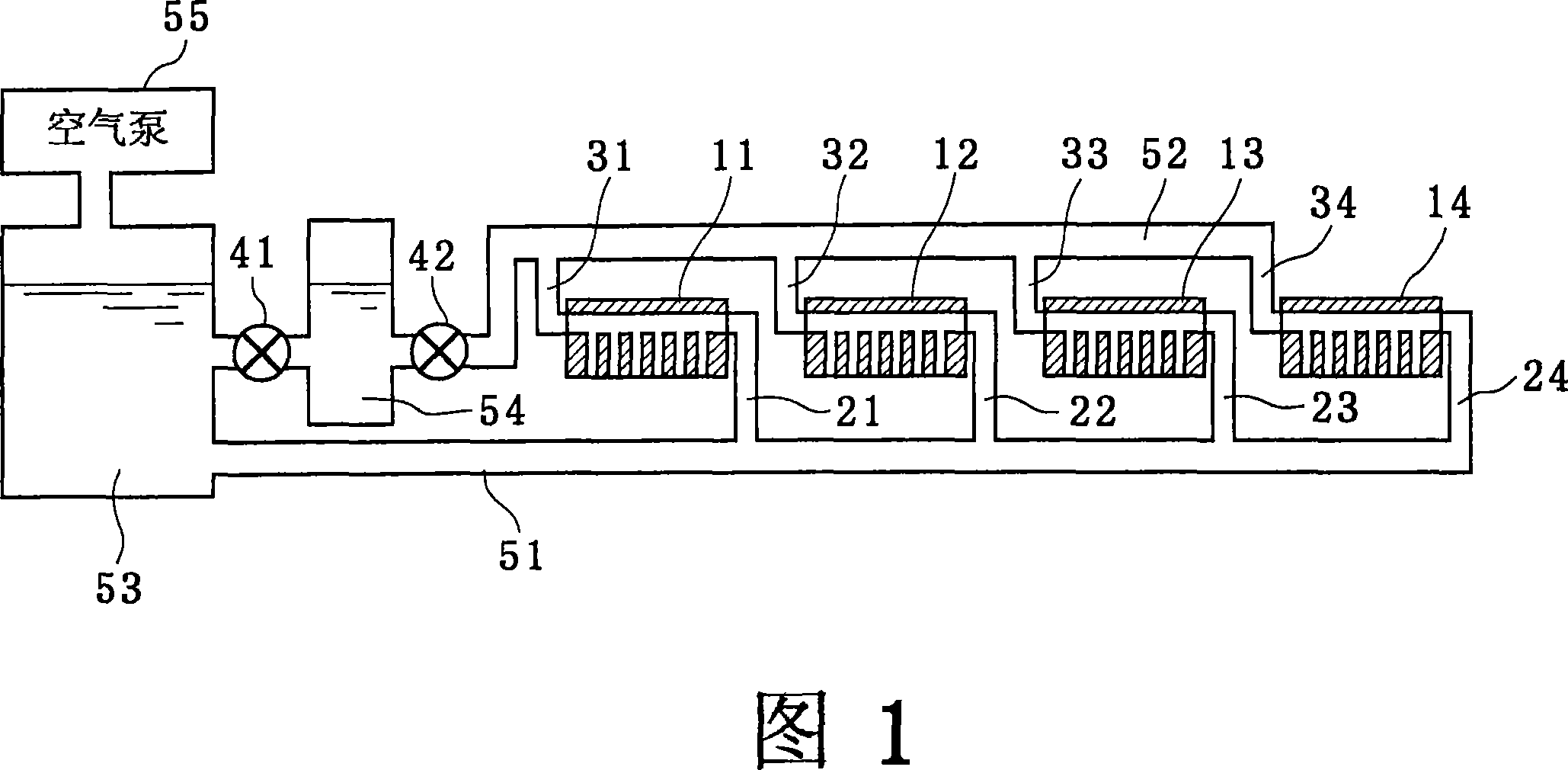

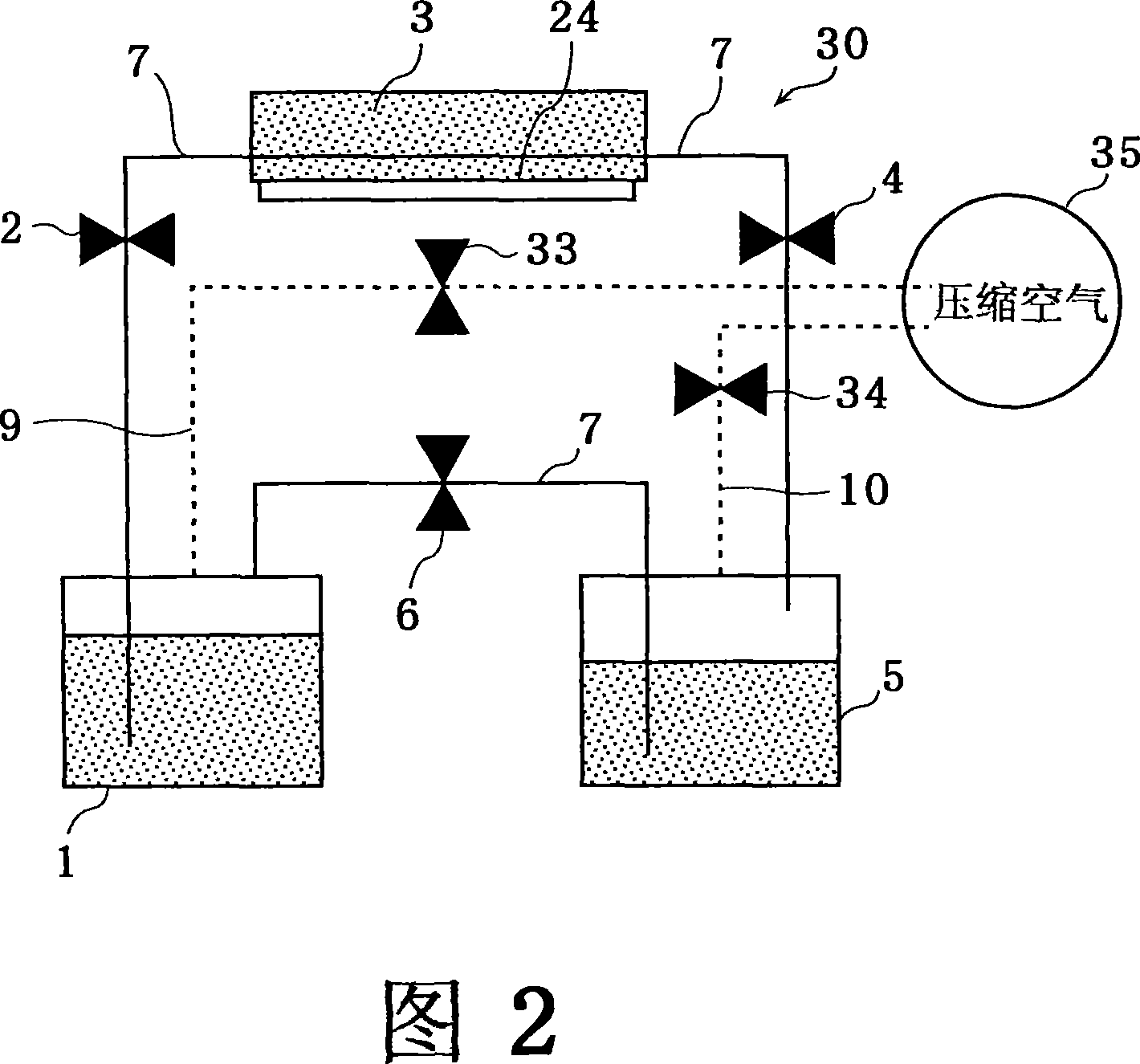

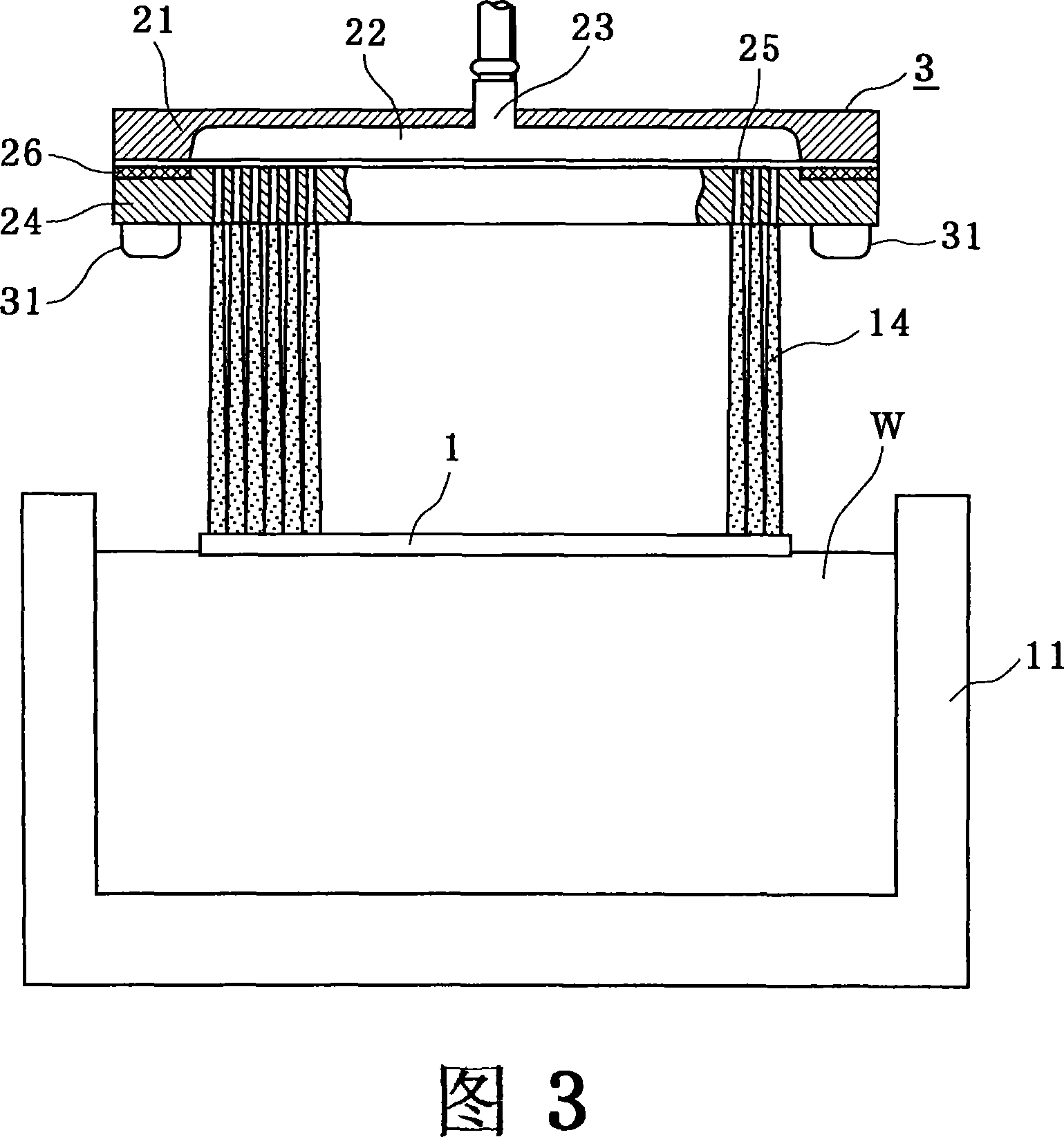

Method of transferring and liquid coating apparatus

InactiveCN101072690ACurb consumptionInhibits disconnection or deformationDecorative surface effectsPretreated surfacesDistortionNozzle

A coating film that upon transfer, excels in adherence and image clarity, being free from appearance defects, such as grain defect, surface rupture, pattern break and distortion. There is provided a method of transferring, comprising the steps of floating transfer sheet (101) on the water surface of transfer bath (11), applying activator (14) onto the transfer sheet (101), dipping transfer recipient (15) in the transfer bath from above the transfer sheet (101) to thereby effect transferring of the transfer sheet (101), further washing away substrate (102) with water, drying the transfer recipient (15) with coating film (105) transferred, and hardening the coating film (105), wherein in the step of applying the activator (14) onto the transfer sheet (101) to thereby attain activation, the activator is emitted through nozzle head (3) equipped with multiple nozzles to which a pressure of 0.008 to 0.040 MPa is applied, and the nozzle head (3) is traveled above the transfer sheet (101).

Owner:PANASONIC CORP

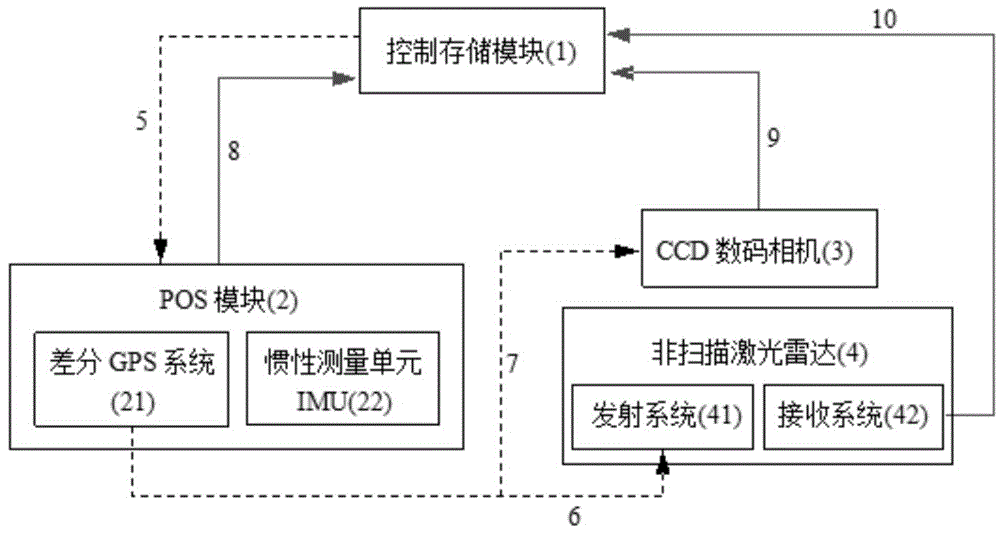

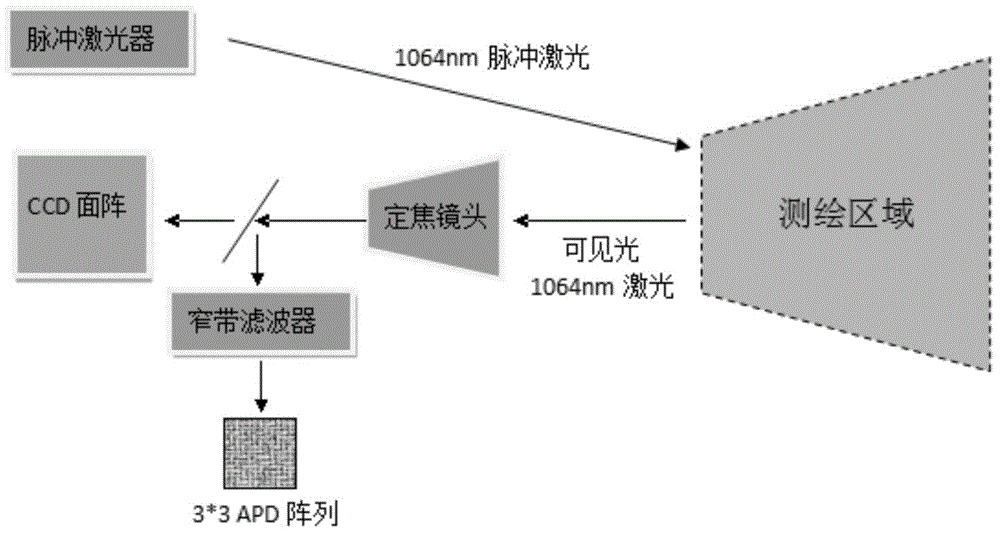

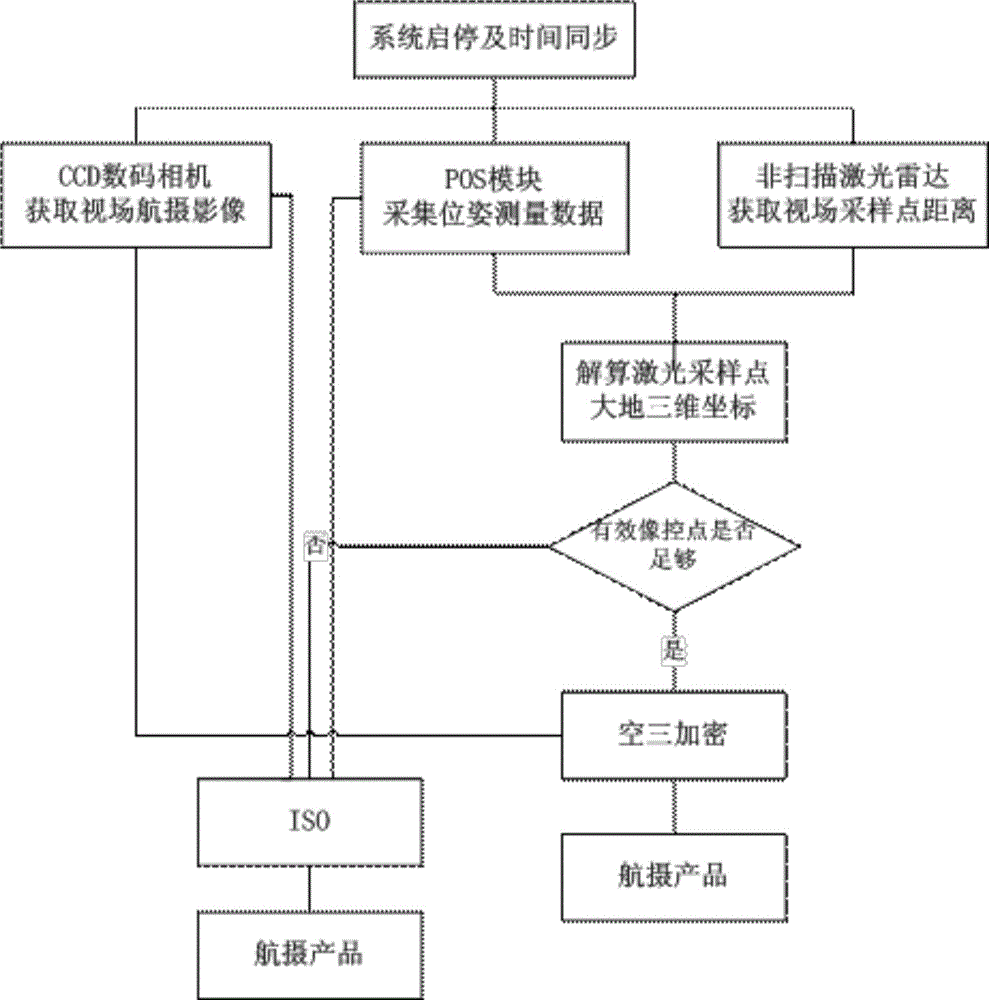

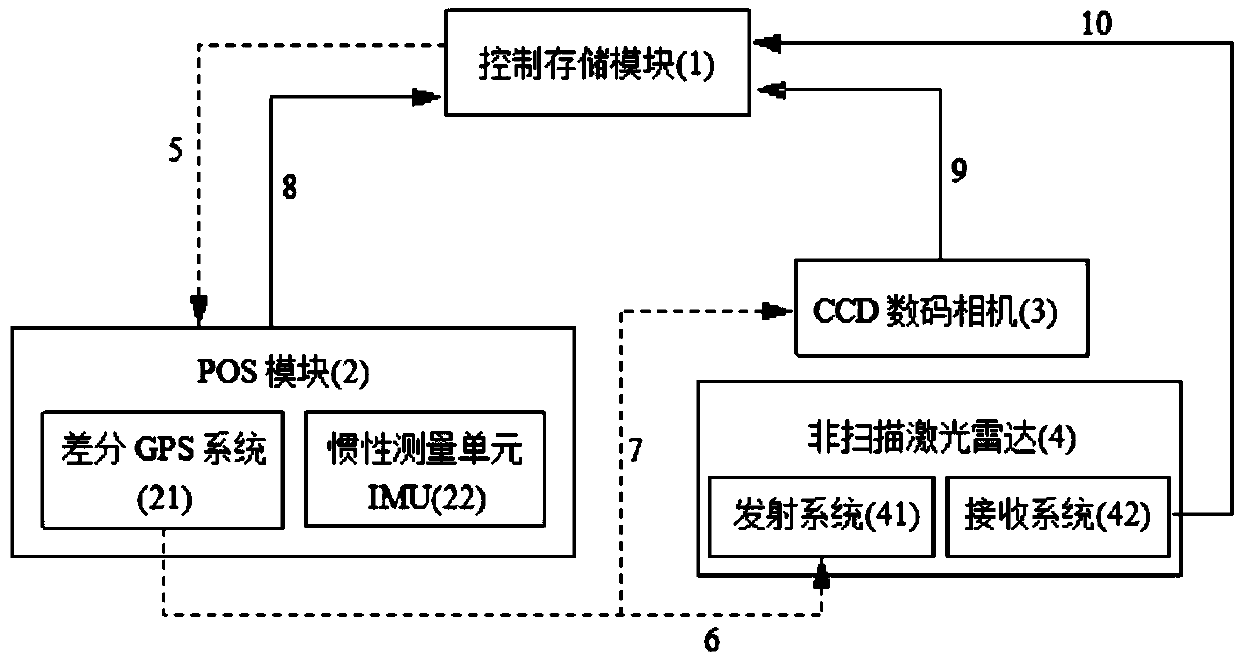

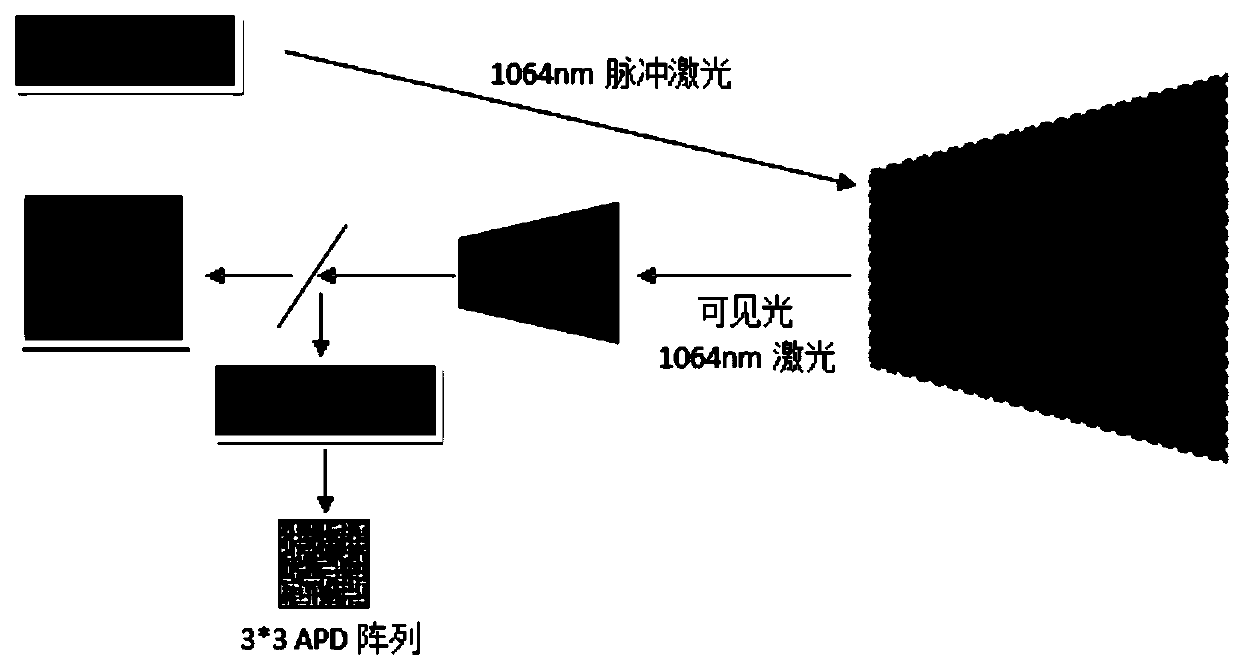

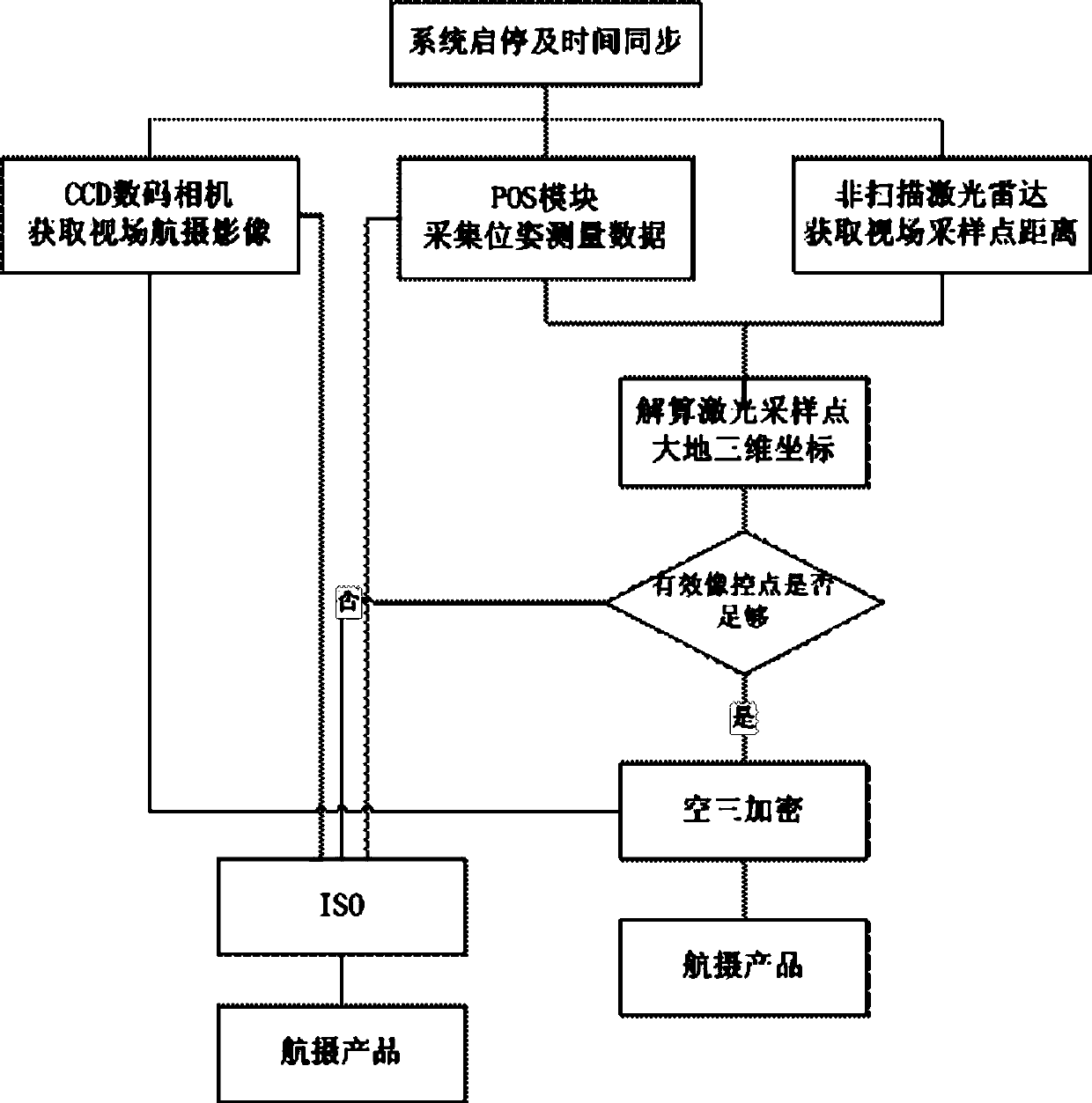

Aerial photogrammetric system integrated with non-scanning laser radar and aerial photogrammetric method

ActiveCN105783875AKeep small and lightweightImprove mapping abilityPhotogrammetry/videogrammetryNavigation by speed/acceleration measurementsPhotographic processingAviation

The invention discloses an aerial photogrammetric system integrated with a non-scanning laser radar and an aerial photogrammetric method. The system comprises the non-scanning laser radar, a CCD (Charge Coupled Device) digital camera, a positioning-orienting POS (Passive Optical Splitter) module and a control-storage module. The method comprises the following steps of carrying out multiple-laser-beam irradiation on a visual field range by the non-scanning laser radar based on a focal plane array, so as to determine the distances of many sampling points in a visual field; meanwhile, by utilizing pose data provided by the positioning-orienting POS module, resolving out the geodetic three-dimensional coordinate of each sampling point as ground control information of subsequent aerial photographic processing; collecting an aerial photogrammetric photo of the same visual field by the CCD digital camera, realizing aerial survey mapping according to the information, which is provided by the laser radar, of a ground control point in quick and low-cost manners. According to the aerial photogrammetric system integrated with the non-scanning laser radar and the aerial photogrammetric method, a conventional field ground control method is replaced by adopting the three-dimensional imaging by the non-scanning laser radar; a charting period can be greatly shortened; the cost is decreased; the mapping capacity of a zone which is severe in geographical environment is improved.

Owner:MIANYANG SKYEYE LASER TECH

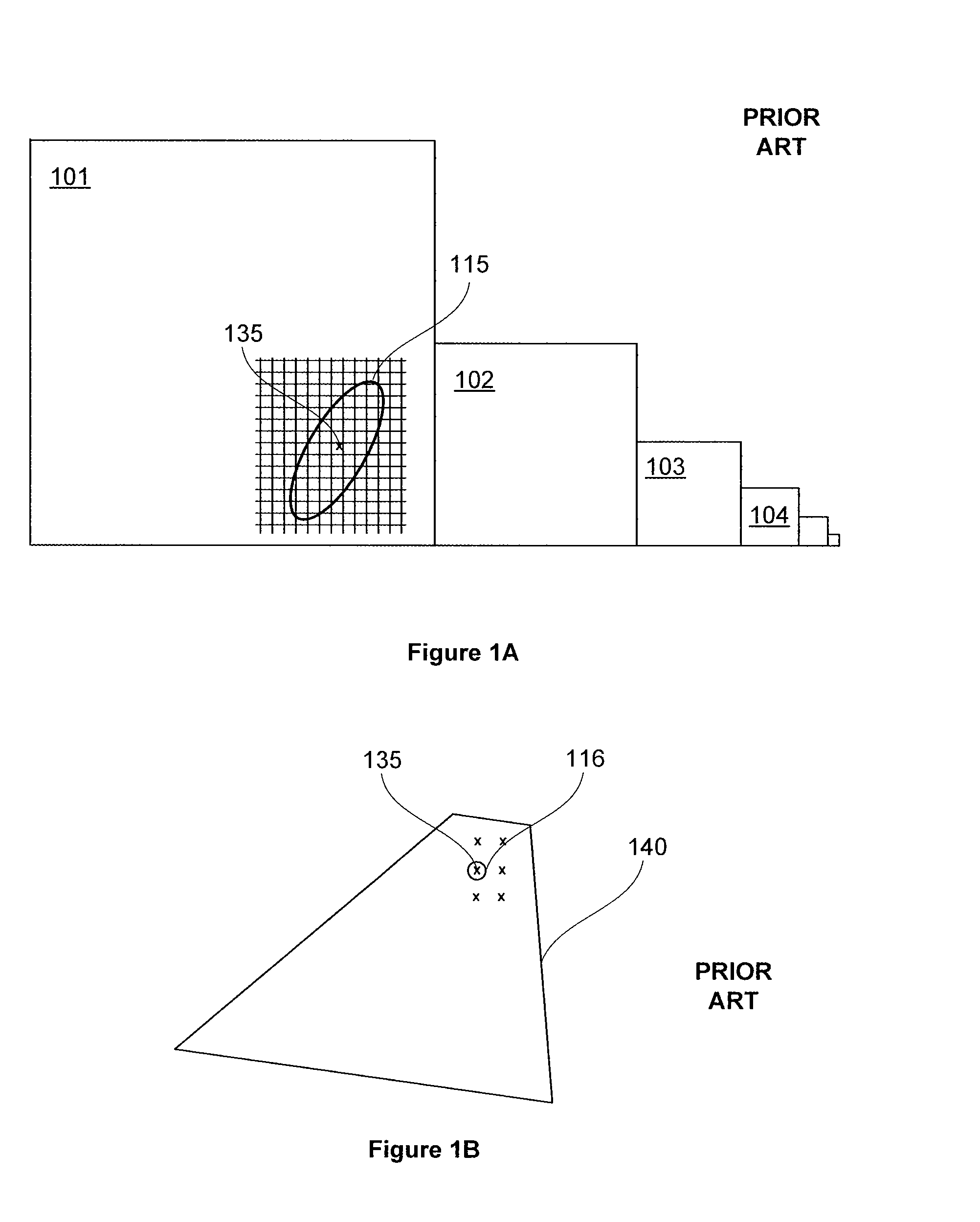

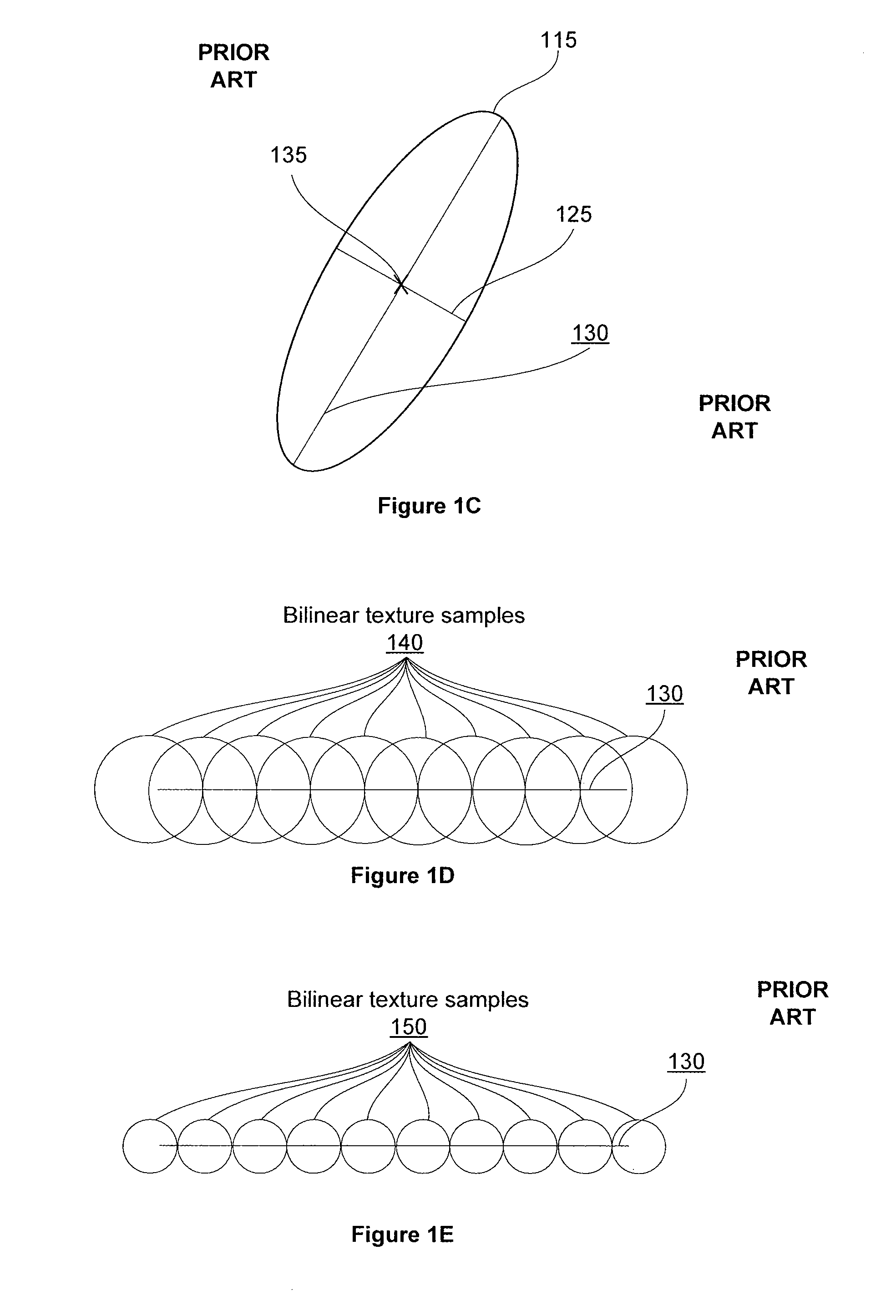

Anisotropic texture filtering with a modified number of texture samples

ActiveUS7372468B1Improve performanceReduce numberCathode-ray tube indicatorsImage generationTexture filteringComputer graphics (images)

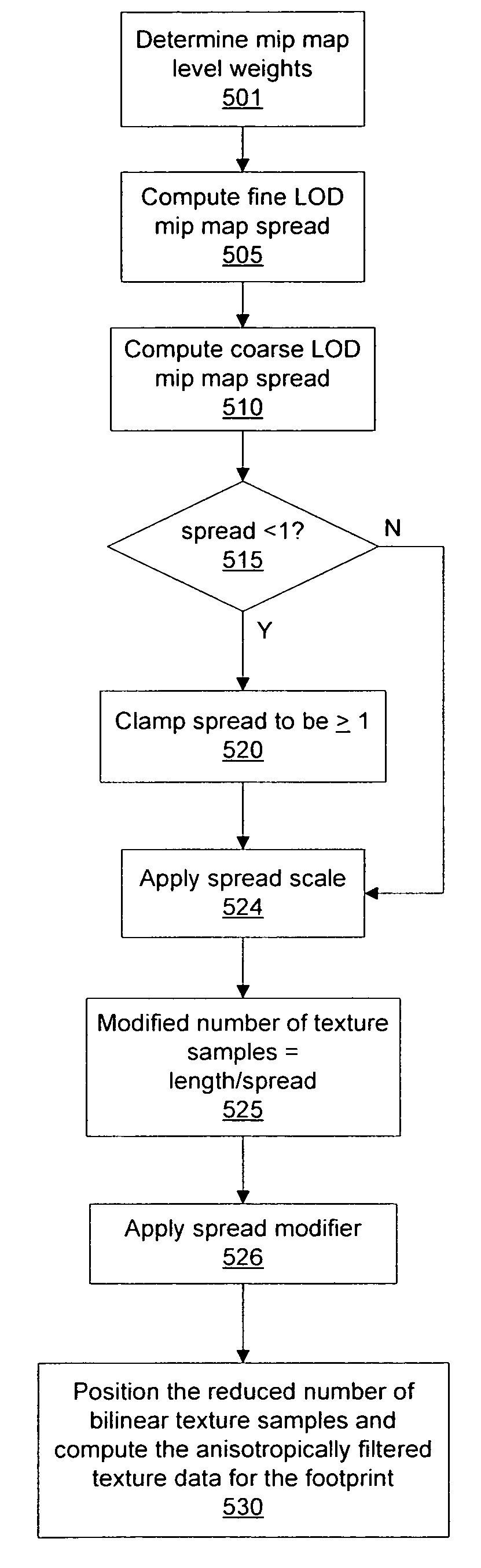

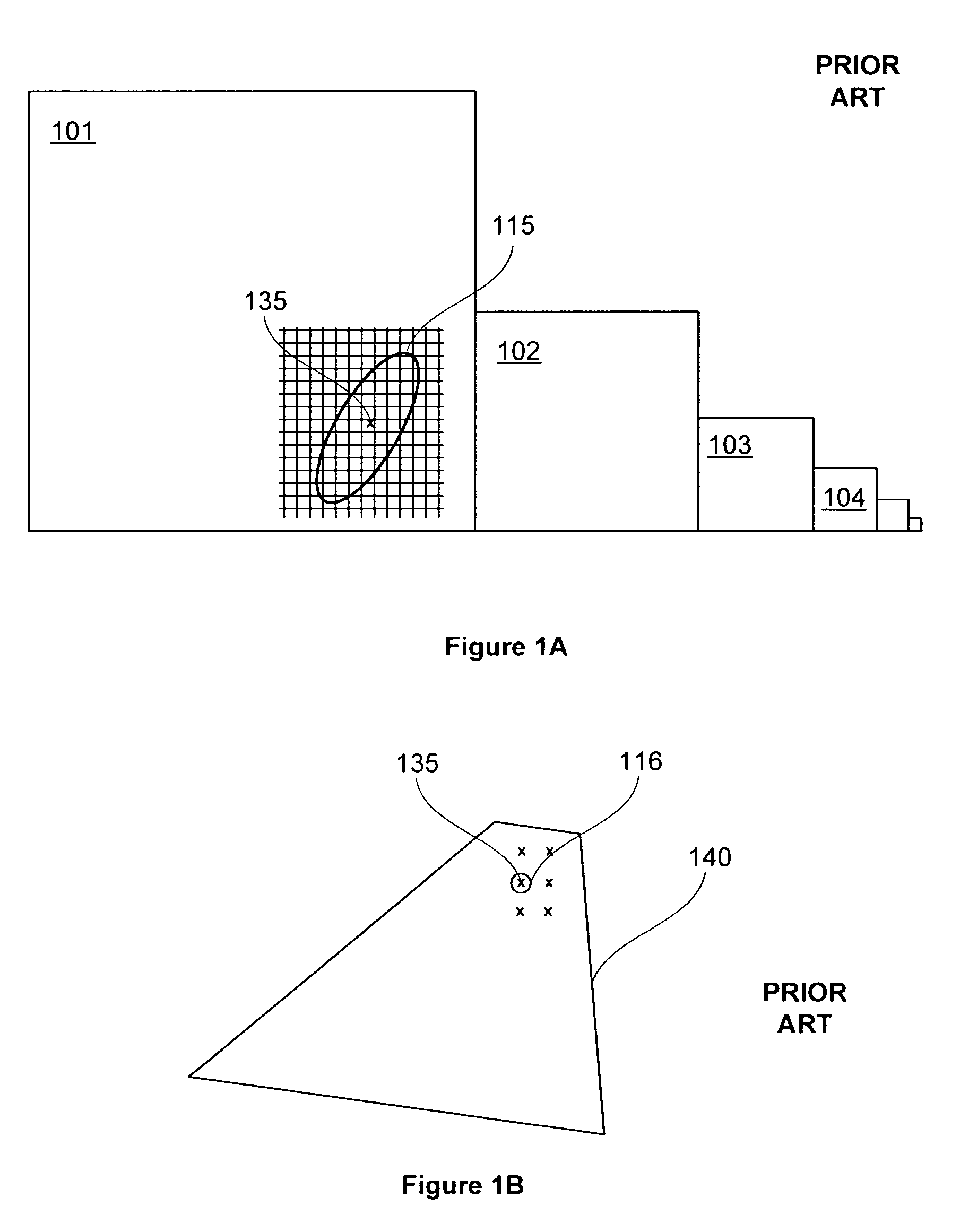

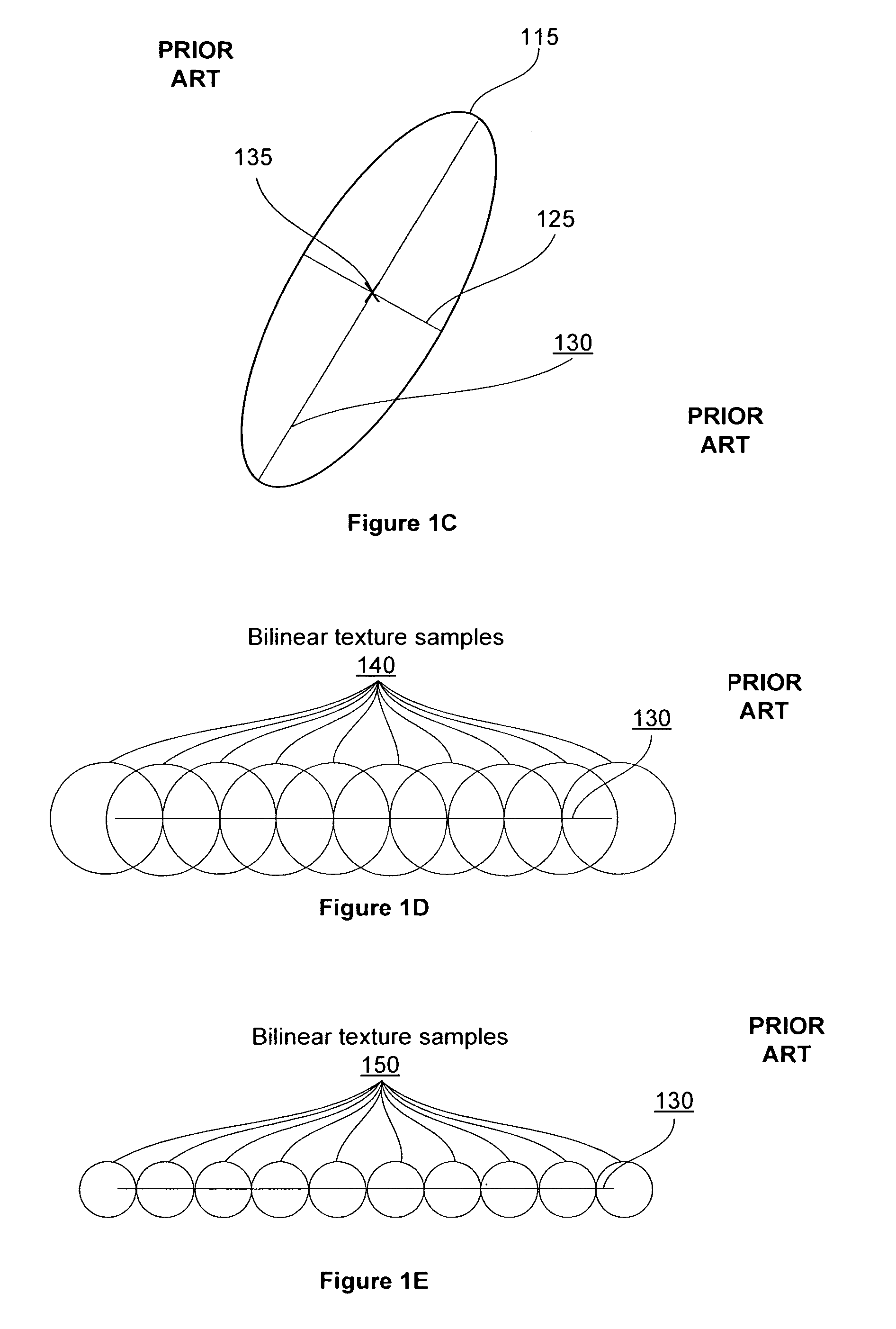

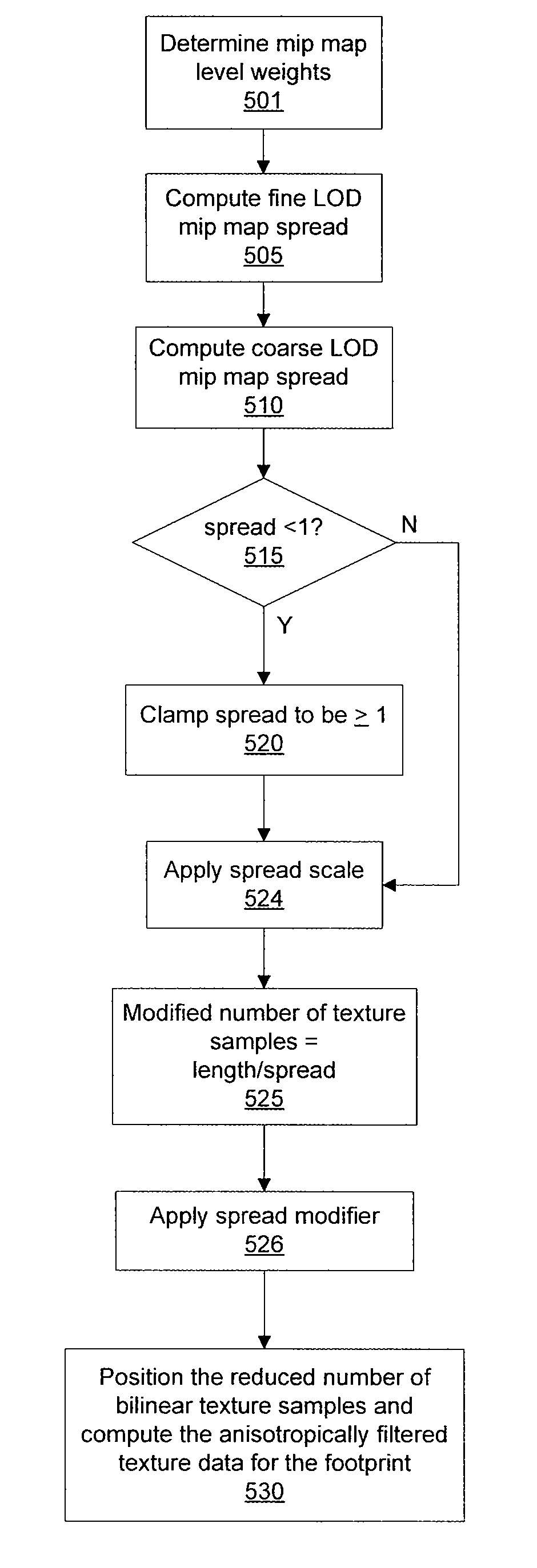

Systems and methods for modifying the number of texture samples used to produce an anisotropically filtered texture mapped pixel may improve texture mapping performance. When the number of texture samples is reduced, fewer texels are read and fewer filtering computations are needed to produce a texture value for an anisotropic footprint. The number of texture samples is reduced based on the mip map level weight. The number of texture samples may also be modified using specific parameters for the coarse and / or fine mip map levels. The spacing between the texture samples along the major axis of anisotropy may be modified to improve image quality or texture cache performance.

Owner:NVIDIA CORP

System and method for modifying a number of texture samples for anisotropic texture filtering

ActiveUS8068118B1Reduce in quantityImprove mapping abilityCathode-ray tube indicators3D-image renderingComputer graphics (images)Image quality

Systems and methods for modifying the number of texture samples used to produce an anisotropically filtered texture mapped pixel may improve texture mapping performance. When the number of texture samples is reduced, fewer texels are read and fewer filtering computations are needed to produce a texture value for an anisotropic footprint. The number of texture samples is reduced based on the mip map level weight. The number of texture samples may also be modified using specific parameters for the coarse and / or fine mip map levels. The spacing between the texture samples along the major axis of anisotropy may be modified to improve image quality or texture cache performance.

Owner:NVIDIA CORP

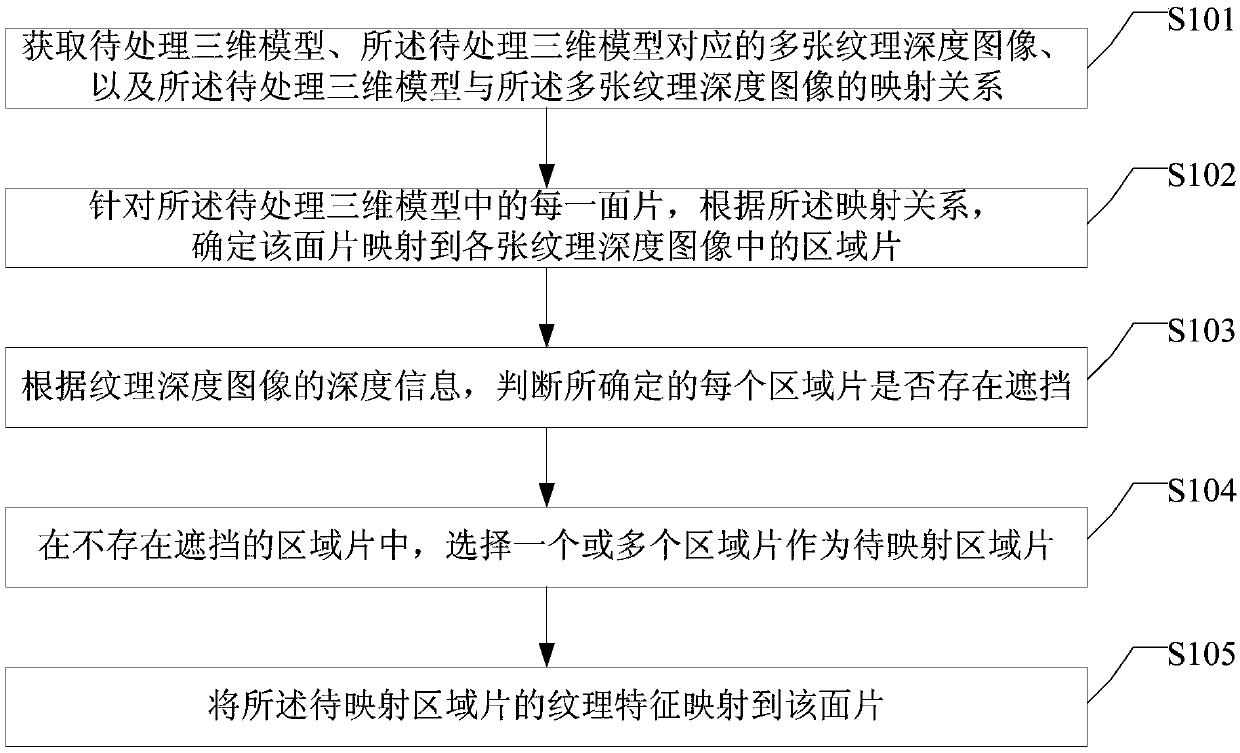

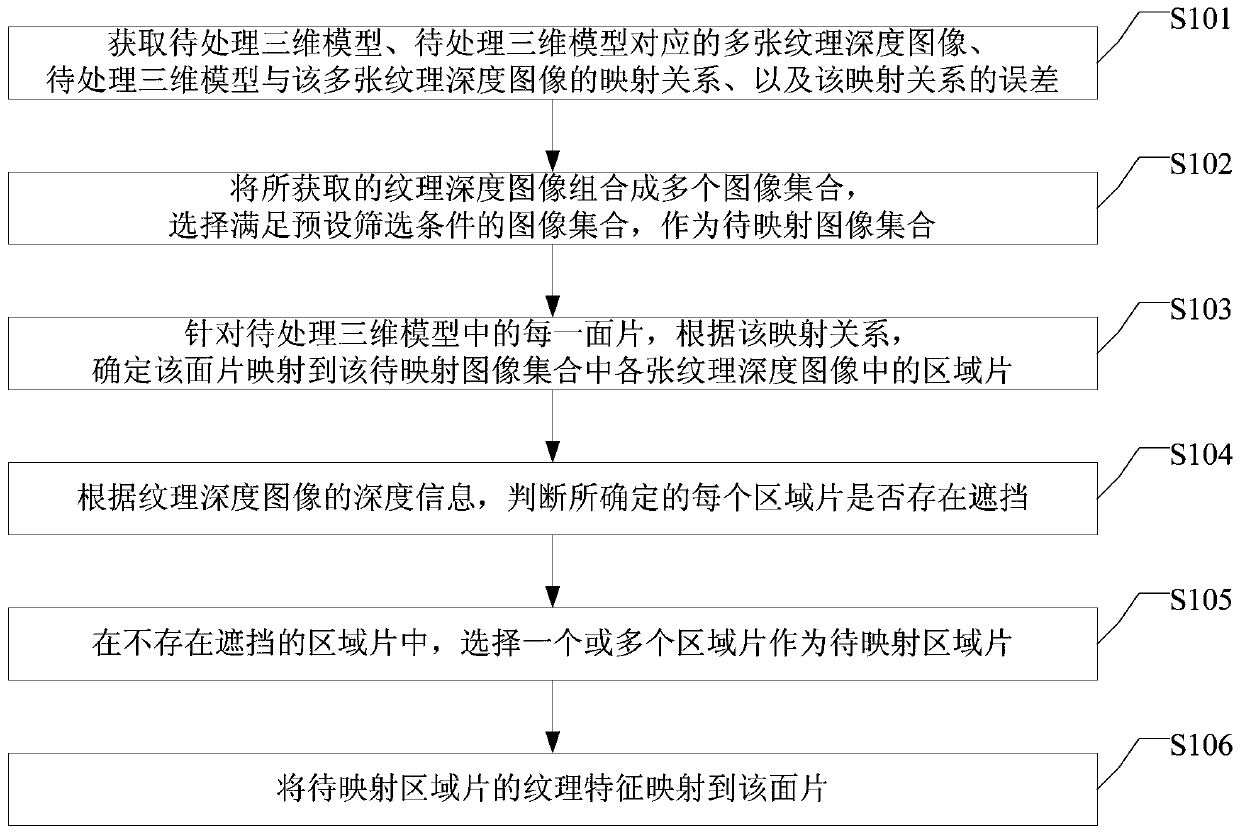

Texture mapping method, device and apparatus based on three-dimensional model

PendingCN110473294AImprove mapping abilityImage data processingInternal combustion piston enginesComputer visionFacet

The embodiment of the invention provides a texture mapping method, device and apparatus based on a three-dimensional model. The method comprises the following steps: for each patch in a three-dimensional model, determining an area patch mapped to a plurality of texture depth images by the patch, selecting the area patch without occlusion as an area patch to be mapped, and mapping texture featuresof the area patch to be mapped to the patch. In the scheme, the facets in the three-dimensional model are mapped by utilizing the texture features of the area patches without shielding in the texturedepth image, and the area patch corresponding to each facet is not shielded, so that the mapping effect is improved.

Owner:HANGZHOU HIKVISION DIGITAL TECH

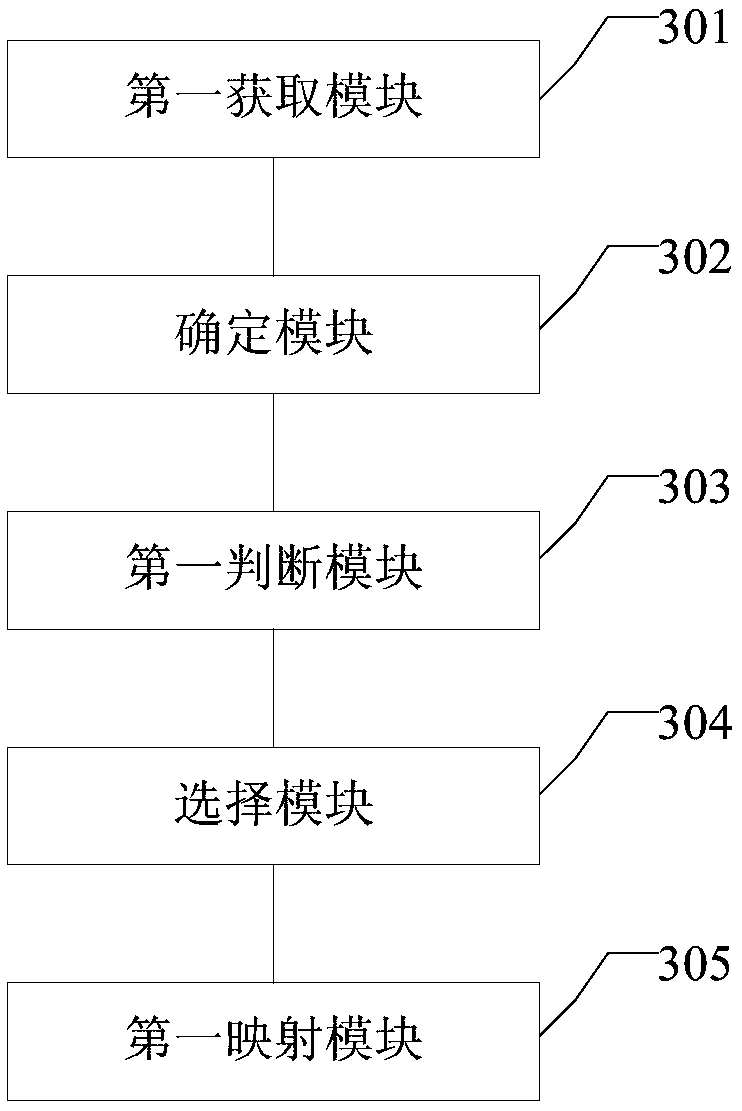

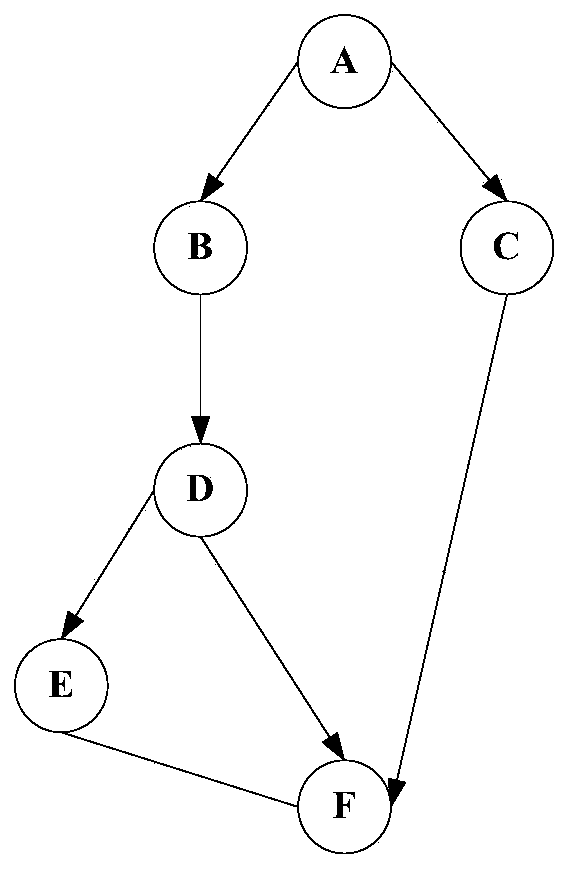

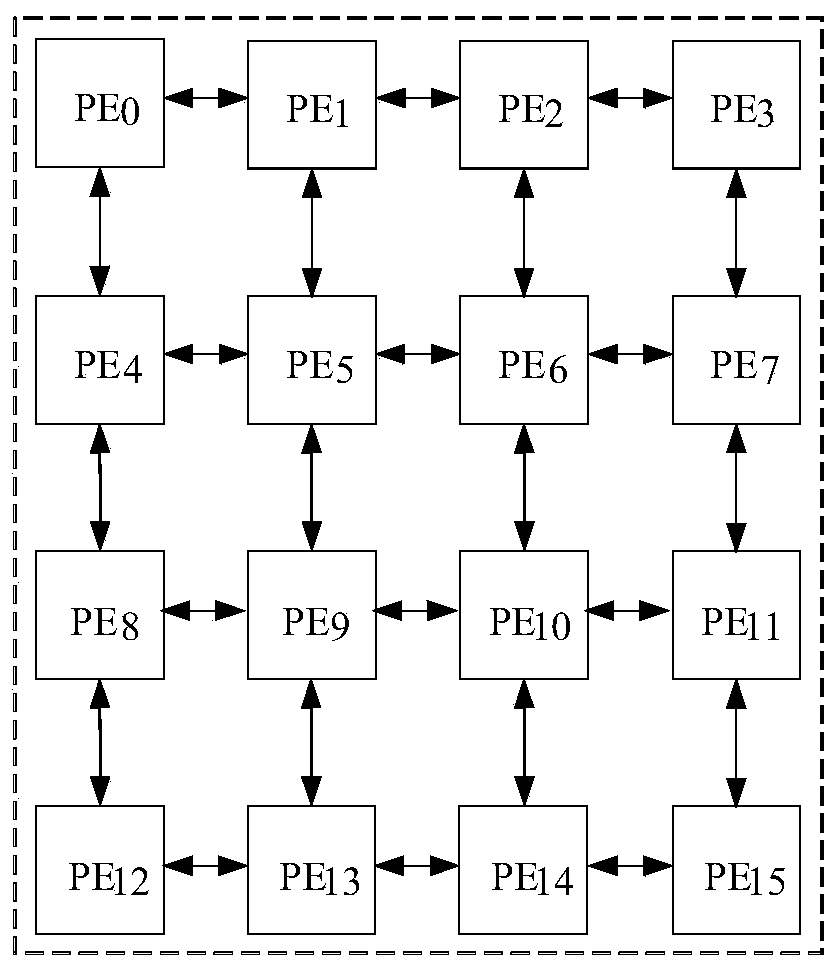

Mapping method and device for coarse-grained reconfigurable password logic array

ActiveCN110034920AImprove mapping abilityImprove efficiencyEncryption apparatus with shift registers/memoriesEnergy efficient computingRound complexityPassword

The invention provides a mapping method and a mapping device for a coarse-grained reconfigurable password logic array so as to simplify a mapping process. The coarse-grained reconfigurable password logic array comprises reconfigurable processing units PE which are fully interconnected; the method comprises the following steps: dividing operation nodes in a cryptographic algorithm data flow graph into a plurality of operation clusters; taking PE in the coarse-grained reconfigurable password logic array as an ant node, and calculating by using an ant colony algorithm to obtain an optimal mappingpath between the coarse-grained reconfigurable password logic array and an operation cluster; wherein each PE in the optimal mapping path is mapped with one operation cluster. Visibly, in the embodiment of the invention, the cryptographic algorithm data flow graph is divided in advance, and then mapping is performed based on the operation cluster, so that the mapping granularity of the cryptographic algorithm data flow graph is increased, and the algorithm mapping complexity is correspondingly reduced. Meanwhile, the mapping between the coarse-grained reconfigurable password logic array and the operation cluster is completed by adopting an ant colony algorithm, the mapping convergence process can be accelerated, and the mapping performance and efficiency are improved.

Owner:PLA STRATEGIC SUPPORT FORCE INFORMATION ENG UNIV PLA SSF IEU

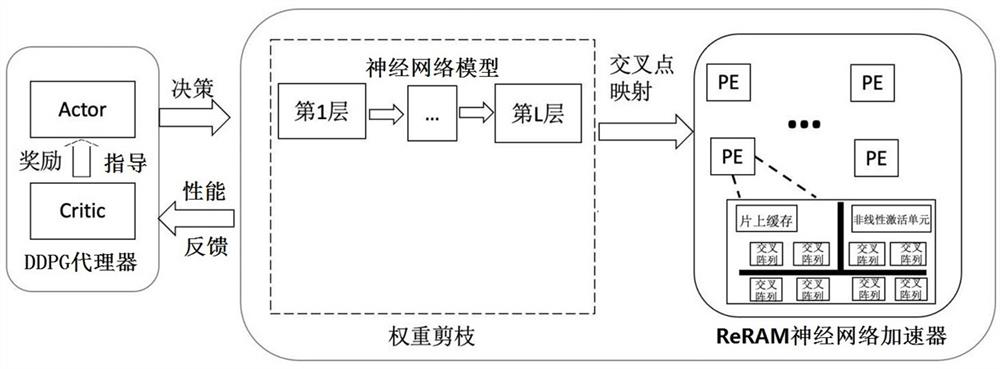

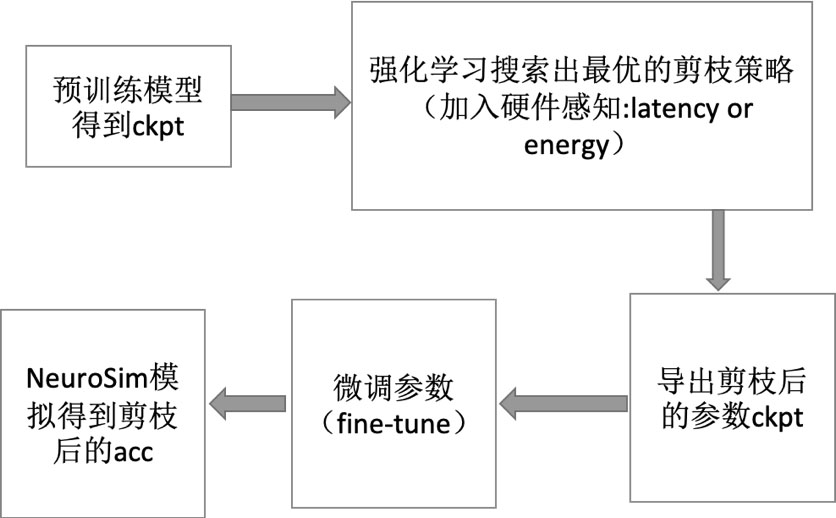

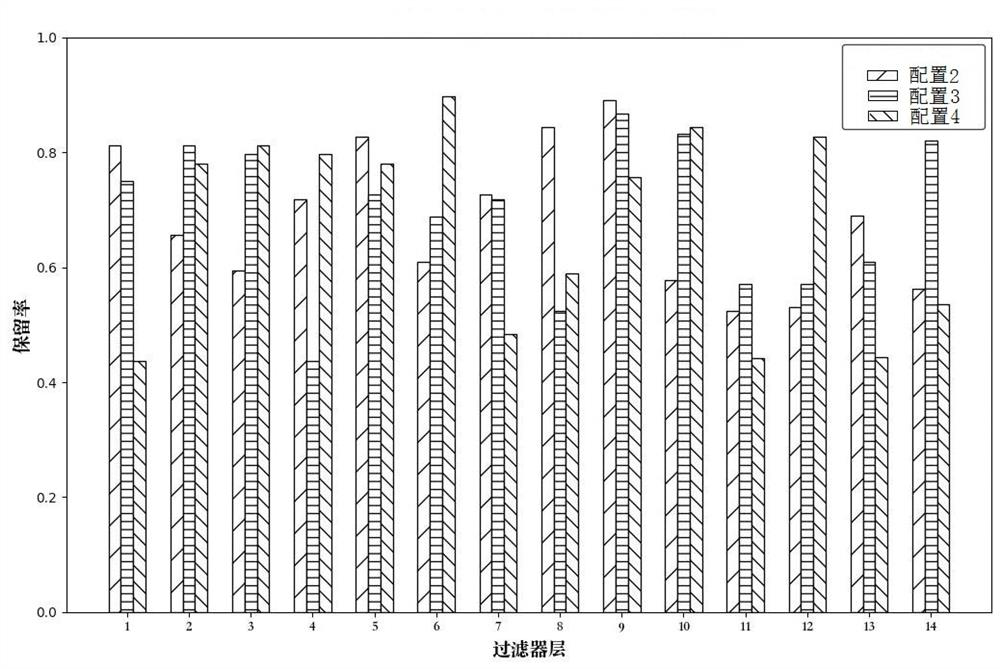

Adjustable hardware aware pruning and mapping framework based on ReRAM neural network accelerator

The invention provides an adjustable hardware perception pruning and mapping framework based on a ReRAM neural network accelerator. The pruning and mapping framework comprises a DDPG agent and the ReRAM neural network accelerator. The DDPG agent is composed of a behavior decision module Actor and an evaluation module Critic, and the behavior decision module Actor is used for making a pruning decision for the neural network; the ReRAM neural network accelerator is used for mapping a model formed under a pruning decision generated by the behavior decision module Actor, and feeding back a performance parameter mapped by the model under the pruning decision to the evaluation module Critic as a signal; the performance parameters comprise energy consumption, delay and model accuracy of the simulator; the judgment module Critic updates a reward function value according to the fed back performance parameters and guides a pruning decision of the behavior decision module Actor in the next stage;according to the method, a pruning scheme which is most matched with hardware and user requirements and is most efficient is made by utilizing a reinforcement learning DDPG agent, so that the delay performance and the energy consumption performance on the hardware are improved while the accuracy is ensured.

Owner:ZHEJIANG LAB +1

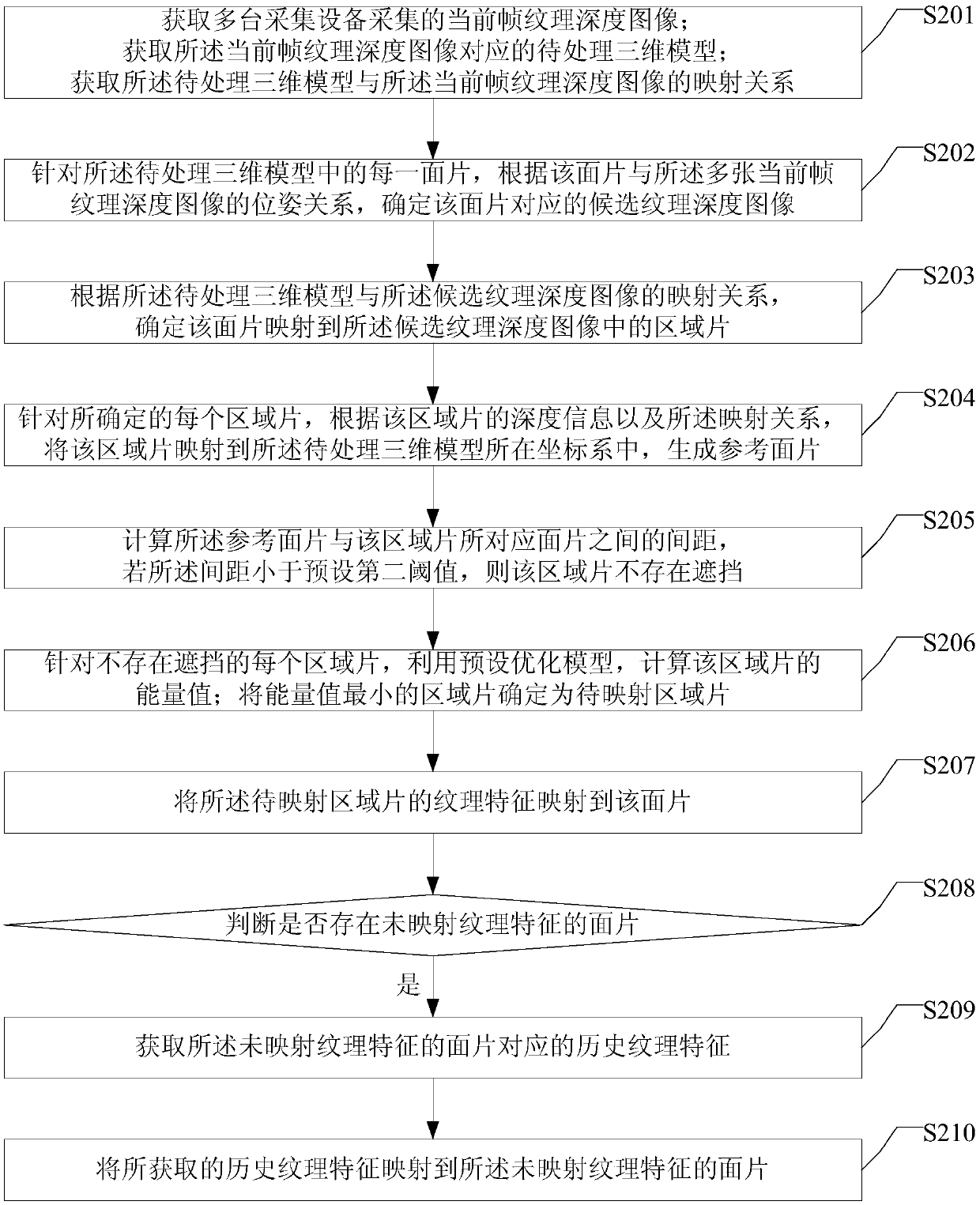

Texture mapping method, device and equipment based on three-dimensional model

PendingCN111369659ASmall mapping errorImprove mapping ability3D-image renderingInternal combustion piston enginesThree dimensional modelDepth map

The embodiment of the invention provides a texture mapping method, device and equipment based on a three-dimensional model. The method comprises the following steps: selecting a to-be-mapped image setfrom the acquired texture depth images, for each patch in the three-dimensional model, determining an area patch mapped to each texture depth image in the to-be-mapped image set by the patch, selecting the area patch without occlusion as a to-be-mapped area patch, and mapping texture features of the to-be-mapped area patch to the patch; visibly, in the scheme, in the first aspect, the facets in the three-dimensional model are mapped by using the texture features of the area patches without occlusion in the texture depth image, and the area patch corresponding to each facet is not occluded, sothat the mapping effect is improved; and on the other hand, the sum of the errors of the mapping relationships corresponding to the texture depth images in the selected to-be-mapped image set meets apreset error condition, and the mapping error of the region pieces determined in the to-be-mapped image set is relatively small, so that the mapping effect is further improved.

Owner:HANGZHOU HIKVISION DIGITAL TECH

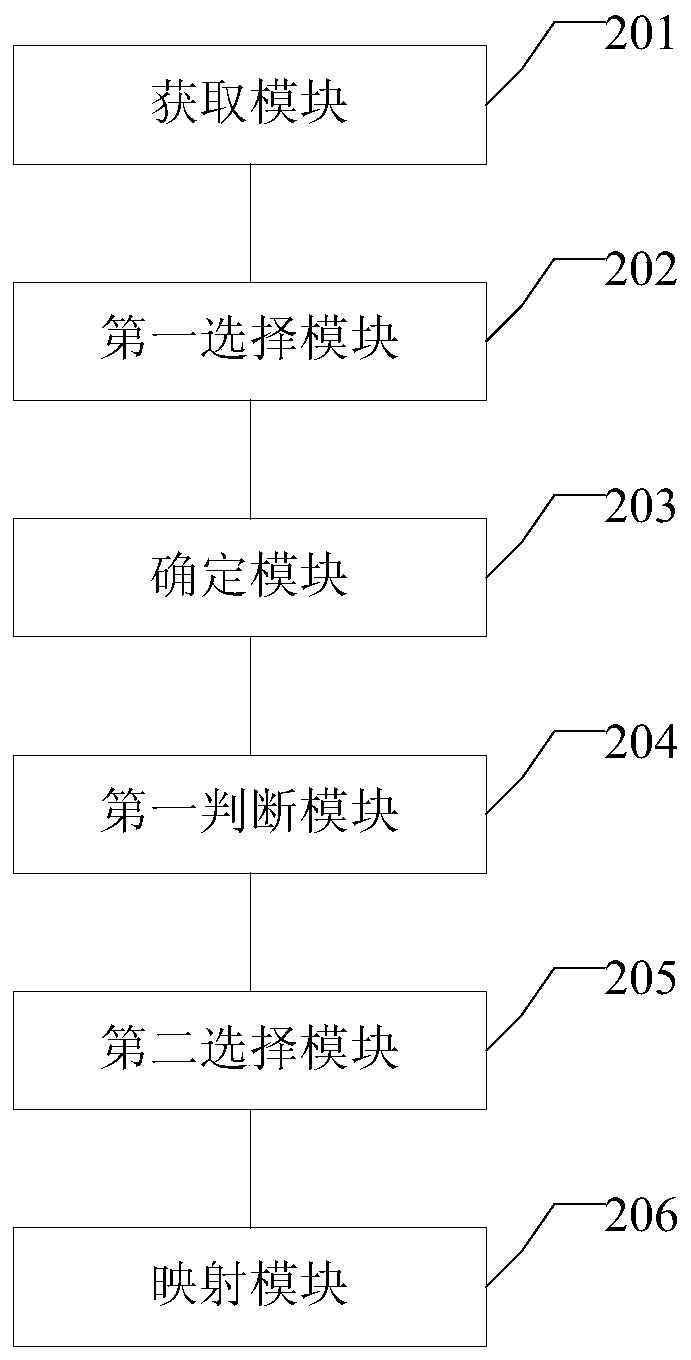

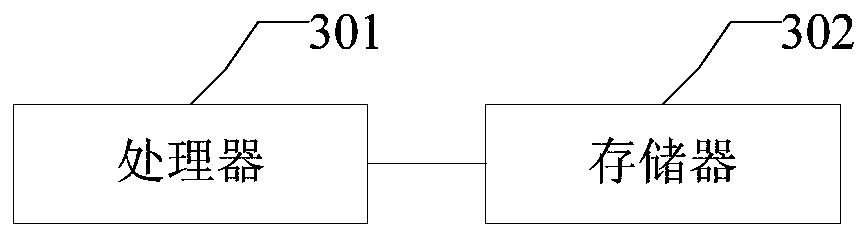

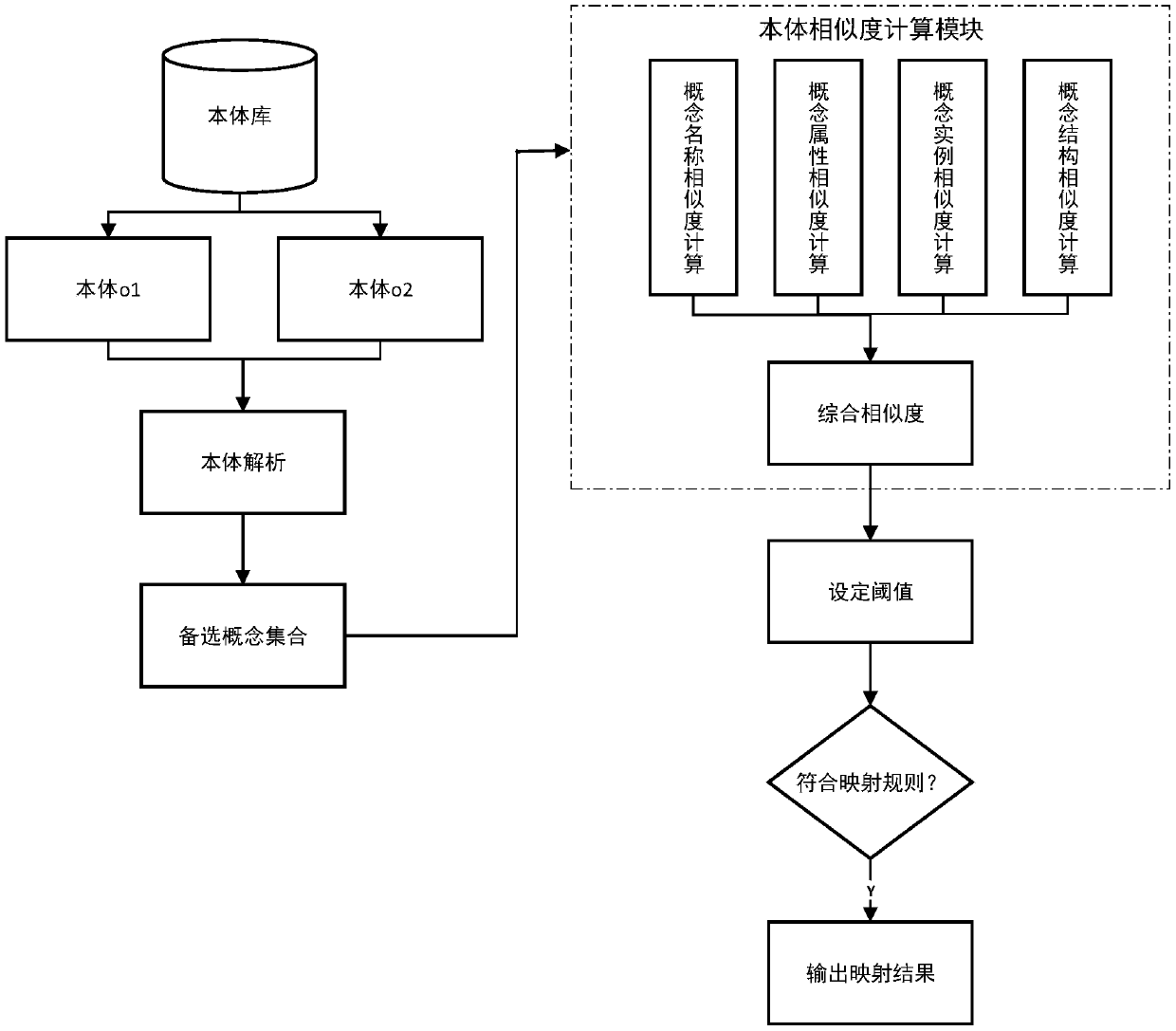

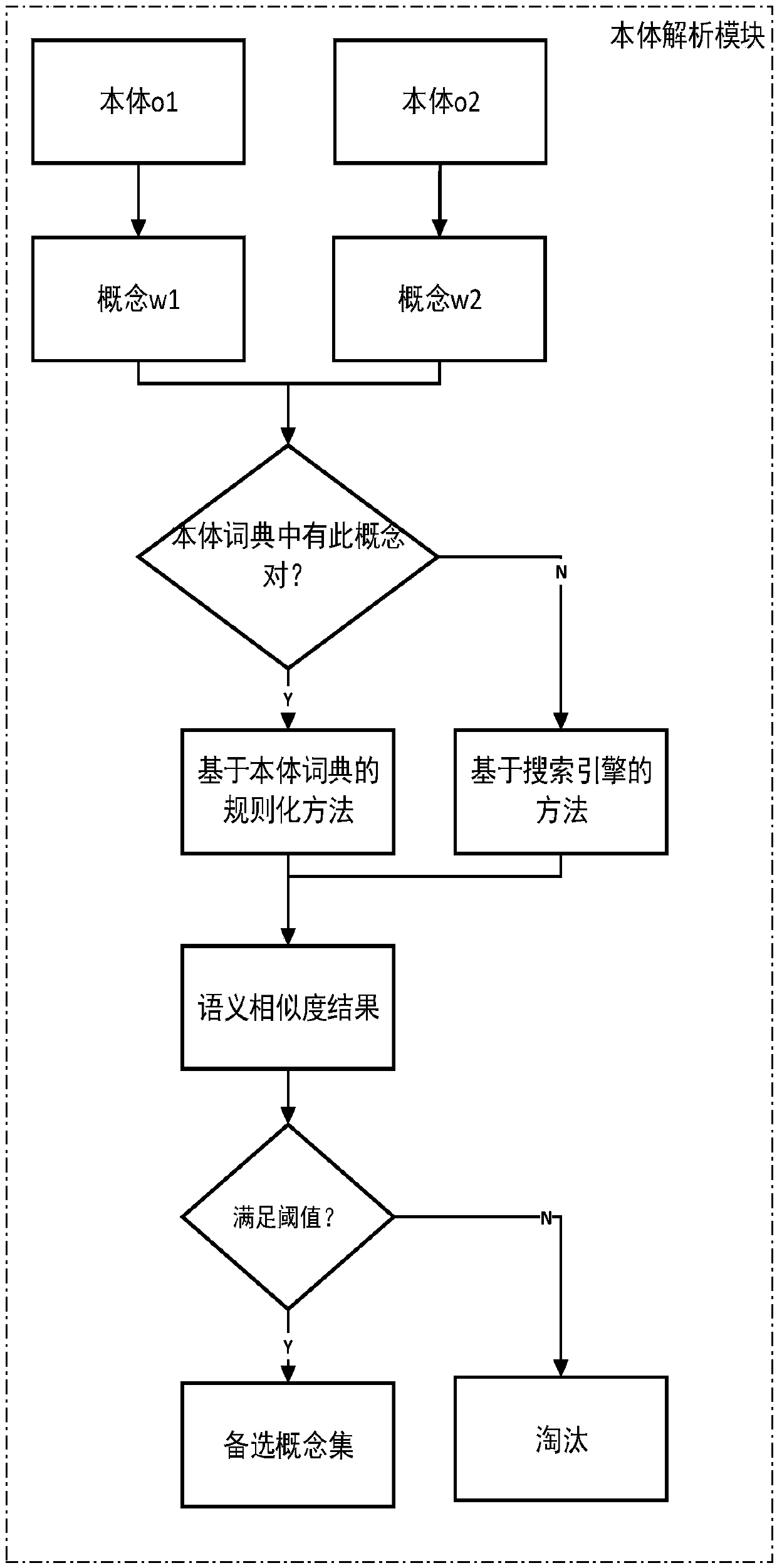

Robot data interoperation domain ontology mapping method based on semantic similarity

PendingCN109543189AReduce workloadImprove work efficiencyWeb data indexingSemantic analysisKey issuesWorkload

The invention claims a robot data interoperation domain ontology mapping method based on semantic similarity, which comprises the steps of analyzing matching concept pairs of the ontology, screening out an alternative concept set according to semantic similarity, calculating the comprehensive similarity of the concept pairs, and outputting a mapping result. This method solves the key problem of data interoperability of heterogeneous robot systems with ontology theory, that is, how to find the mapping relationship between ontologies. This method is mainly applied to data interoperability in manufacturing heterogeneous systems, complete the mapping of robot domain ontology, Compared with the traditional manual method, the ontology mapping construction process is more convenient and quick, the workload of mapping process is reduced, and the expansibility and stability of the ontology in the robot domain can be improved.

Owner:CHONGQING UNIV OF POSTS & TELECOMM +1

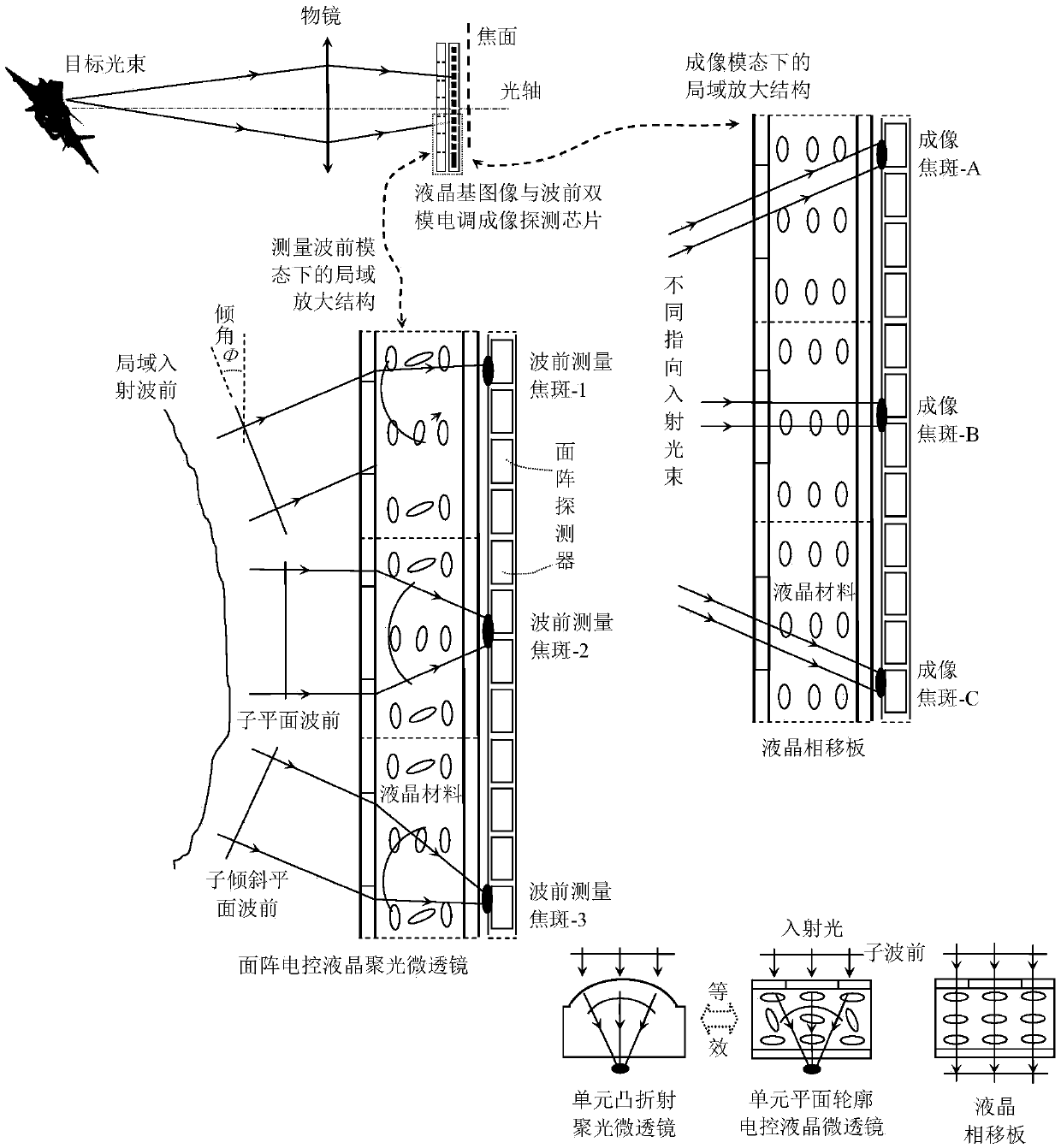

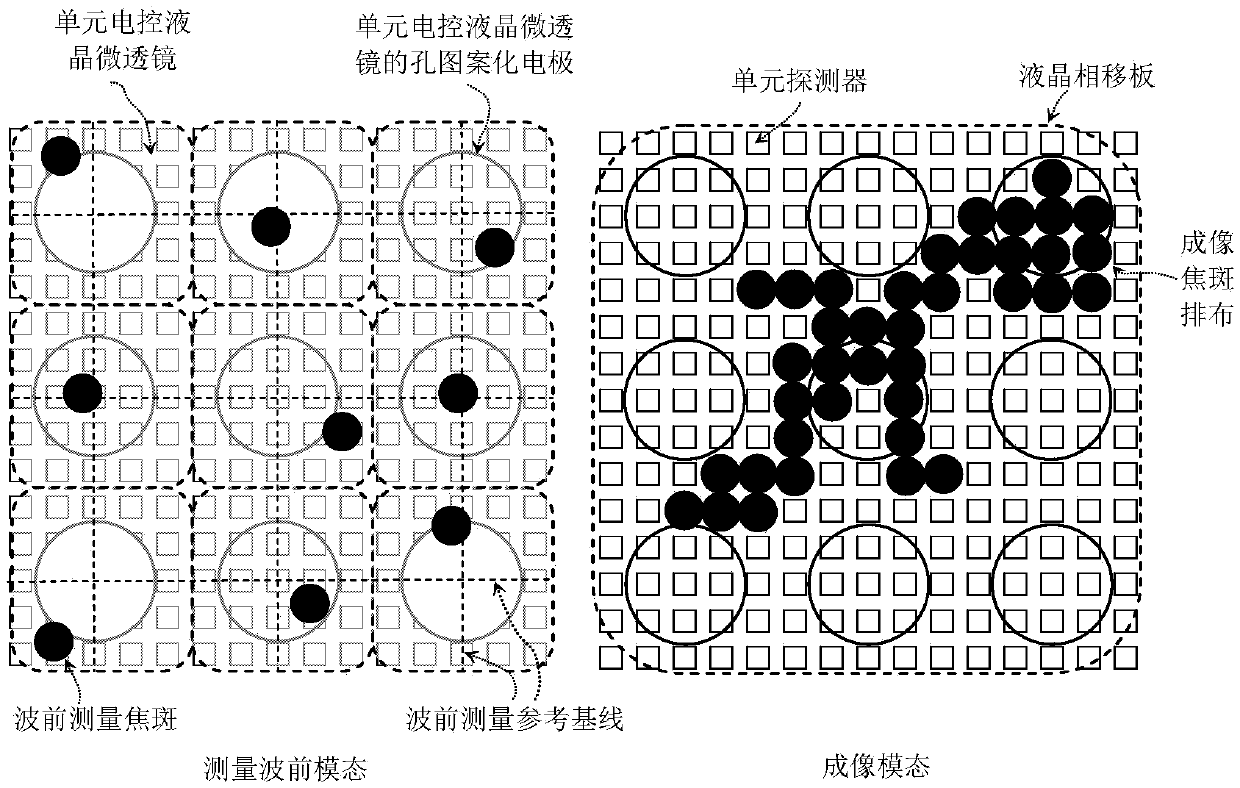

Liquid crystal base image and wavefront dual-mode electrical-modulation imaging detection chip

ActiveCN105509894AAchieving Timing CompatibilityWavefront measurement with adjustable line-of-sightRadiation pyrometryImaging qualityDual mode

The invention discloses a liquid crystal base image and wavefront dual-mode electrical-modulation imaging detection chip, and the chip comprises a liquid crystal micro-optical structure, an area-array visible-light detector and a drive control preprocessing module; the liquid crystal micro-optical structure is an area-array electronic control liquid crystal micro lens under a sequential power-up state; the area-array visible-light detector is divided into a plurality of sub-area array visible-light detectors by the area-array electronic control liquid crystal micro lens according to the array size thereof, and each unit of the electronic control liquid crystal micro lens matches one sub-area array visible-light detector to form a wavefront measurement mode; the liquid crystal micro-optical structure is a liquid crystal phase plate for delaying an incident wave beam under a sequential power-off state, and the liquid crystal phase plate and the area-array visible-light detector form an imaging mode. According to the invention, the chip can capture the emerging wavefront and a high image quality flat image of a target based on a sequential electric signal, the detection efficiency is high, the chip is easy to use and couple with a conventional imaging optical system.

Owner:HUAZHONG UNIV OF SCI & TECH

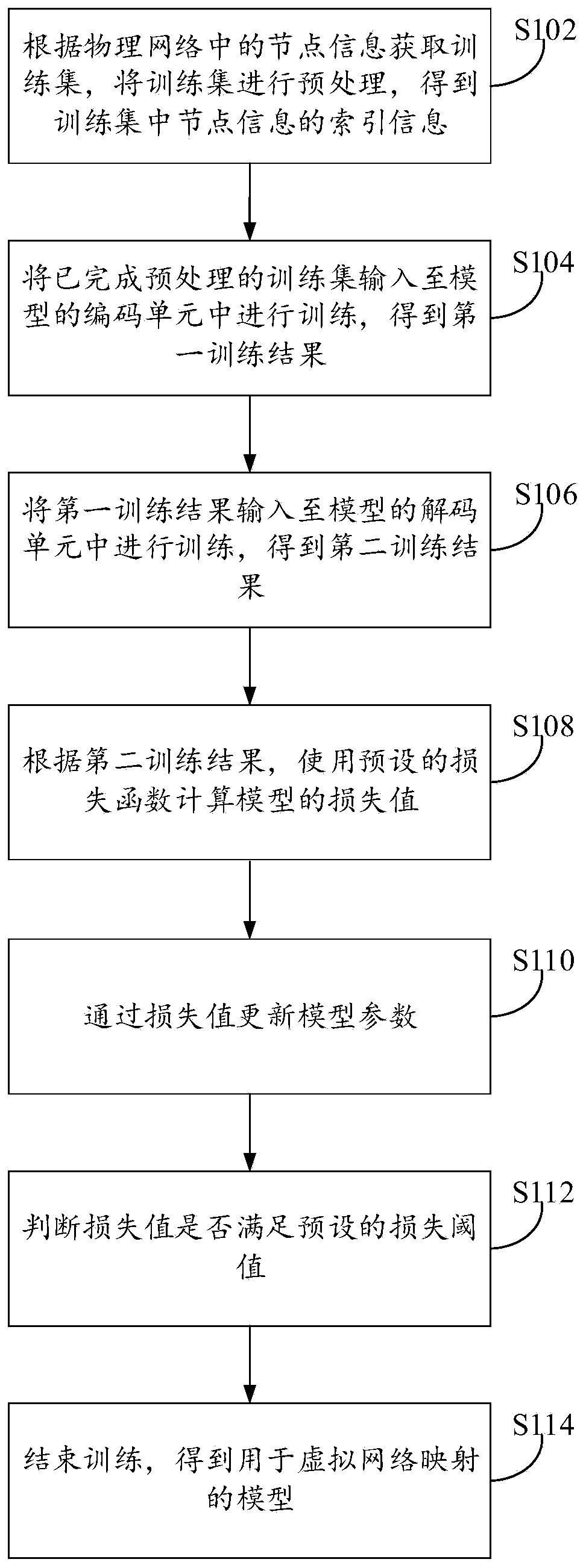

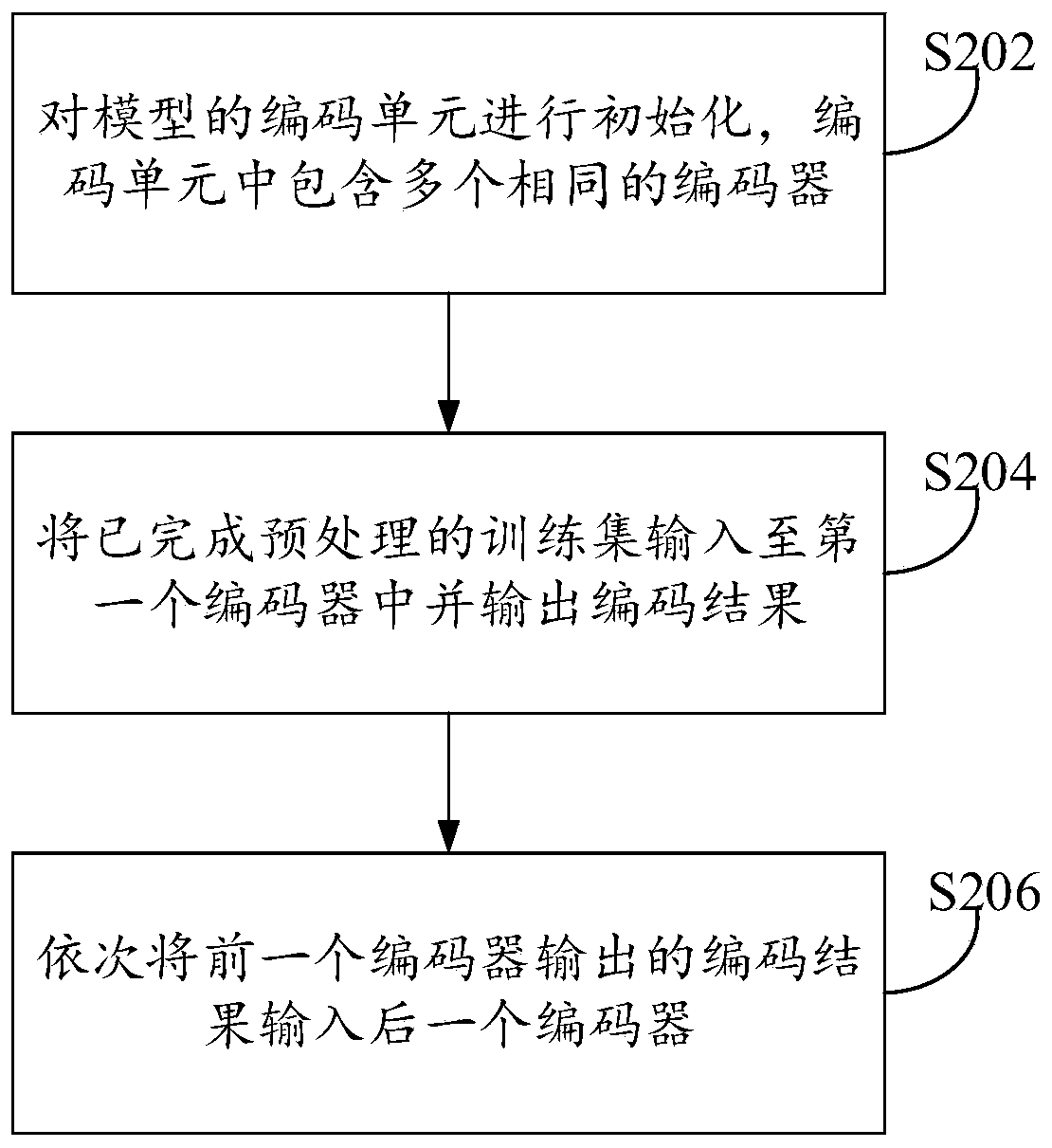

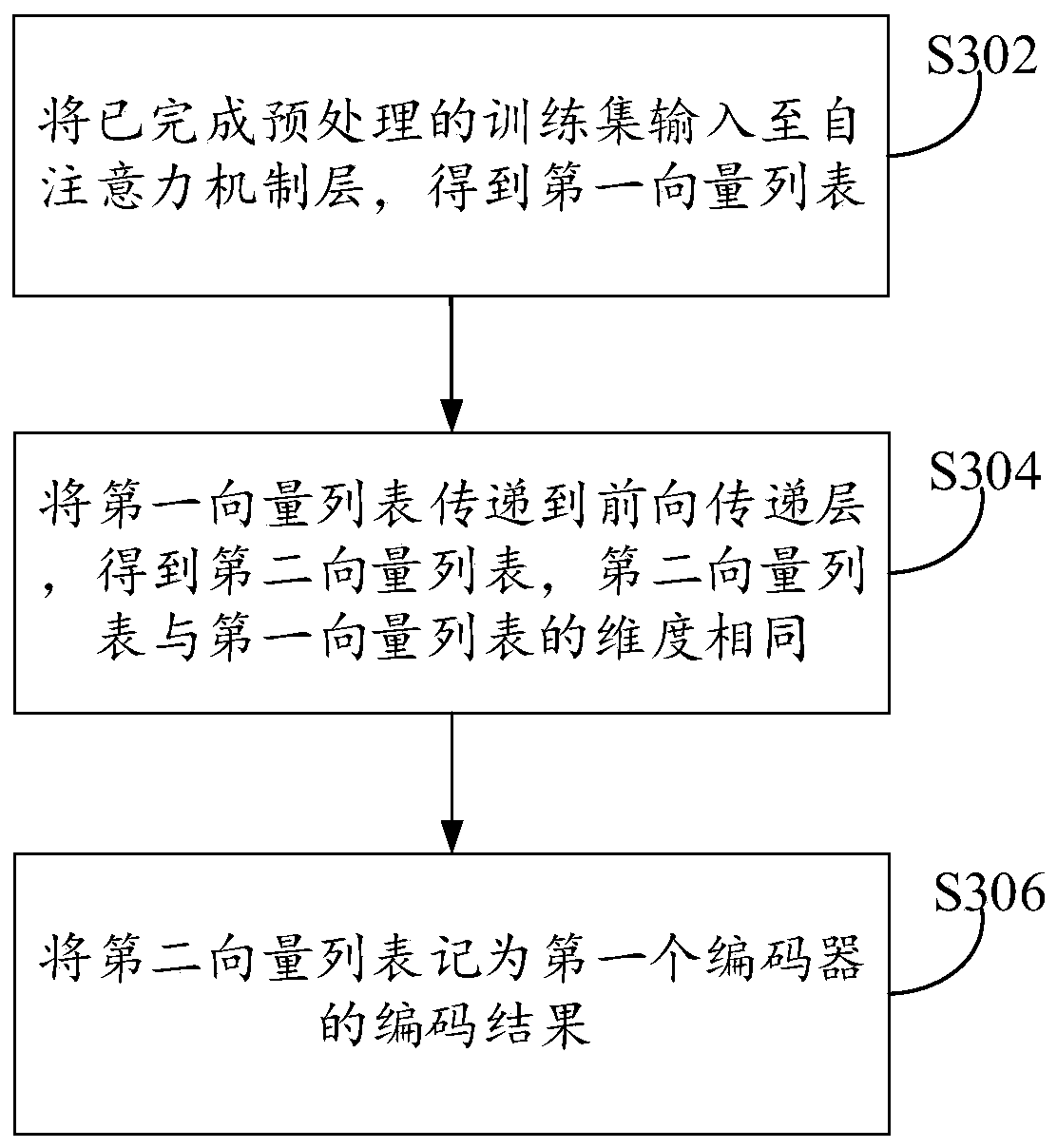

Virtual network mapping method and model training method and device thereof

ActiveCN110890985AImprove mapping abilityData switching networksNeural learning methodsReinforcement learning algorithmEngineering

The invention provides a virtual network mapping method and a model training method and device thereof, and the model training method comprises the steps: obtaining a training set according to the node information in a physical network, preprocessing the training set, and obtaining index information of the node information in the training set; inputting a preprocessed training set into a coding unit of a model for training to obtain a first training result; inputting the first training result into a decoding unit of the model for training to obtain a second training result; calculating a lossvalue of the model by using a preset loss function according to the second training result; updating model parameters through the loss value; judging whether the loss value meets a preset loss threshold value or not; if yes, training is ended, and a model used for virtual network mapping is obtained. Through the plurality of encoders in the encoding unit and the plurality of decoders in the decoding unit and by adopting a reinforcement learning algorithm for training, the mapping effect of the model on the virtual network is improved.

Owner:BEIJING UNIV OF POSTS & TELECOMM

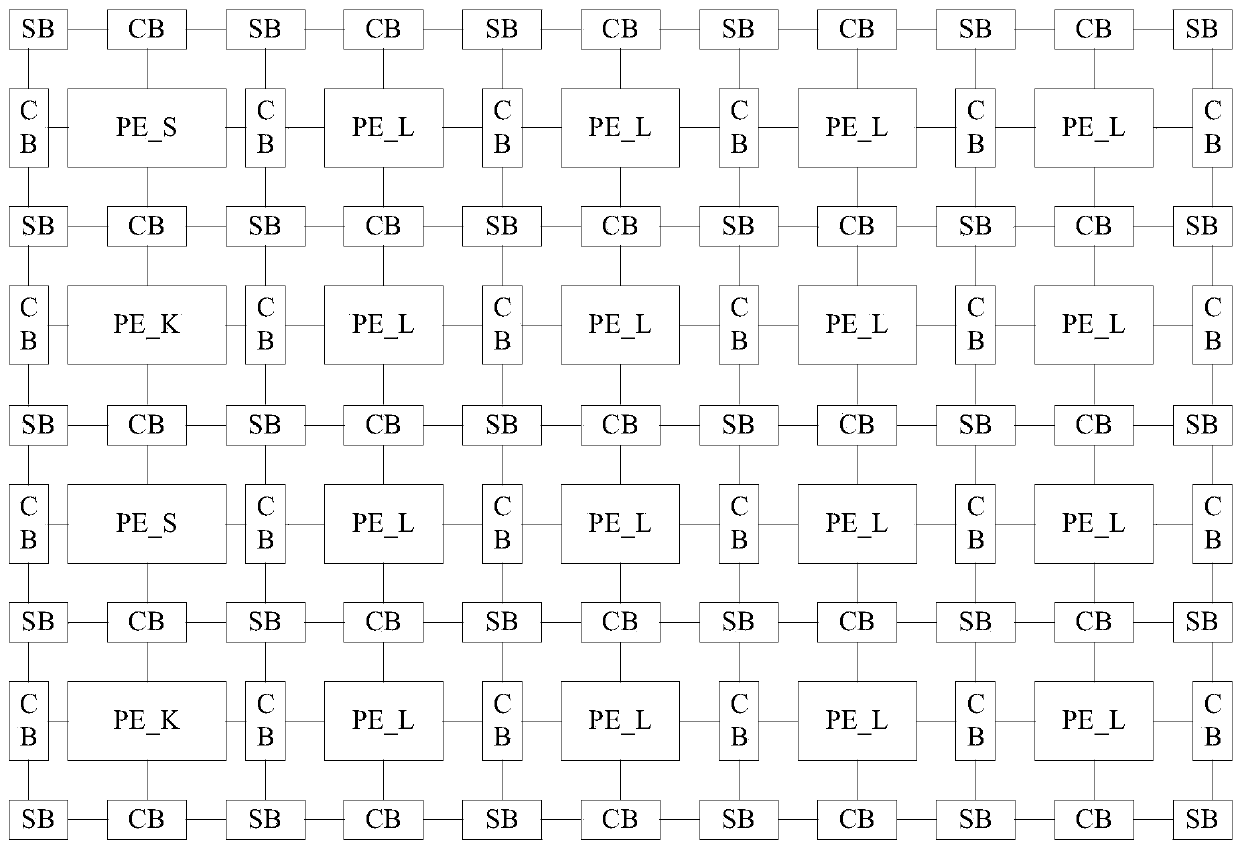

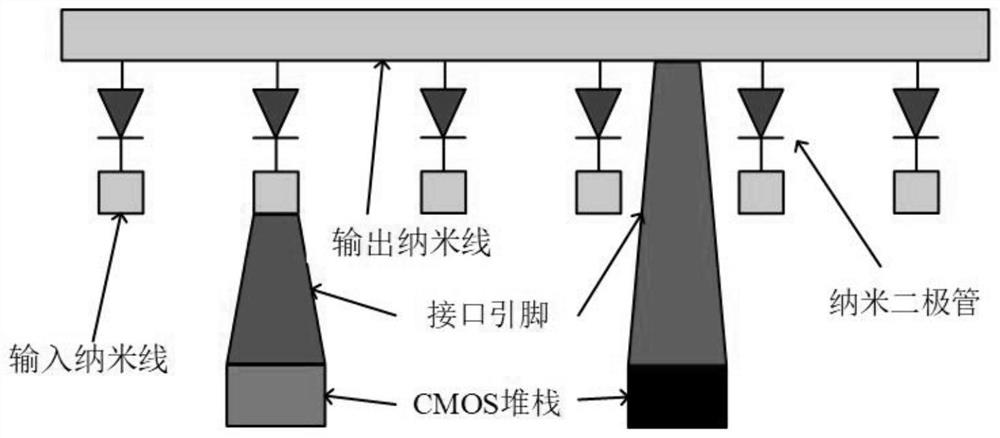

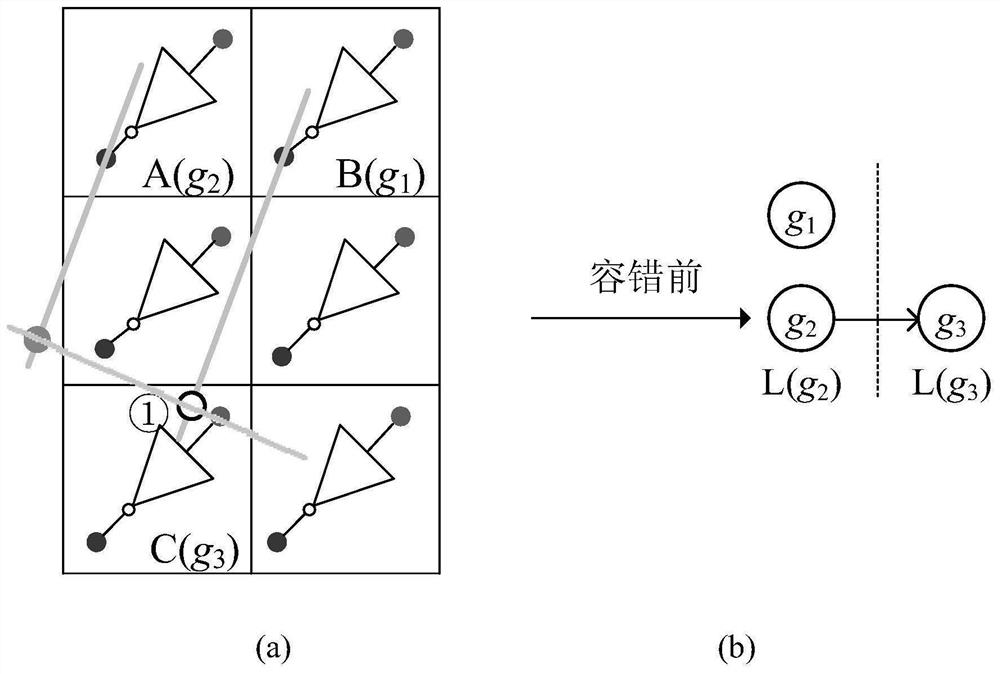

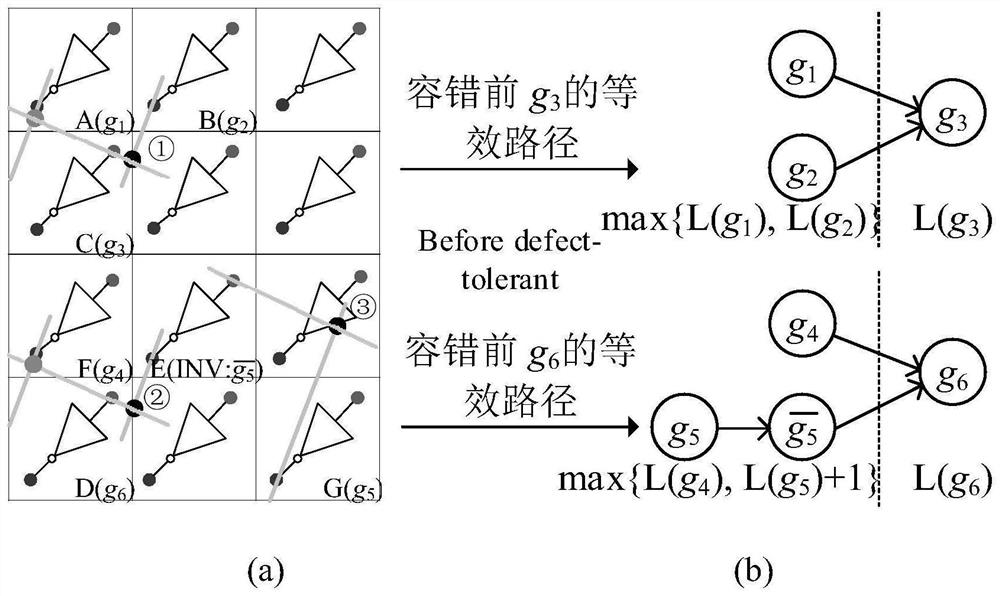

Nano CMOS circuit fault-tolerant mapping method capable of optimizing time delay

PendingCN112214946AImprove mapping abilityBig spaceSpecial data processing applicationsCAD with nanotechnologyTime delaysHemt circuits

The invention discloses a nano CMOS (Complementary Metal Oxide Semiconductor) circuit fault-tolerant mapping method capable of optimizing time delay, and aims to solve the problems of poor time delayperformance, poor solving speed, poor quality and the like in a nano CMOS circuit for realizing a correct logic function by adopting an existing fault-tolerant mapping method. Under the mapping constraints of defective nano CMOS circuit, the invention provides a nano CMOS circuit fault-tolerant mapping method capable of optimizing time delay. According to the fault-tolerant mapping method, the mapping process of a traditional nano CMOS circuit is optimized, the dividing technology of a logic level to a logic circuit to be mapped and the physical-level pre-planning technology with original input as an object are newly added, and the logic circuit is mapped by taking a path tree as a unit. Two mapping modes are adopted to be mapped into a pre-planned area in the nano CMOS circuit to optimizeeach path delay, the mapping success rate is improved by searching available defect units, and the delay performance of the delay mapping circuit is optimized on the basis of quickly eliminating theinfluence of defects on the logic function of the nano CMOS circuit.

Owner:NINGBO UNIV

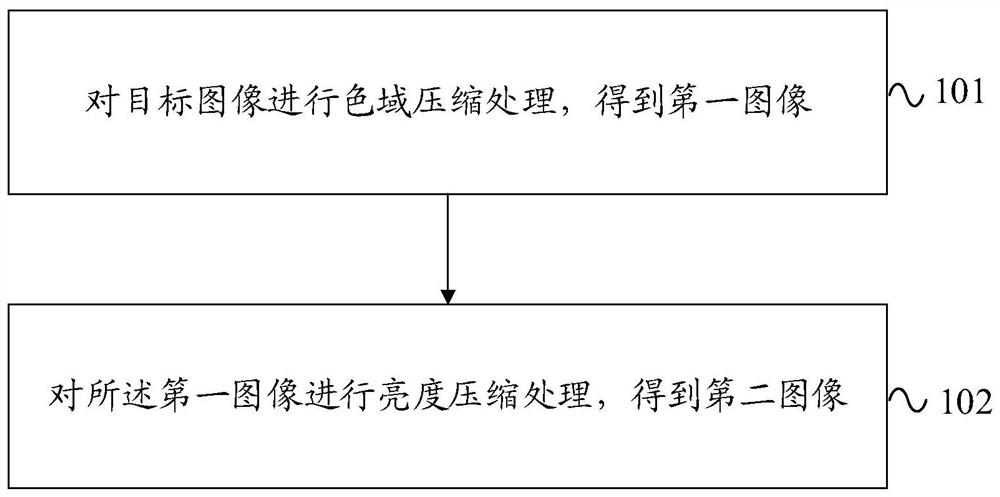

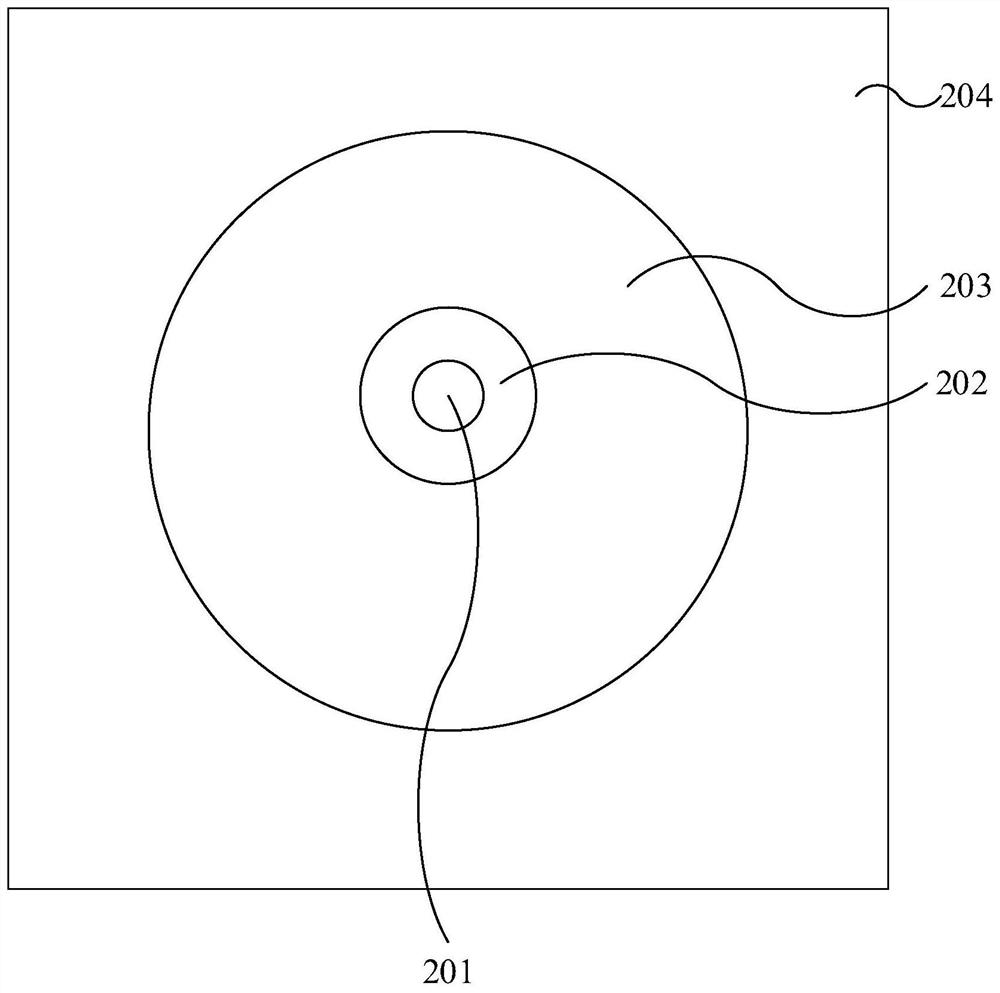

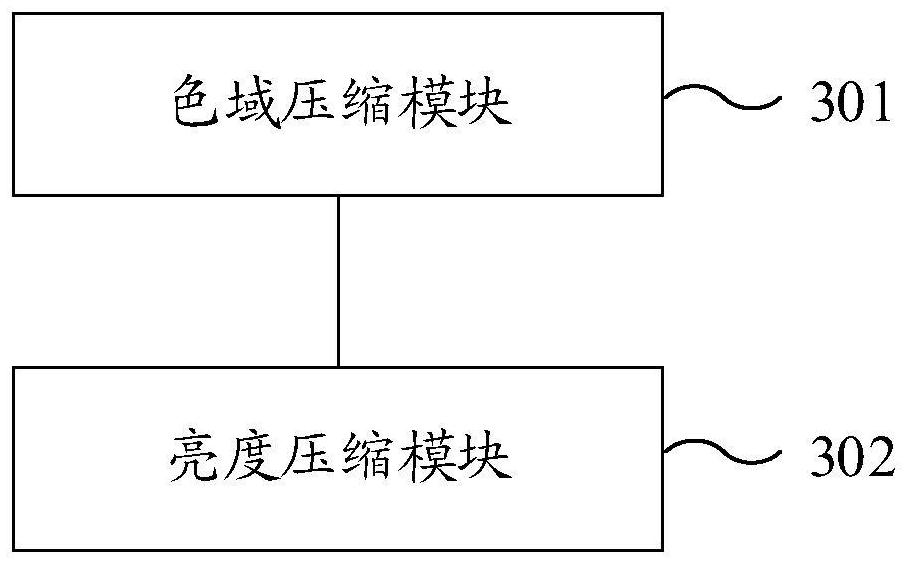

Image tone mapping method and device, electronic equipment and storage medium

PendingCN113132696AImprove accuracyImprove the effectBrightness and chrominance signal processing circuitsPicture signal generatorsComputer graphics (images)Image processing

Owner:VIVO MOBILE COMM CO LTD

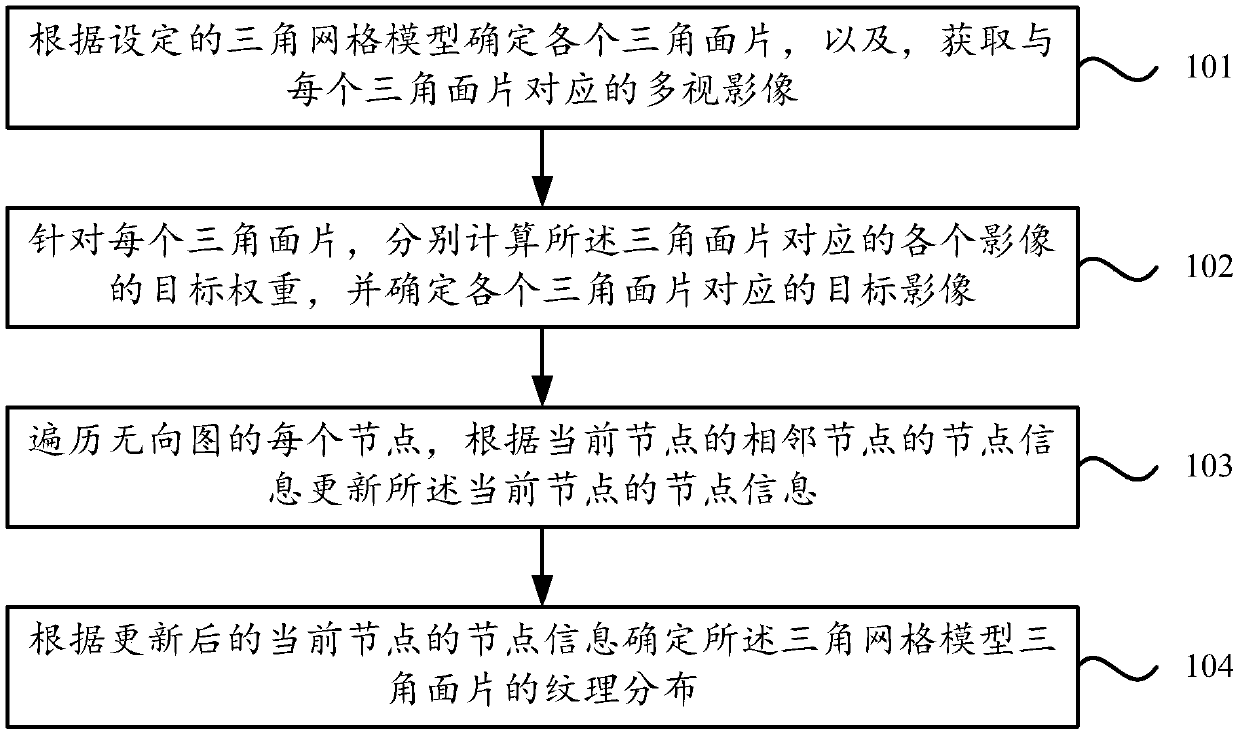

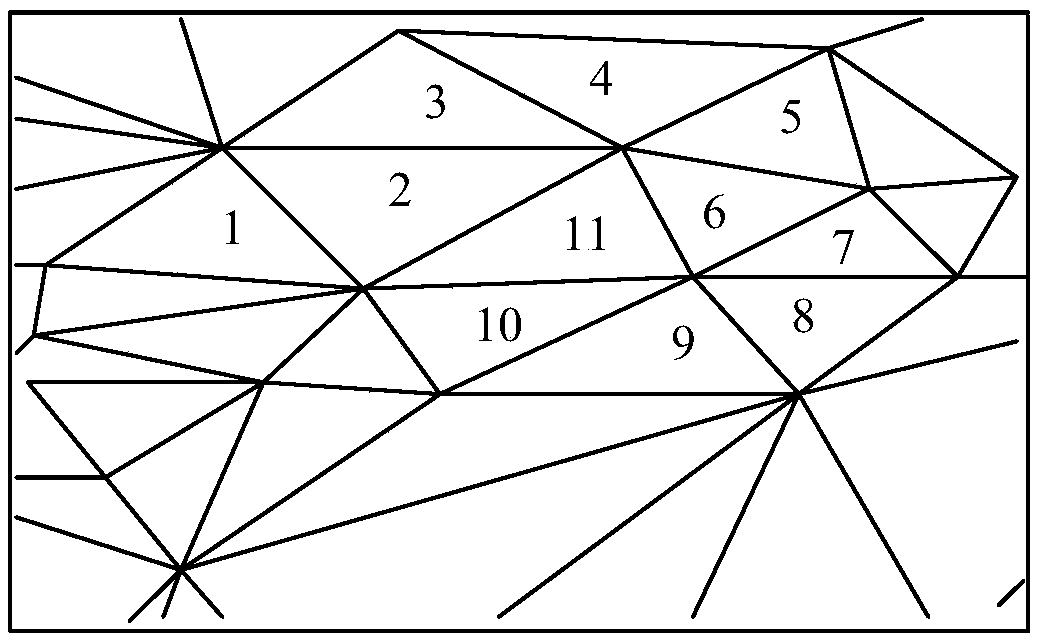

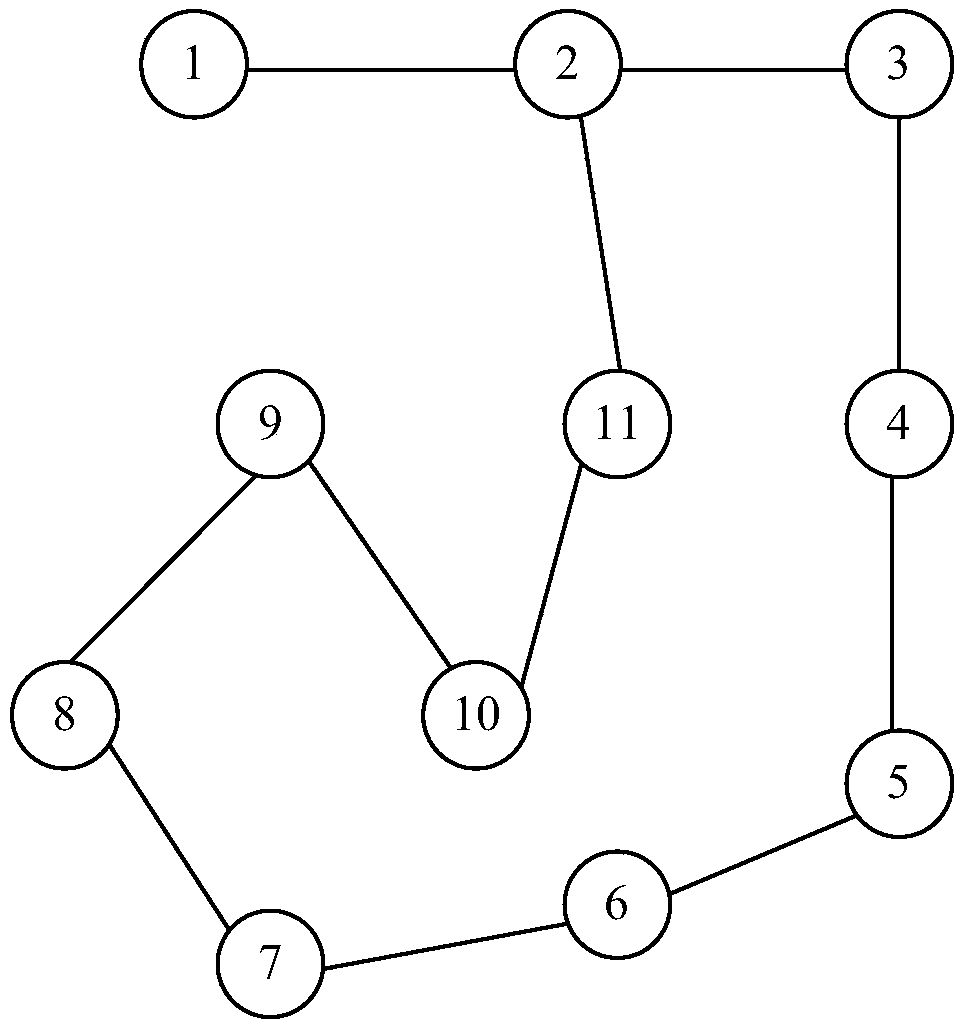

Multi-view image texture distribution determination method and device, equipment and storage medium

PendingCN109685879AImprove texture qualityQuality improvement3D-image rendering3D modellingUndirected graphAlgorithm

The embodiment of the invention discloses a multi-view image texture distribution determination method and device, equipment and a storage medium, and the method comprises the steps: determining eachtriangular patch according to a set triangular grid model, and obtaining a multi-view image corresponding to each triangular patch; Respectively calculating the target weight of each image corresponding to the triangular patch, and determining the target image corresponding to each triangular patch; Traversing each node of the undirected graph, and updating the node information of the current nodeaccording to the node information of the adjacent node of the current node; Wherein the node information of the adjacent node and the node information of the current node respectively comprise a nodevalue and a label, the node value comprises a target image corresponding to a triangular patch of the node, and the label comprises a target image meeting a set condition in the target image; And determining the texture distribution of the triangular patch of the triangular mesh model according to the updated node information of the current node. The texture quality during reconstruction of a natural scene in the multi-view image is improved, and the texture mapping effect is enhanced.

Owner:广东启慧城市信息有限公司

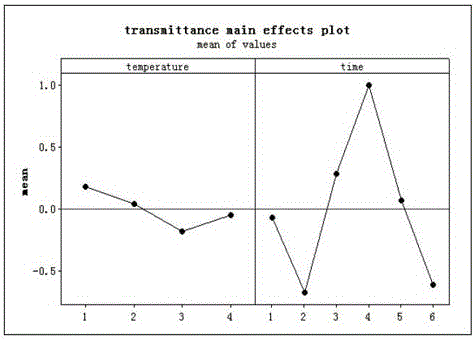

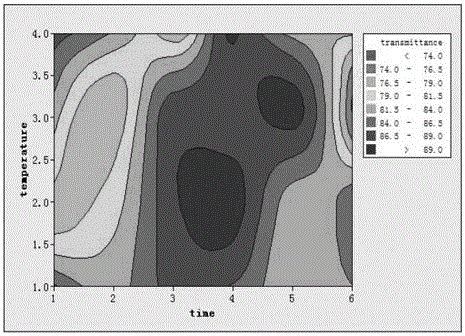

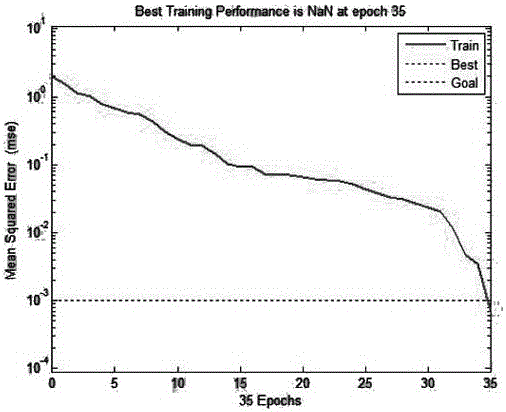

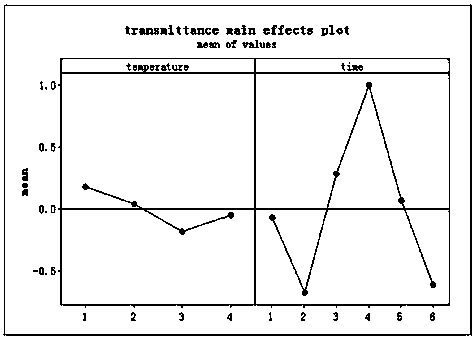

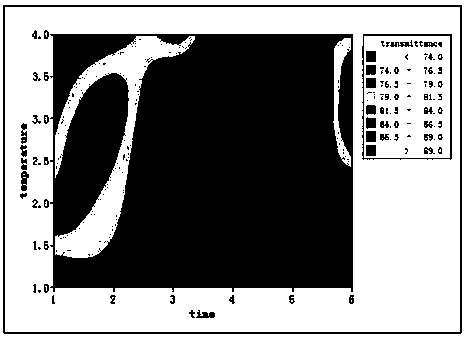

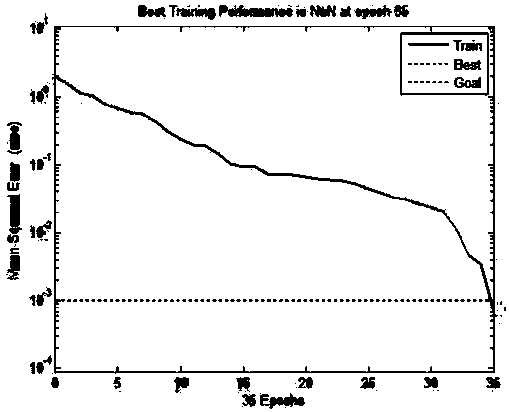

BP neural network-based anti-dazzle glass chemical erosion technological parameter optimization method

ActiveCN106447029AImprove mapping abilityOptimizing Process ParametersNeural learning methodsRelational modelTransmittance

The present invention relates to a BP neural network-based anti-dazzle glass chemical erosion technological parameter optimization method. The method comprises the following steps of S1 processing data; S2 determining an optimization range of the erosion temperature and the erosion time; S3 utilizing a BP neural network to construct a relation model of the erosion temperature, the erosion time and the glass transmittance; S4 carrying out the BP neural network optimization search. According to the present invention, the BP neural network is utilized to optimize an anti-dazzle glass chemical erosion technological parameter, and the BP neural network has the high mapping capability, so that any nonlinear mapping from input to output can be realized. By utilizing the high mapping capability and generalization capability of the BP neural network to establish a nonlinear relation of the temperature, the time and the transmittance, a parameter optimization problem influenced by complicated factors can be solved.

Owner:ZHENGZHOU UNIVERSITY OF AERONAUTICS

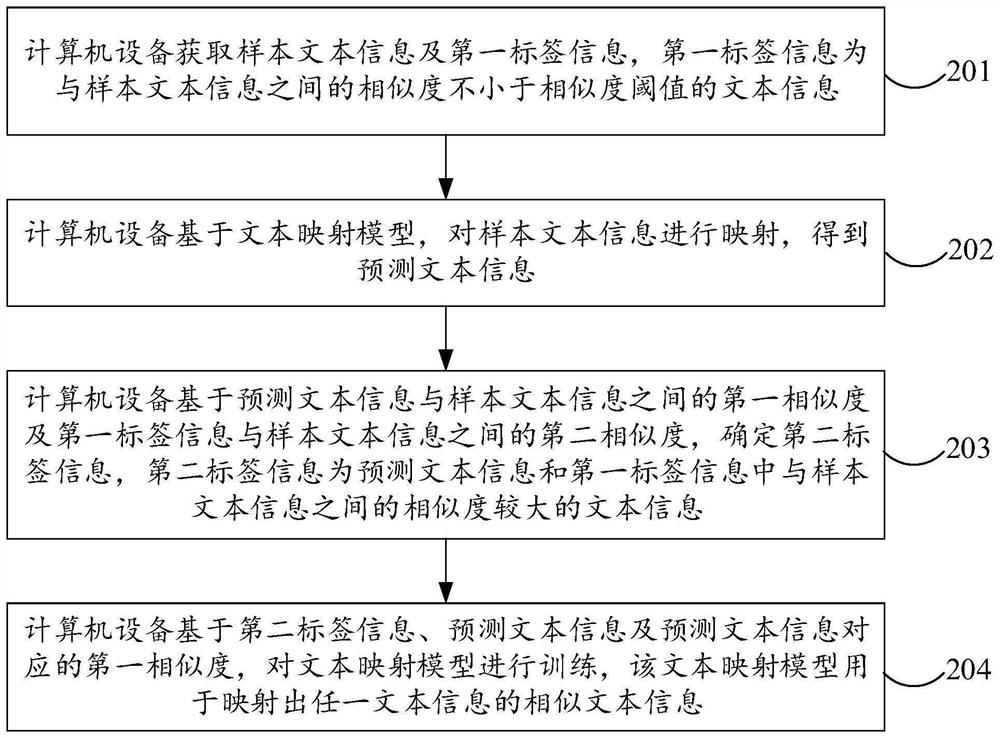

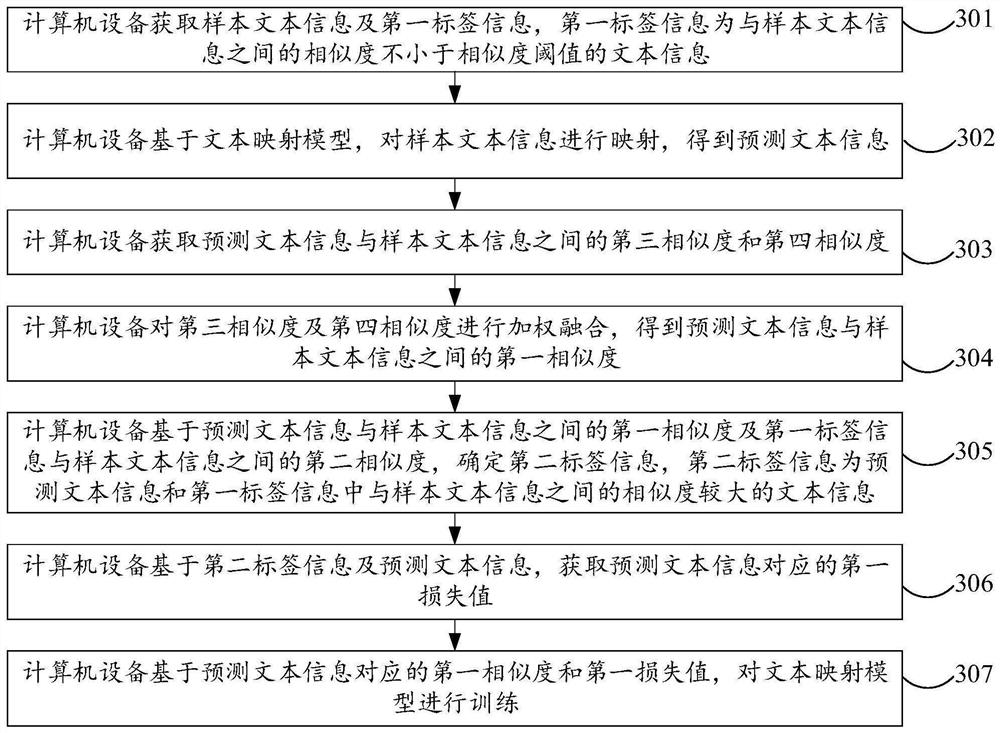

Text mapping model processing method and device, computer equipment and storage medium

PendingCN114328815AImprove mapping abilitySemantic analysisCharacter and pattern recognitionData miningProcessing

The embodiment of the invention discloses a text mapping model processing method and device, computer equipment and a storage medium, and belongs to the technical field of computers. The method comprises the steps of obtaining sample text information and first label information, and mapping the sample text information based on a text mapping model to obtain predicted text information; and determining second label information based on a first similarity between the predicted text information and the sample text information and a second similarity between the first label information and the sample text information, and training the text mapping model based on the second label information, the predicted text information and the first similarity corresponding to the predicted text information. In the embodiment of the application, the text information most similar to the sample text information is taken as the second label information, and the text mapping model is trained based on the predicted text information, the second label text information and the first similarity between the predicted text information and the sample text information, so that the mapping effect of the text mapping model is improved.

Owner:TENCENT TECH (SHENZHEN) CO LTD

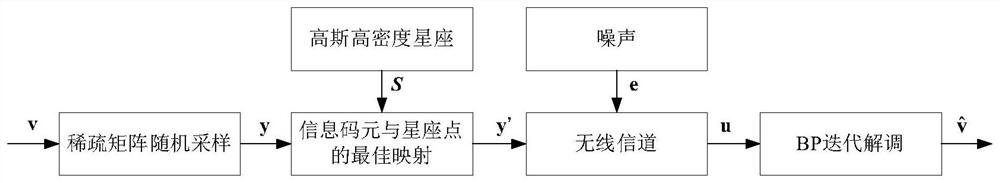

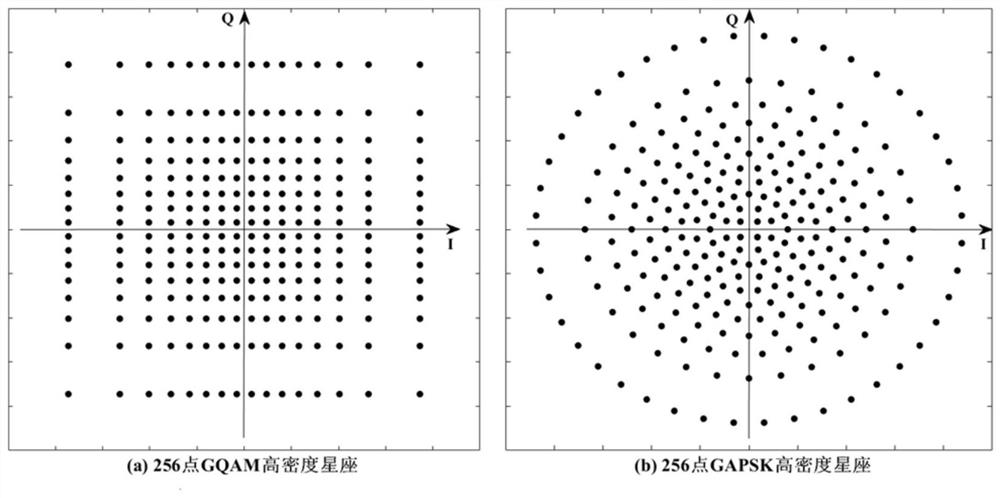

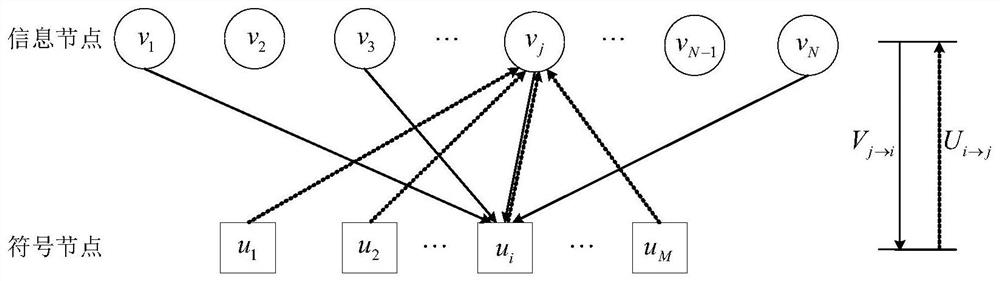

Rate-free modulation and demodulation method approaching capacity limit in wide-range SNR

ActiveCN112953678AImprove mapping abilityIdeal shaping gainCarrier regulationTransmission rate adaptationCoded elementRate modulation

The invention discloses a rateless modulation and demodulation method approaching a capacity limit in a wide-range SNR, and belongs to the technical field of modulation and demodulation in wireless communication. The method comprises the following steps: firstly, a group of constellation points close to Gaussian distribution is fit by using non-uniform interval points with equal probability; secondly, the mapping performance of a constellation diagram is optimized through a BSA algorithm, and a local optimal mapping scheme between information code elements and constellation points is designed; at a sending end, a sparse mapping matrix is used for carrying out random sampling on an information sequence to obtain information code elements, the information code elements are directly modulated to constellation points according to a mapping scheme, and the sampling and mapping times are increased along with the reduction of the channel SNR, so that the adaptive SNR range is expanded; and a receiving end carries out demodulation by adopting a BP iterative algorithm. The method provided by the invention does not need to design a weight set to realize the Gaussian forming of the symbol, can obtain the performance close to the capacity limit in a large-range SNR (Signal to Noise Ratio), and is a modulation and demodulation method with a rate-free characteristic.

Owner:HUAZHONG UNIV OF SCI & TECH

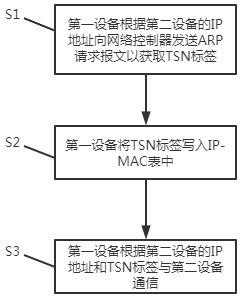

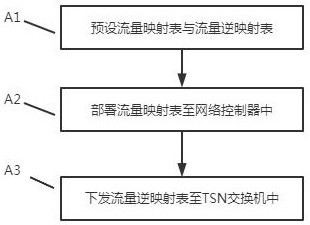

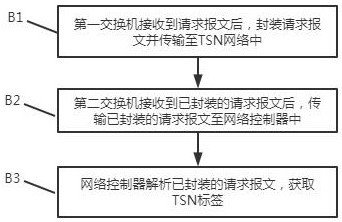

A Traffic Mapping Method for Time Sensitive Networks

ActiveCN113259244BReduced traffic mapping performanceImproved traffic mapping performanceData switching networksIp addressInternet traffic

The invention discloses a traffic mapping method for a time-sensitive network, comprising the following steps: a first device sends a request message to a network controller according to an IP address of a second device to obtain a TSN label; the first device writes the TSN label into the IP-MAC table; the first device communicates with the second device according to the IP address and TSN label of the second device. In this technical solution, when the first device accesses the peer communication device in the TSN network, it only needs to call the TSN label obtained from the network controller and stored in the IP-MAC table combined with the IP address of the peer device. Communication between the first device and the peer device. There is no need to add a TSN label to each communication data packet, which avoids the degradation of traffic mapping performance caused by this processing method. Therefore, the technical solution is simple and convenient, and can significantly improve network traffic mapping performance.

Owner:NAT UNIV OF DEFENSE TECH

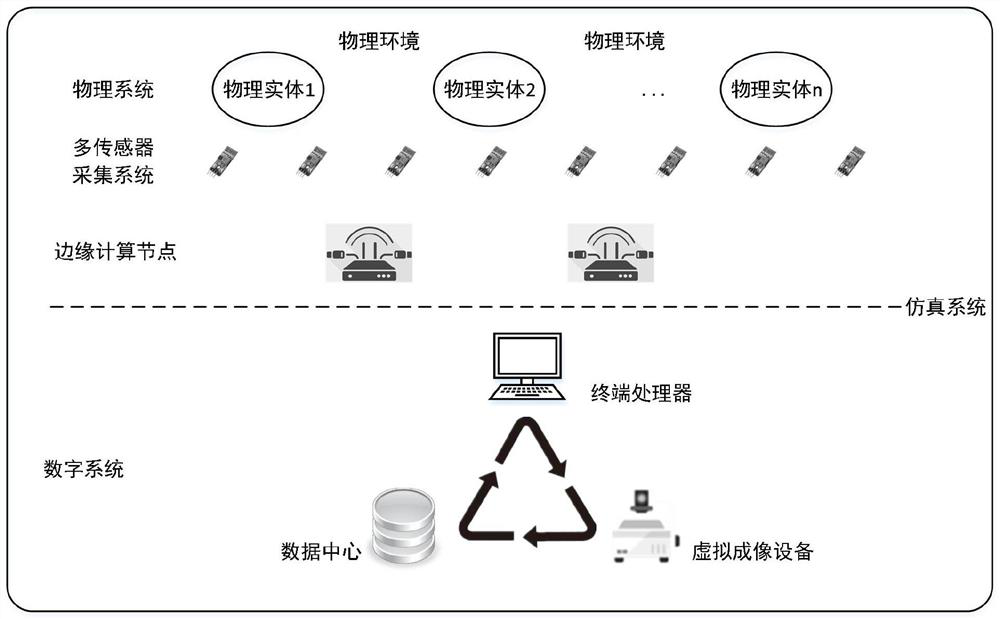

A digital twin system based on virtual imaging technology

ActiveCN109819233BRealize nearby computing processingImplement extractionTransmissionImage data processingEdge computingMultiple sensor

The invention relates to a strong mapping digital twin system based on a virtual imaging technology. According to the system, a multi-information cooperative communication mechanism is established between digital twin bodies, morphological information, state information and behavior information of a physical entity system are collected through multiple sensors and sent to an edge computing node, and the edge computing node is responsible for receiving sensor information and carrying out edge computing processing on the received information; A virtual imaging technology is applied to project digital entities of the digital twin system into a real space in a three-dimensional visualization mode, meanwhile, state information of the physical entities is displayed in a virtual reality mode, thedetail display effect of the digital twin system is enhanced, and the requirements for multi-view observation and immersion experience are met; According to the system, strong information mapping isestablished between a physical entity and a digital entity through the process, and it is guaranteed that information is transmitted between twin bodies in real time at a high speed in an undistortedmode.

Owner:合肥哈工热气球数字科技有限公司

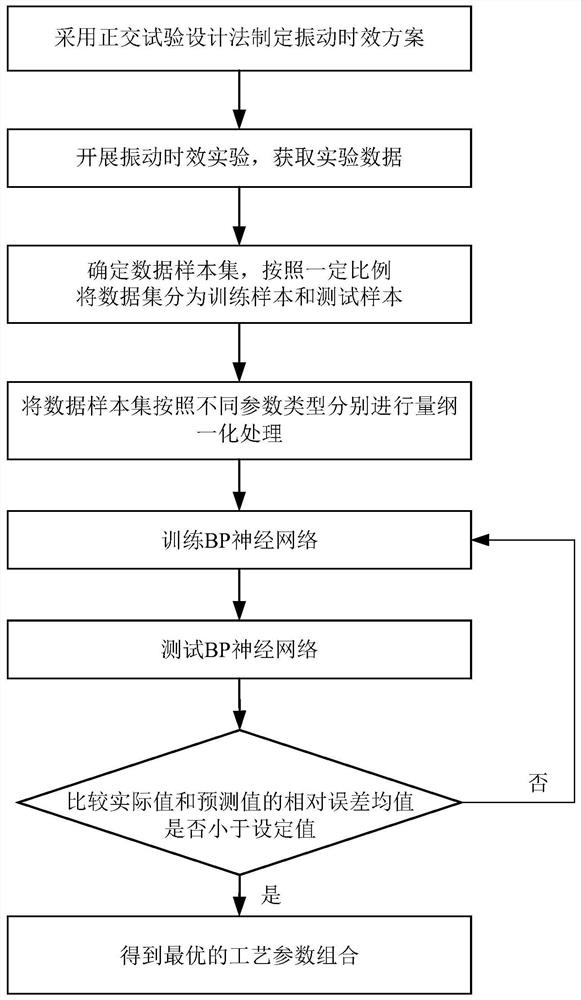

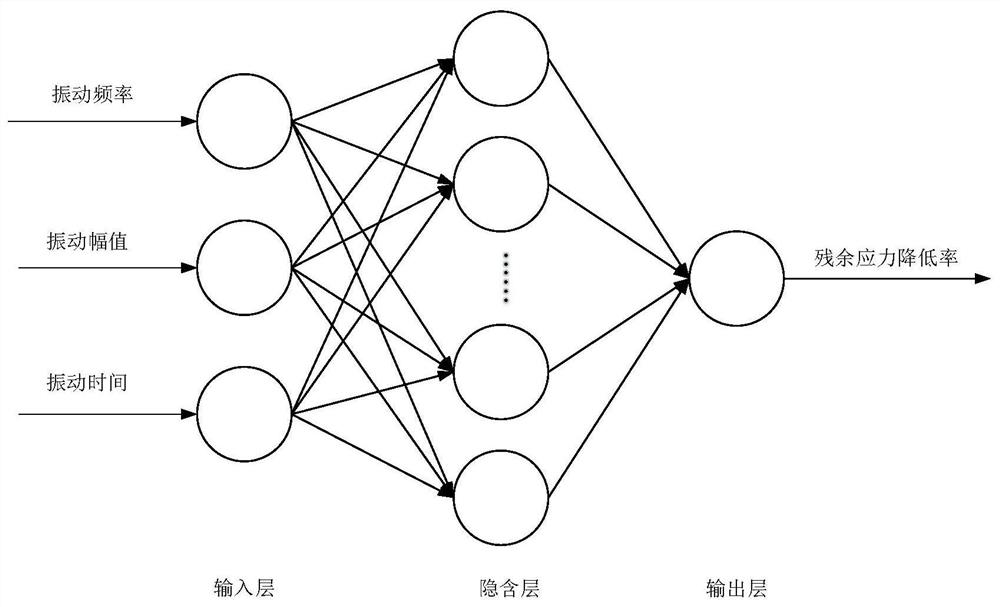

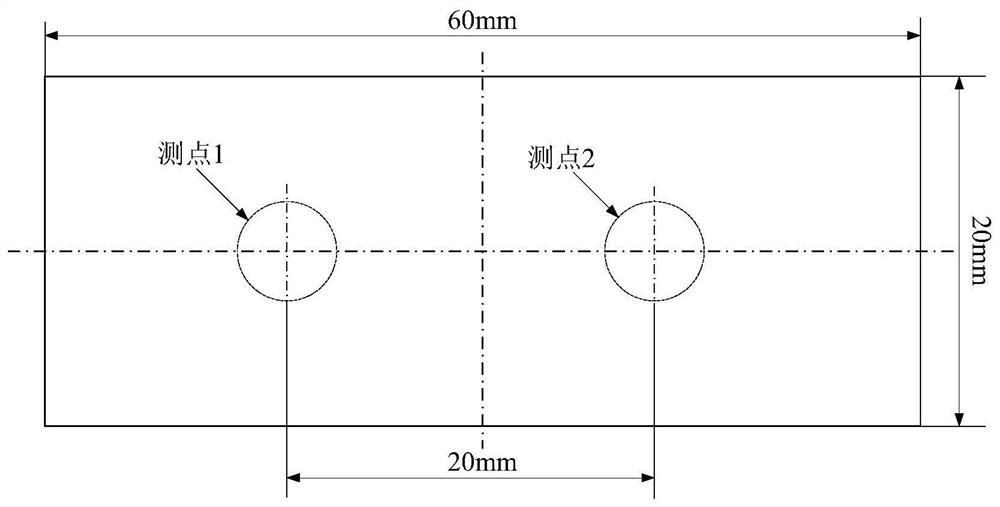

Vibration aging process parameter optimization method based on BP neural network

The invention discloses a vibration aging process parameter optimization method based on a BP neural network. The method is characterized by comprising the following steps that an orthogonal experiment design method is adopted to formulate a vibration aging experiment scheme, a vibration aging experiment is carried out, and experiment data are obtained; dimension normalization processing is carried out on obtained data sample sets respectively according to different parameter categories, and the data sets are divided into two parts, namely a training sample and a test sample according to a certain proportion; the BP neural network is trained and tested by using the data subjecte to dimension normalization; and according to errors of residual stress values obtained through tests and experiments, weights and threshold values of all layers of the network are corrected till a relative error mean value of a predicted value and an actual value is smaller than a set value, an optimal technological parameter combination is obtained, and finally the vibration aging technological parameter optimization method based on the BP neural network is formed. The method has the advantages that a vibration aging process parameter adjusting process is simplified, and the optimal process parameters are obtained.

Owner:SHANGHAI MARITIME UNIVERSITY

Optimizing method of anti-glare glass chemical erosion process parameters based on bp neural network

ActiveCN106447029BImprove mapping abilityOptimizing Process ParametersNeural learning methodsRelational modelTransmittance

The present invention relates to a BP neural network-based anti-dazzle glass chemical erosion technological parameter optimization method. The method comprises the following steps of S1 processing data; S2 determining an optimization range of the erosion temperature and the erosion time; S3 utilizing a BP neural network to construct a relation model of the erosion temperature, the erosion time and the glass transmittance; S4 carrying out the BP neural network optimization search. According to the present invention, the BP neural network is utilized to optimize an anti-dazzle glass chemical erosion technological parameter, and the BP neural network has the high mapping capability, so that any nonlinear mapping from input to output can be realized. By utilizing the high mapping capability and generalization capability of the BP neural network to establish a nonlinear relation of the temperature, the time and the transmittance, a parameter optimization problem influenced by complicated factors can be solved.

Owner:ZHENGZHOU UNIVERSITY OF AERONAUTICS

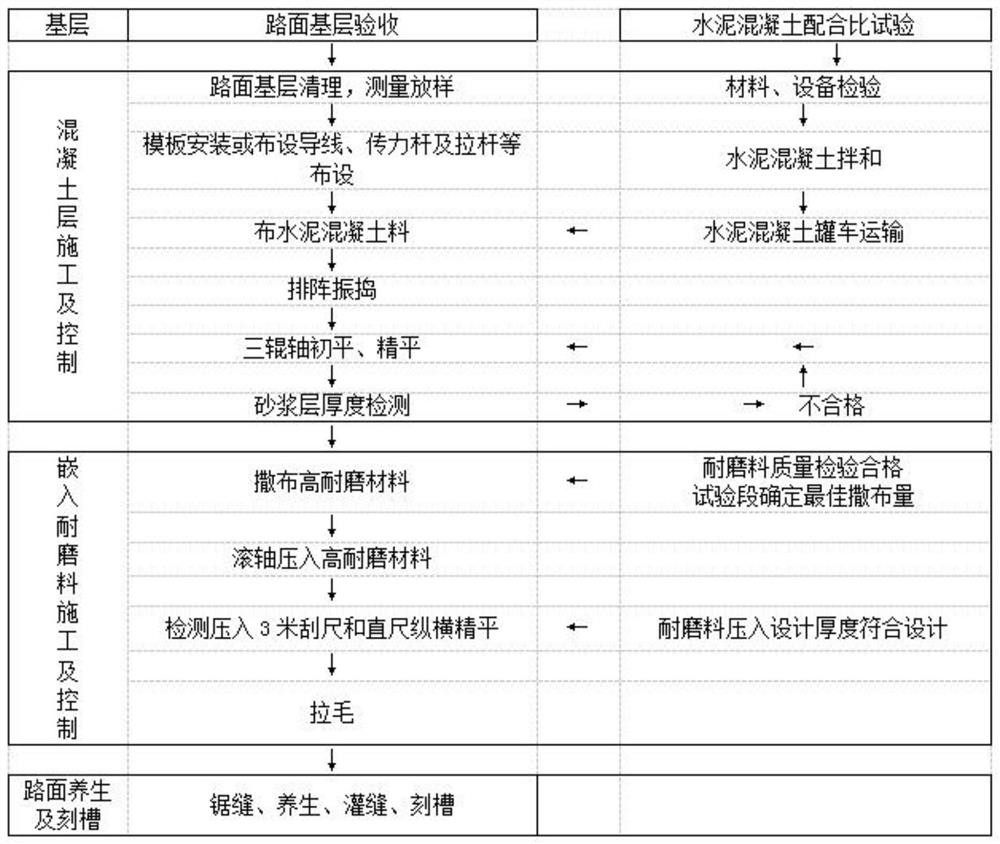

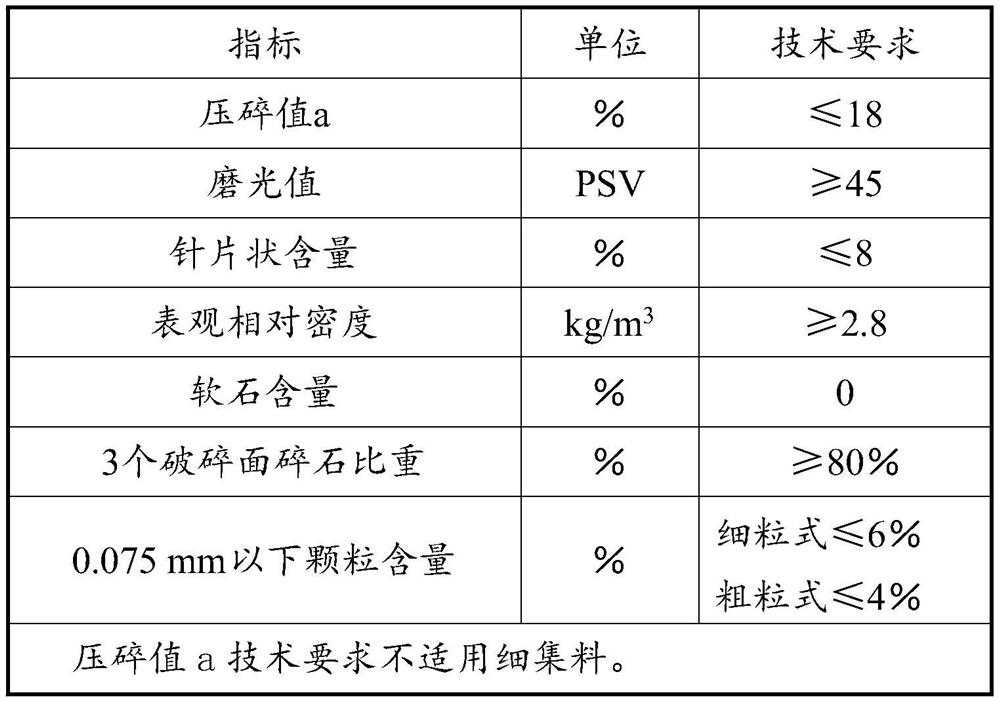

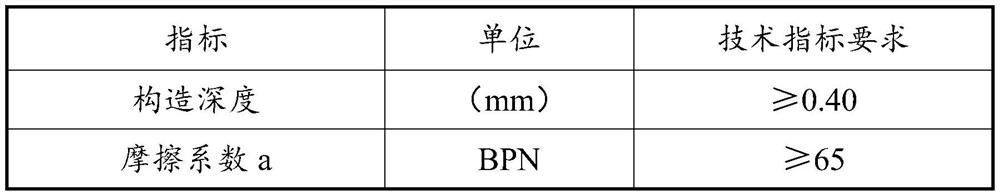

Wear-resistant embedded type anti-skid layer of new cement concrete pavement and construction method

PendingCN111979869AImproves skid resistance and resistance to skid fadingImprove mapping capabilitiesIn situ pavingsPaving gutters/kerbsScreedNatural sand

The invention discloses a wear-resistant embedded type anti-skid layer of a new cement concrete pavement and a construction method, and relates to the technical field of highway engineering. The wear-resistant anti-skid layer comprises a wear-resistant material embedded in the surface of the new cement concrete pavement; when being used for tunnel pavements, the wear-resistant material includes high wear-resistant aggregates, pigments and a retroreflection material, and when being applied to other parts, the wear-resistant material only includes the high wear-resistant aggregates; and the highwear-resistant aggregates are natural or artificial stones each with a polishing value of not less than 45PSV. The construction method comprises the following innovated contents: base treatment and necessary preparation work; concrete layer concrete proportion design, workability requirement, a construction method for and process control over a surface mortar layer; a construction and control method for the wear-resistant material embedded anti-skid functional layer, a uniform spreading method for the wear-resistant material, an embedding and endurance method for the wear-resistant material,a skid resistance and flatness improvement method for he wear-resistant layer, and the like; anti-slip layer curing at a plastic stage, structure treatment and the like. The anti-skid layer can save scarce natural sand resources, makes full use of recycled aggregates, and realizes changing wastes into treasures.

Owner:RES INST OF HIGHWAY MINIST OF TRANSPORT

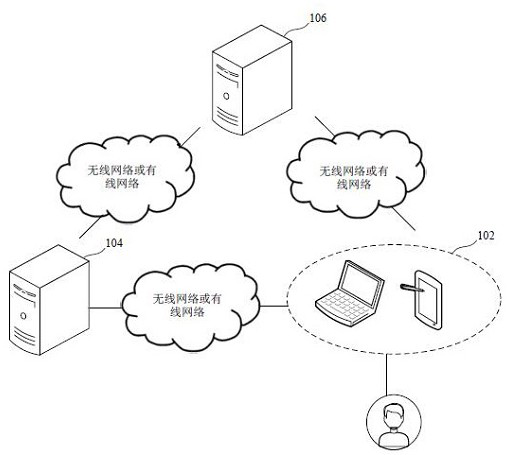

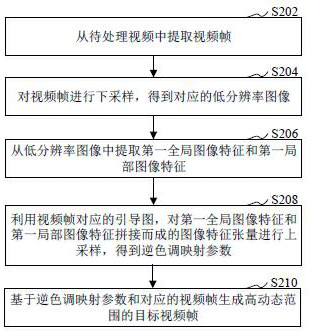

Video processing method, device, computer equipment and storage medium

ActiveCN111683269BAvoid brightnessAvoid chromatic aberrationCharacter and pattern recognitionNeural architecturesPattern recognitionTone mapping

The present application relates to a video processing method, apparatus, computer equipment and storage medium. The method includes: extracting a video frame from a video to be processed; down-sampling the video frame to obtain a corresponding low-resolution image; extracting a first global image feature and a first local image from the low-resolution image feature; use the guide map corresponding to the video frame to upsample the image feature tensor formed by splicing the first global image feature and the first local image feature to obtain inverse tone mapping parameters; based on the inverse Tone-mapping parameters and corresponding video frames generate high dynamic range target video frames. Using this method can avoid the problem of brightness or color difference when the video is converted from low dynamic range to high dynamic range.

Owner:TENCENT TECH (SHENZHEN) CO LTD

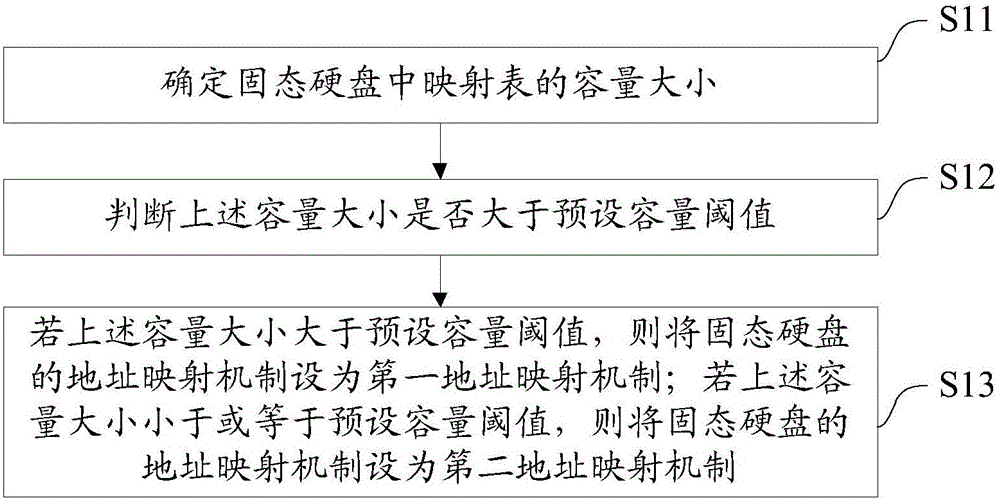

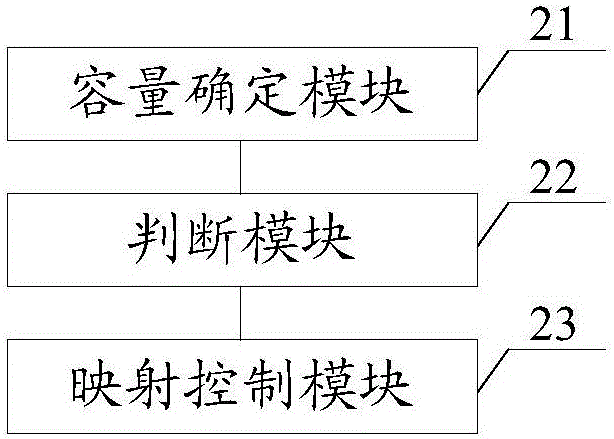

Address mapping method and system as well as solid-state disk

InactiveCN105975403AExcellent mapping performanceImprove mapping abilityMemory adressing/allocation/relocationSolid-stateAddress mapping

The invention discloses an address mapping method and system as well as a solid-state disk. The method comprises the steps of determining the capacity of a mapping table in the solid-state disk; judging whether the capacity is greater than a preset capacity threshold or not; if the capacity is greater than the preset capacity threshold, setting an address mapping mechanism of the solid-state disk as a first address mapping mechanism; and if the capacity is smaller than or equal to the preset capacity threshold, setting the address mapping mechanism of the solid-state disk as a second address mapping mechanism, wherein the mapping table capacity required by the first address mapping mechanism is smaller than that of the second address mapping mechanism, and the mapping performance of the second address mapping mechanism is superior to that of the first address mapping mechanism. According to the method and system as well as the solid-state disk, the advantages of two different address mapping mechanisms can be combined, so that the solid-state disk can have relatively high mapping performance while the mapping table of the solid-state disk occupies relatively small space.

Owner:INSPUR BEIJING ELECTRONICS INFORMATION IND

An aerial photogrammetry system and method integrating non-scanning lidar

ActiveCN105783875BKeep small and lightweightImprove mapping abilityPhotogrammetry/videogrammetryNavigation by speed/acceleration measurementsAviationPhotographic processor

The invention discloses an aerial photogrammetric system integrated with a non-scanning laser radar and an aerial photogrammetric method. The system comprises the non-scanning laser radar, a CCD (Charge Coupled Device) digital camera, a positioning-orienting POS (Passive Optical Splitter) module and a control-storage module. The method comprises the following steps of carrying out multiple-laser-beam irradiation on a visual field range by the non-scanning laser radar based on a focal plane array, so as to determine the distances of many sampling points in a visual field; meanwhile, by utilizing pose data provided by the positioning-orienting POS module, resolving out the geodetic three-dimensional coordinate of each sampling point as ground control information of subsequent aerial photographic processing; collecting an aerial photogrammetric photo of the same visual field by the CCD digital camera, realizing aerial survey mapping according to the information, which is provided by the laser radar, of a ground control point in quick and low-cost manners. According to the aerial photogrammetric system integrated with the non-scanning laser radar and the aerial photogrammetric method, a conventional field ground control method is replaced by adopting the three-dimensional imaging by the non-scanning laser radar; a charting period can be greatly shortened; the cost is decreased; the mapping capacity of a zone which is severe in geographical environment is improved.

Owner:MIANYANG SKYEYE LASER TECH

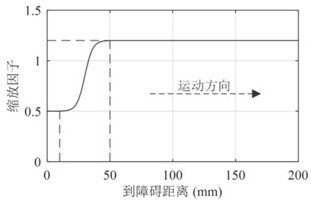

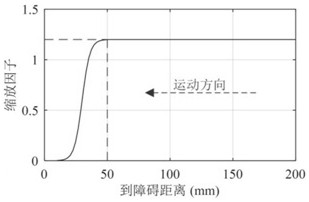

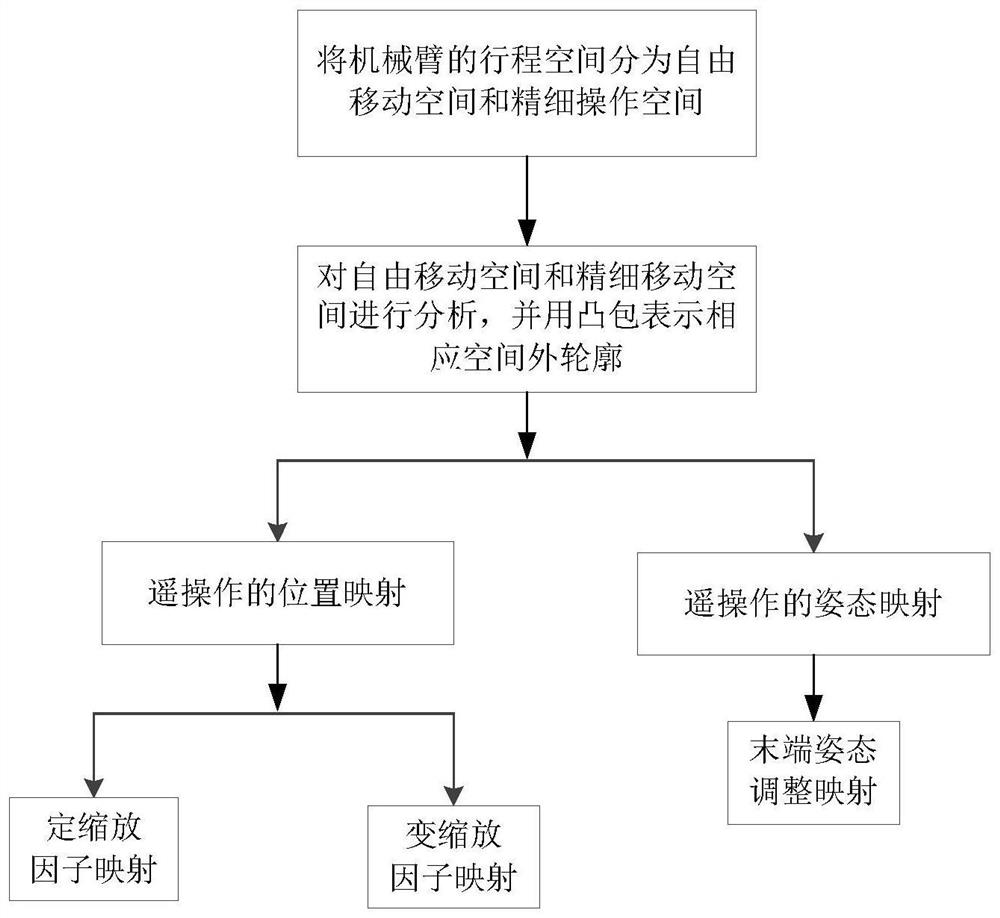

Motion mapping method of teleoperated manipulator based on cyberforce

ActiveCN107877517BImprove mapping abilityProgramme-controlled manipulatorMedicineComputer graphics (images)

The invention discloses a motion mapping method based on a CyberForce teleoperation mechanical arm, belongs to the technical field of robot teleoperation, and aims to solve the problem that the control mapping effect of a conventional control method for robot astronauts is poor as working spaces of the mechanical arm and human arms are inconsistent. The motion mapping method comprises the steps that a motion space of the mechanical arm is divided into a free moving space and a fine operation space; bulges are utilized to represent an outer contour of a reachable working space in a corresponding space; in a bulge outer contour of the free moving space, the position is controlled through set zoom factor mapping and the posture is controlled through posture adjustment mapping according to thereachable working space of the mechanical arm; and in a bulge outer contour of the fine operation space, the position is controlled through variable zoom factor mapping and the posture is controlledthrough posture adjustment mapping according to a set posture space of the mechanical arm. The motion mapping method is used for control of the position and posture of the tail end of the mechanical arm.

Owner:HARBIN INST OF TECH