Patents

Literature

60results about "CAD with nanotechnology" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

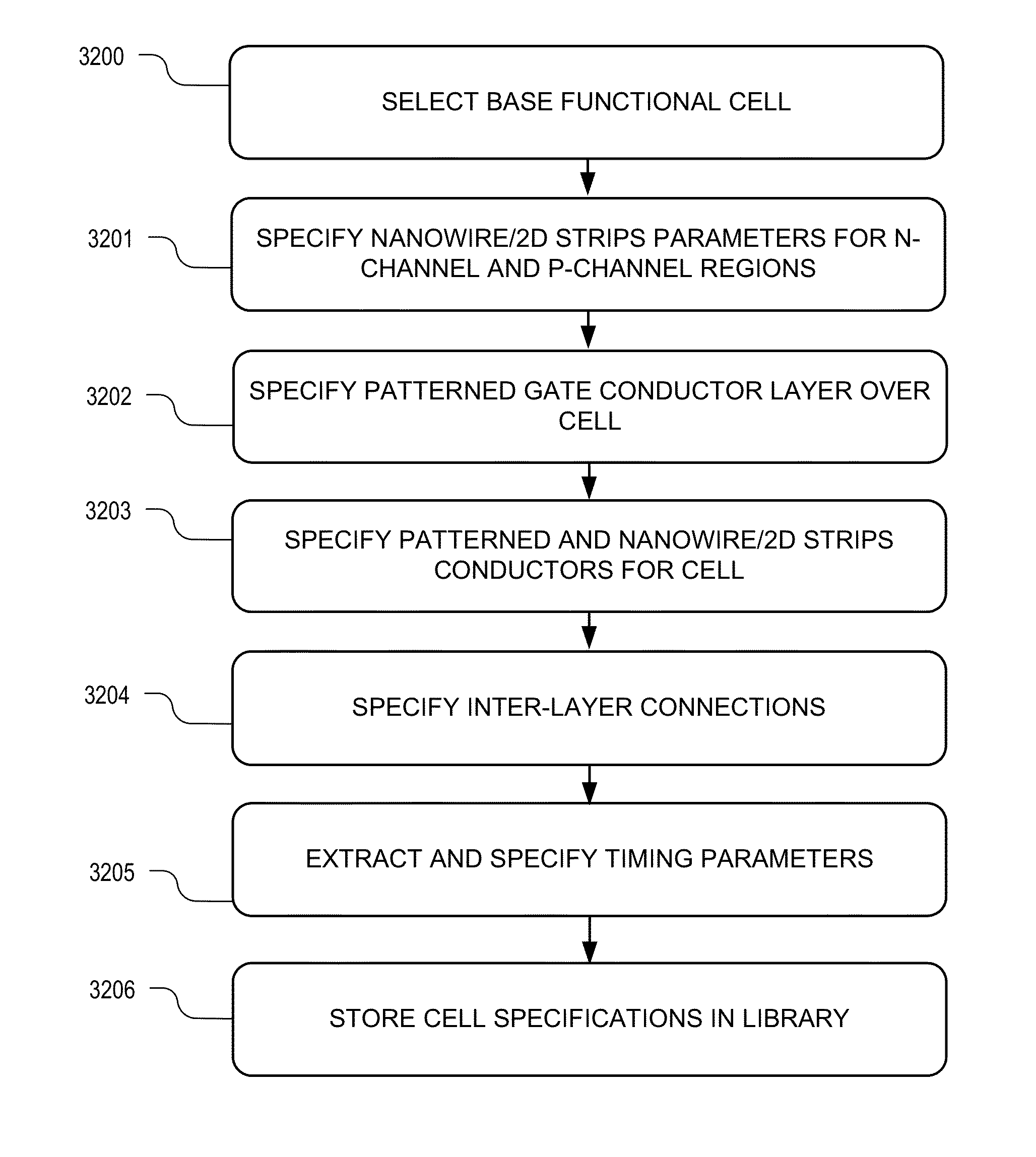

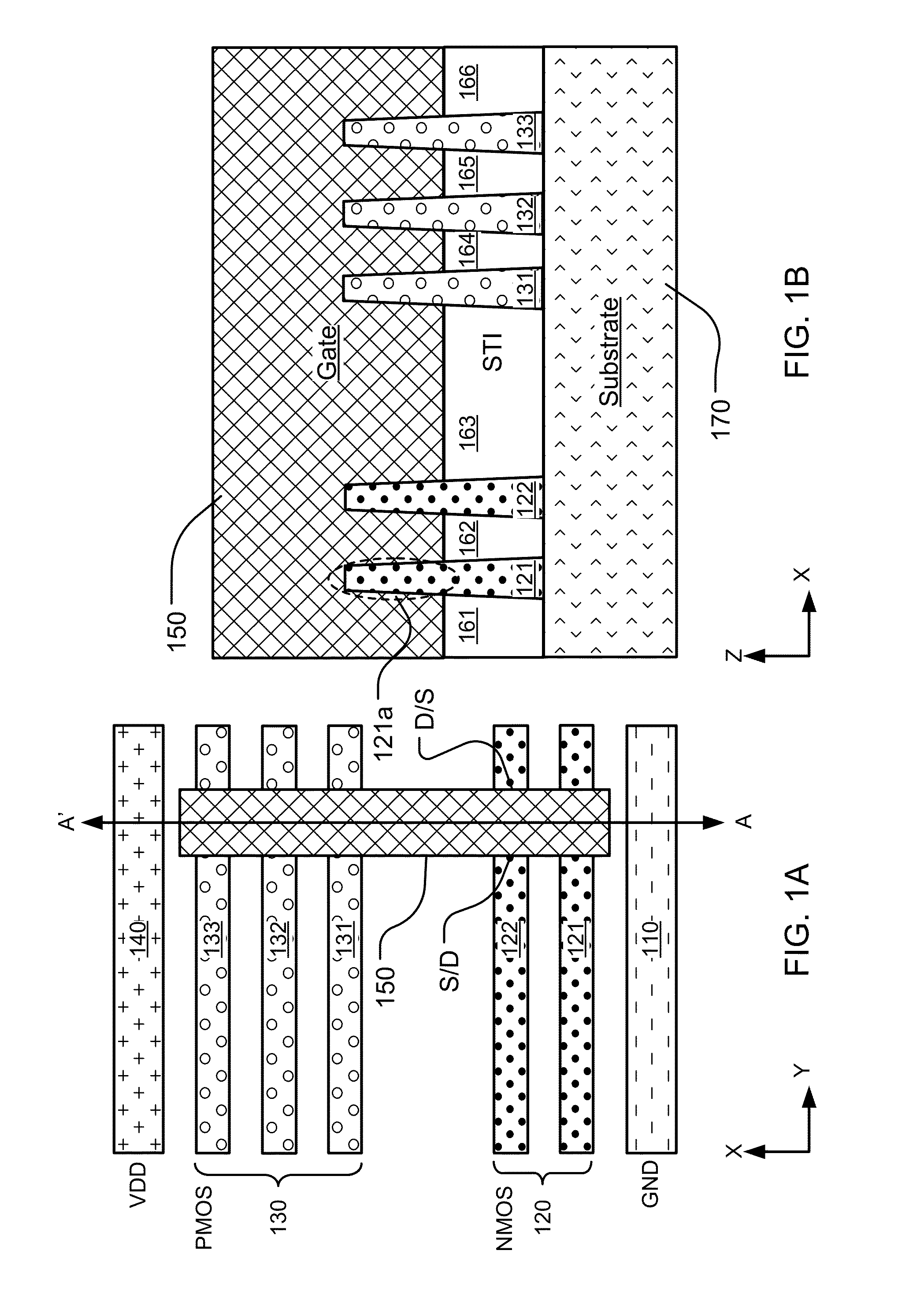

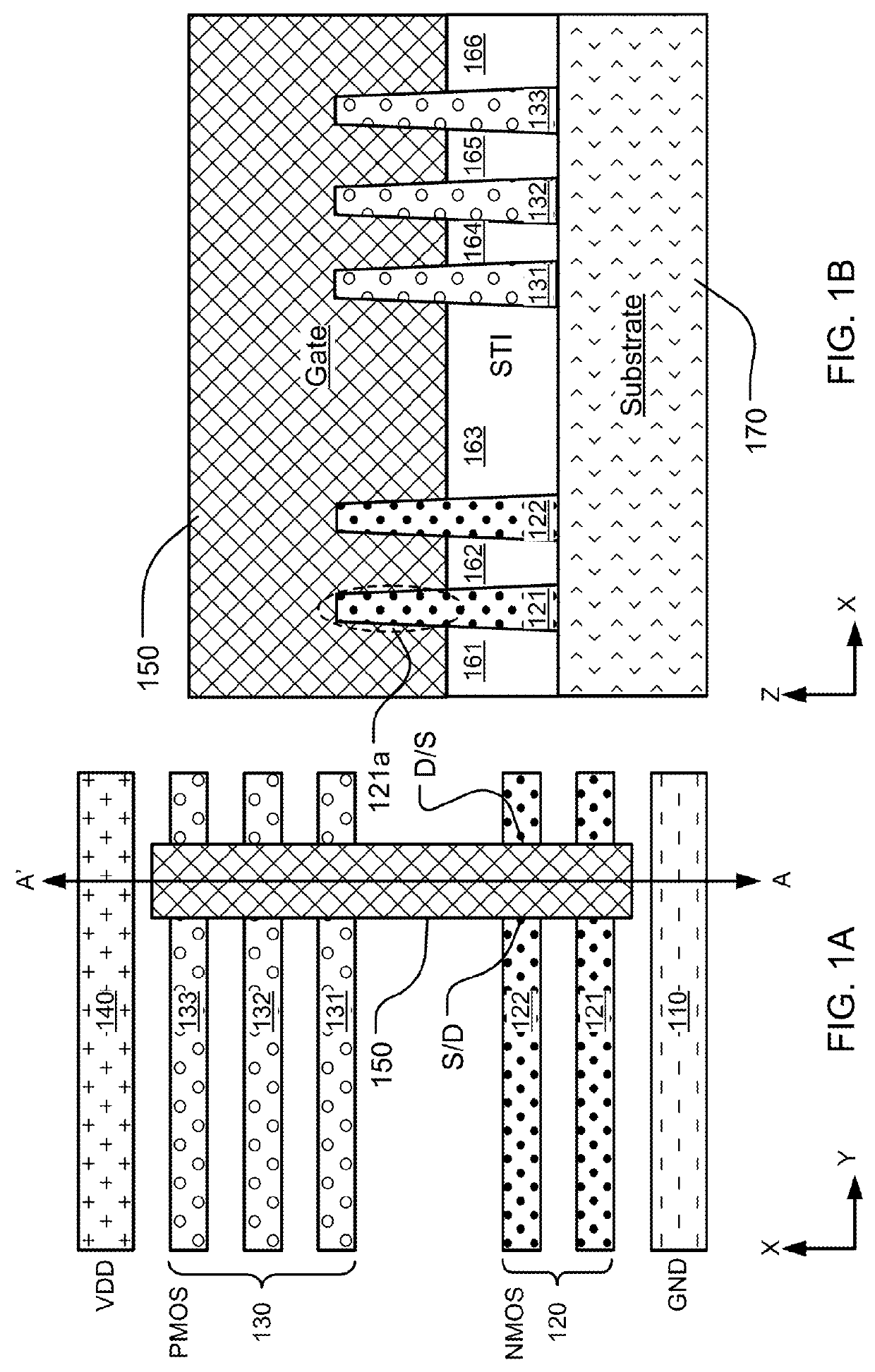

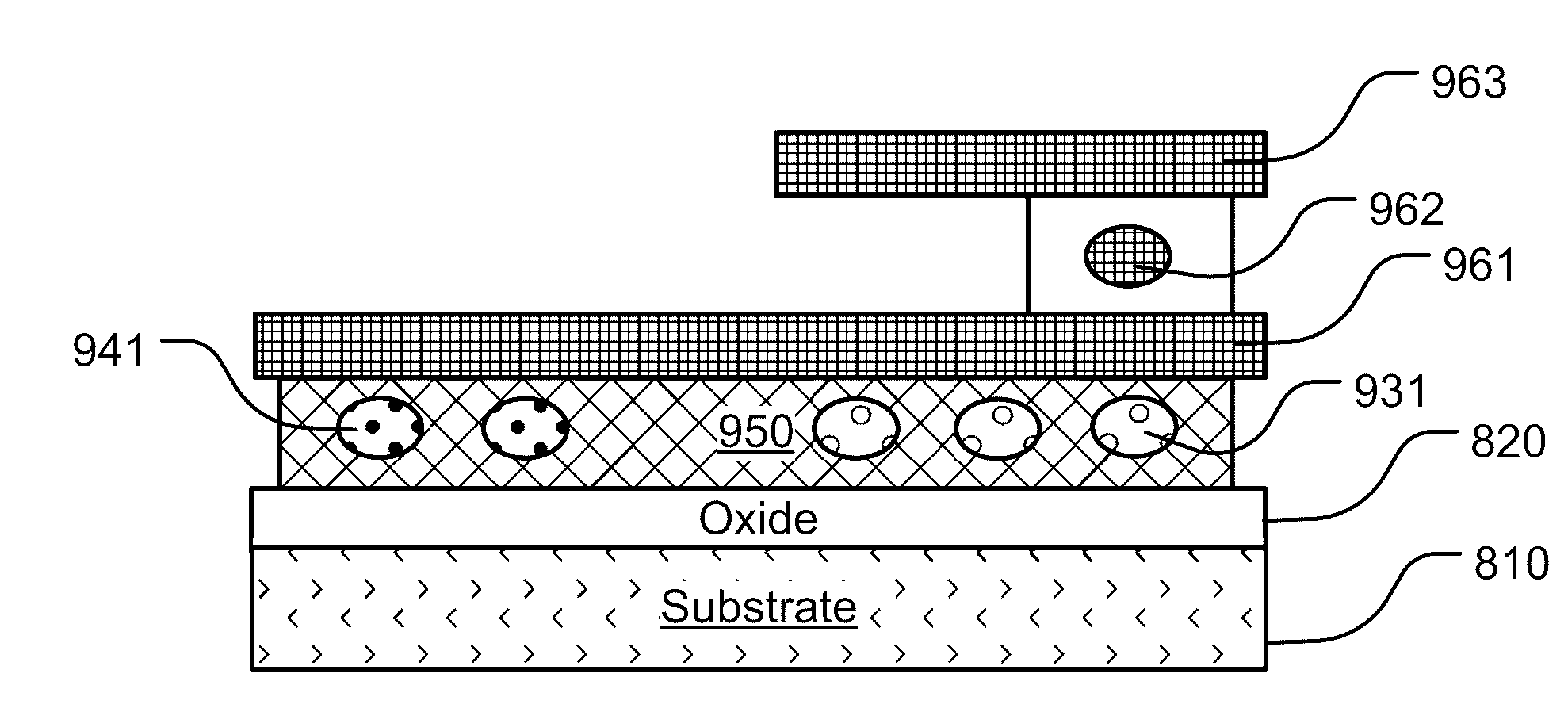

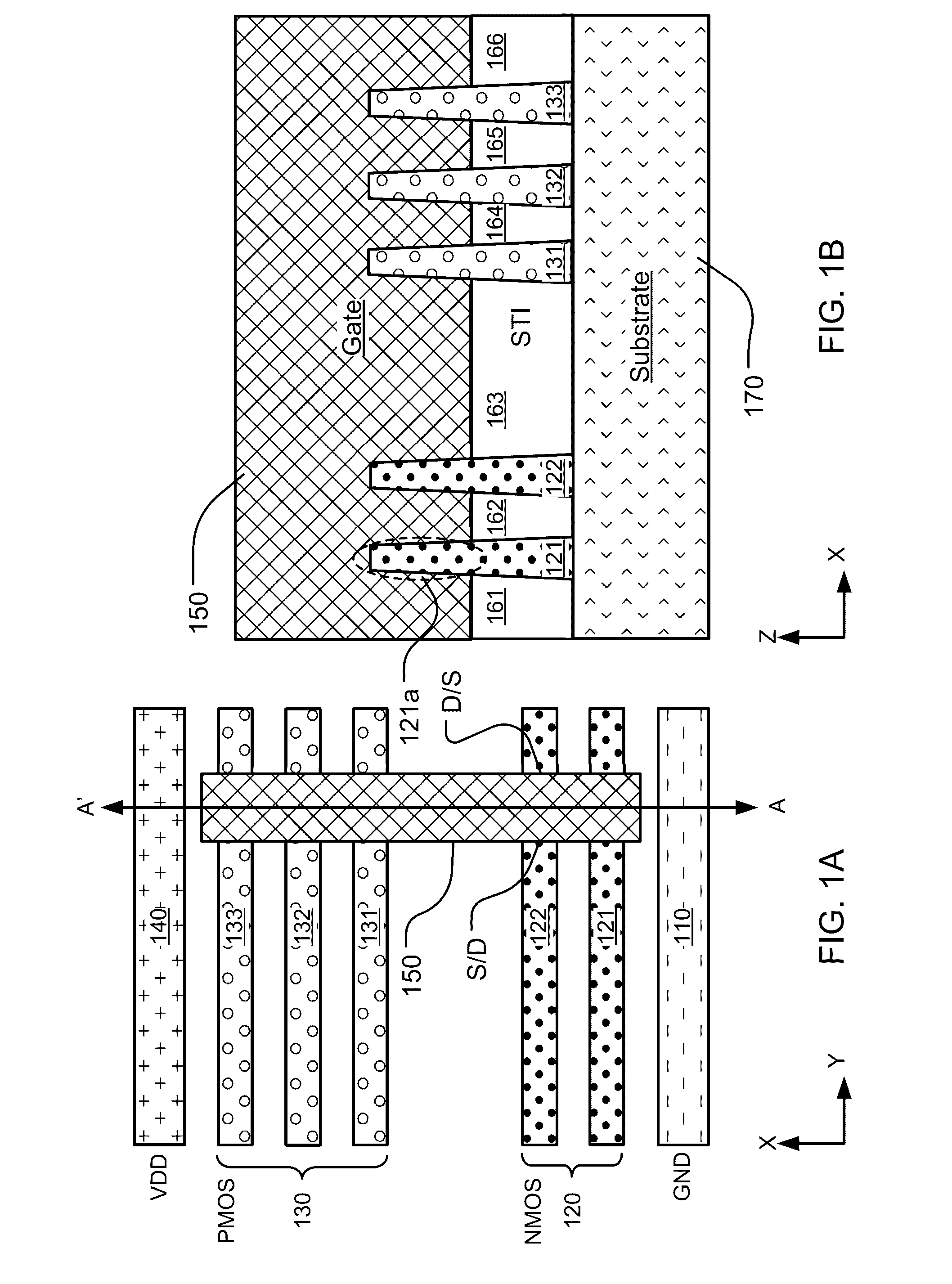

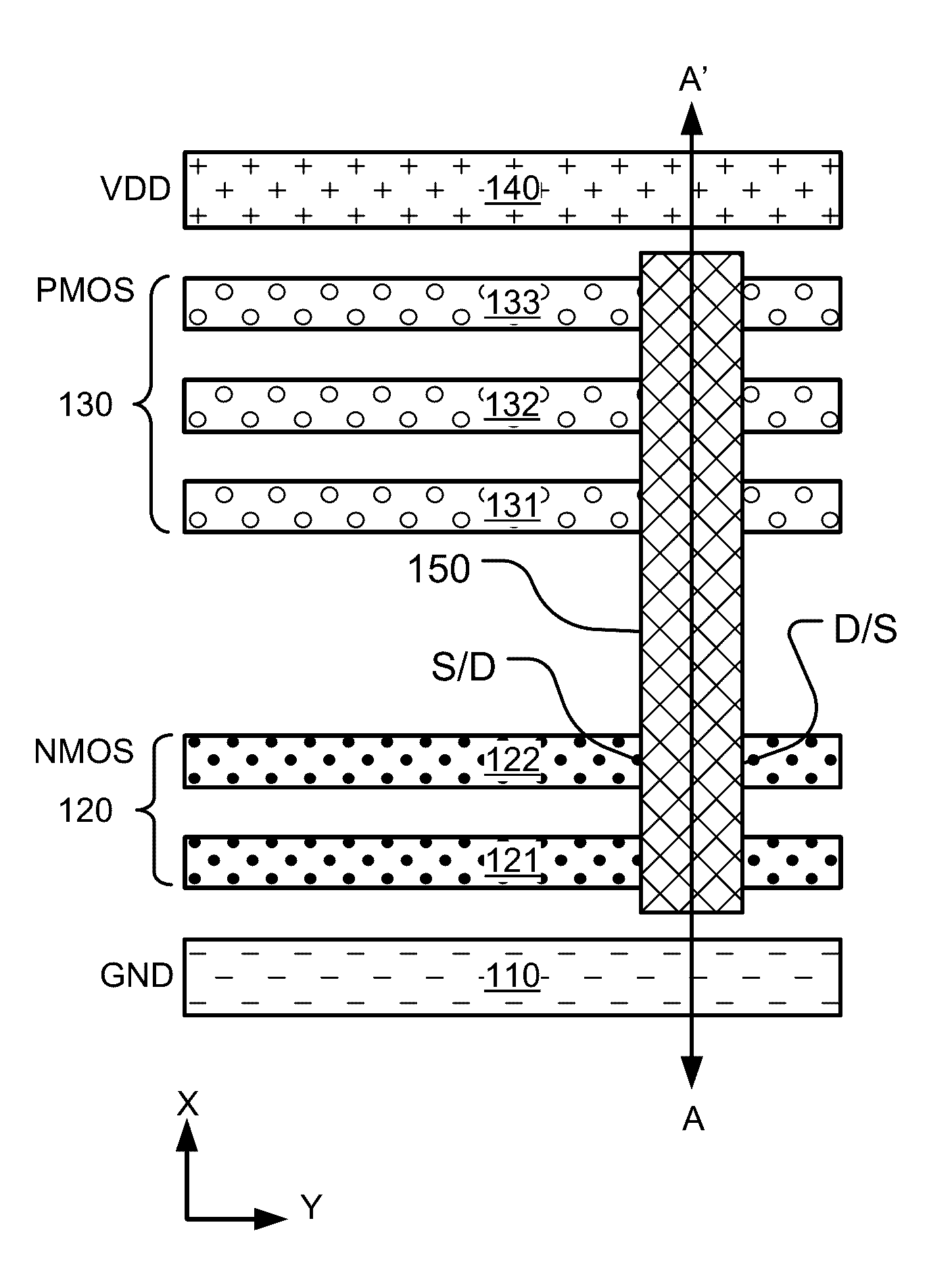

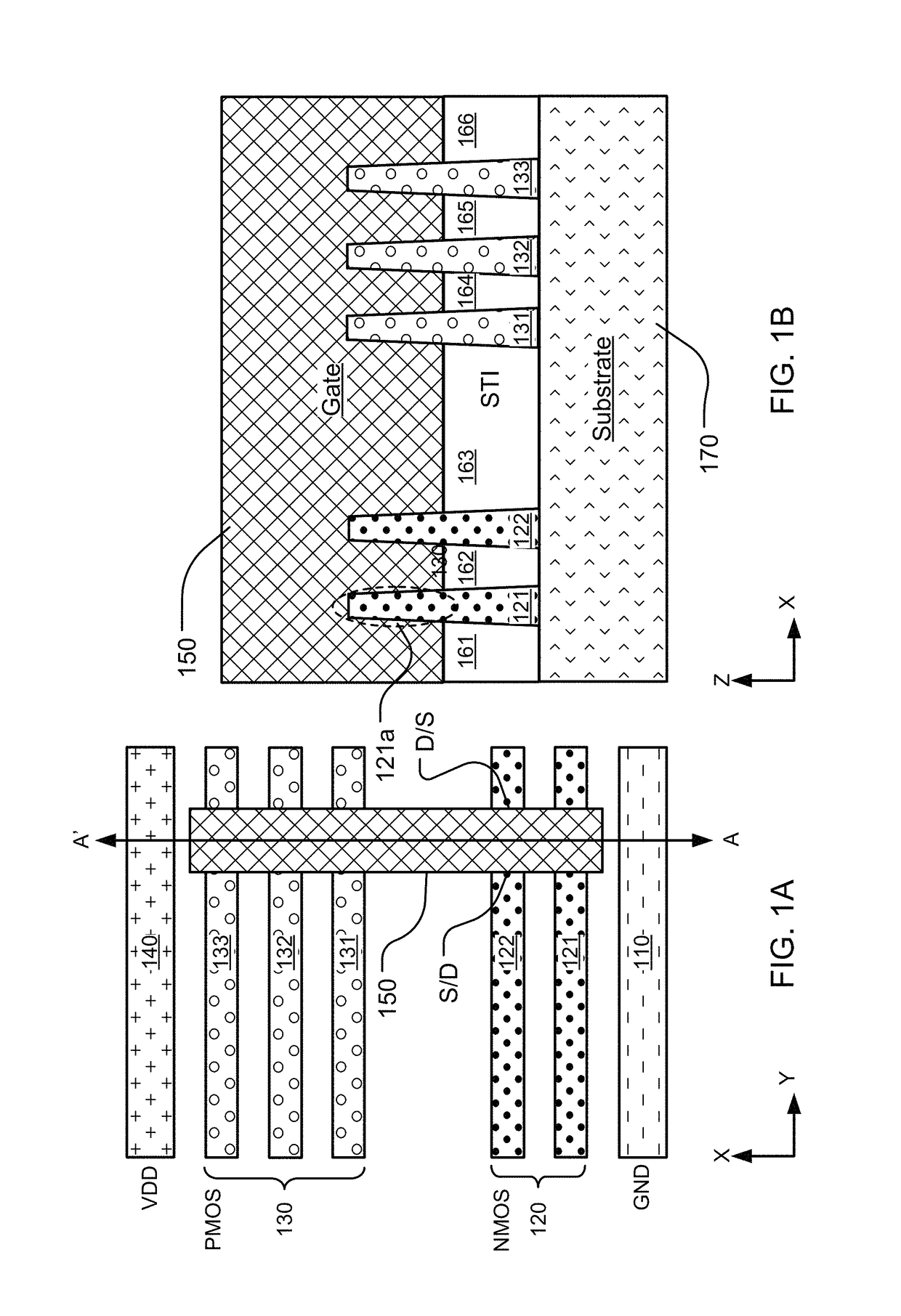

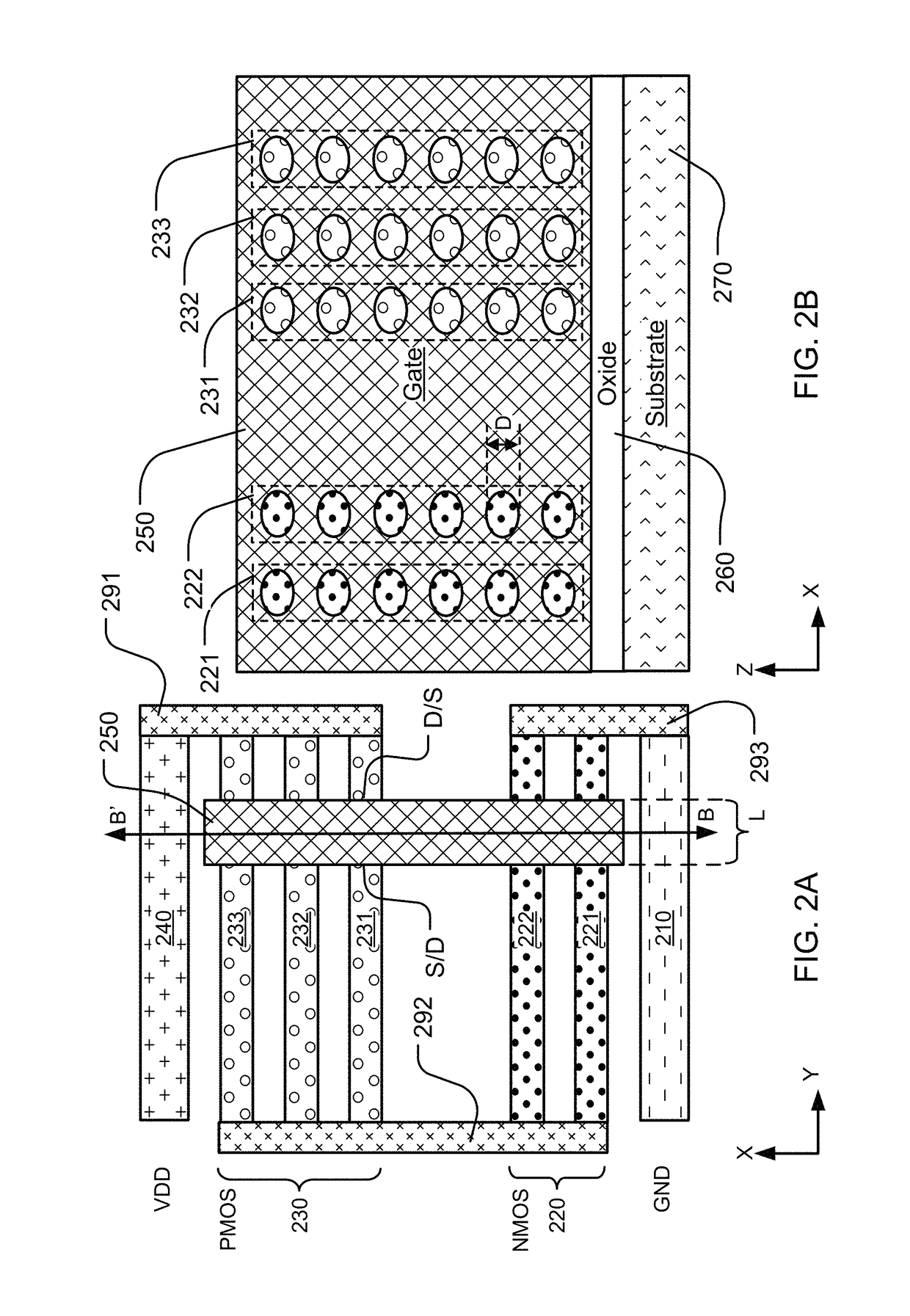

Design tools for integrated circuit components including nanowires and 2d material strips

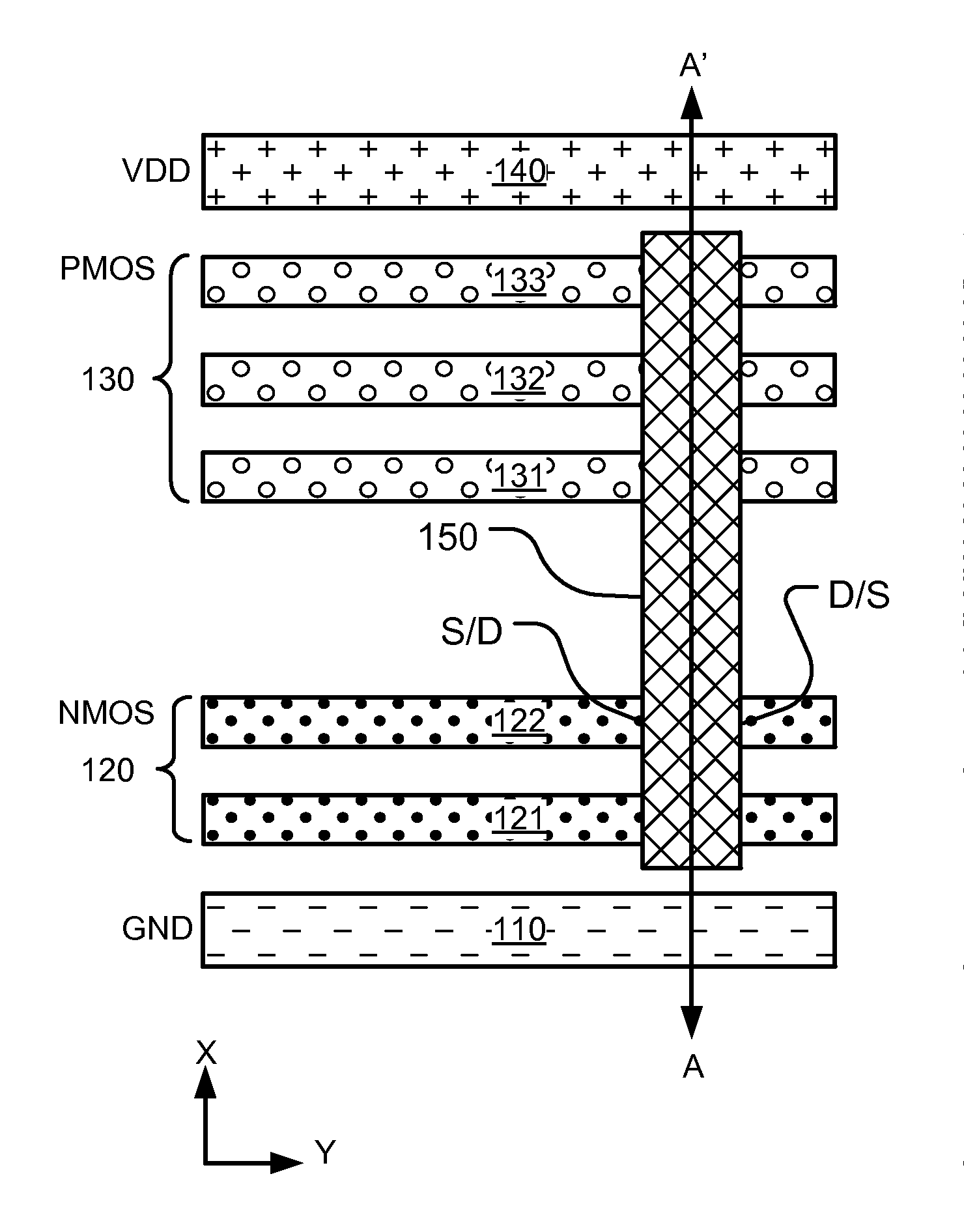

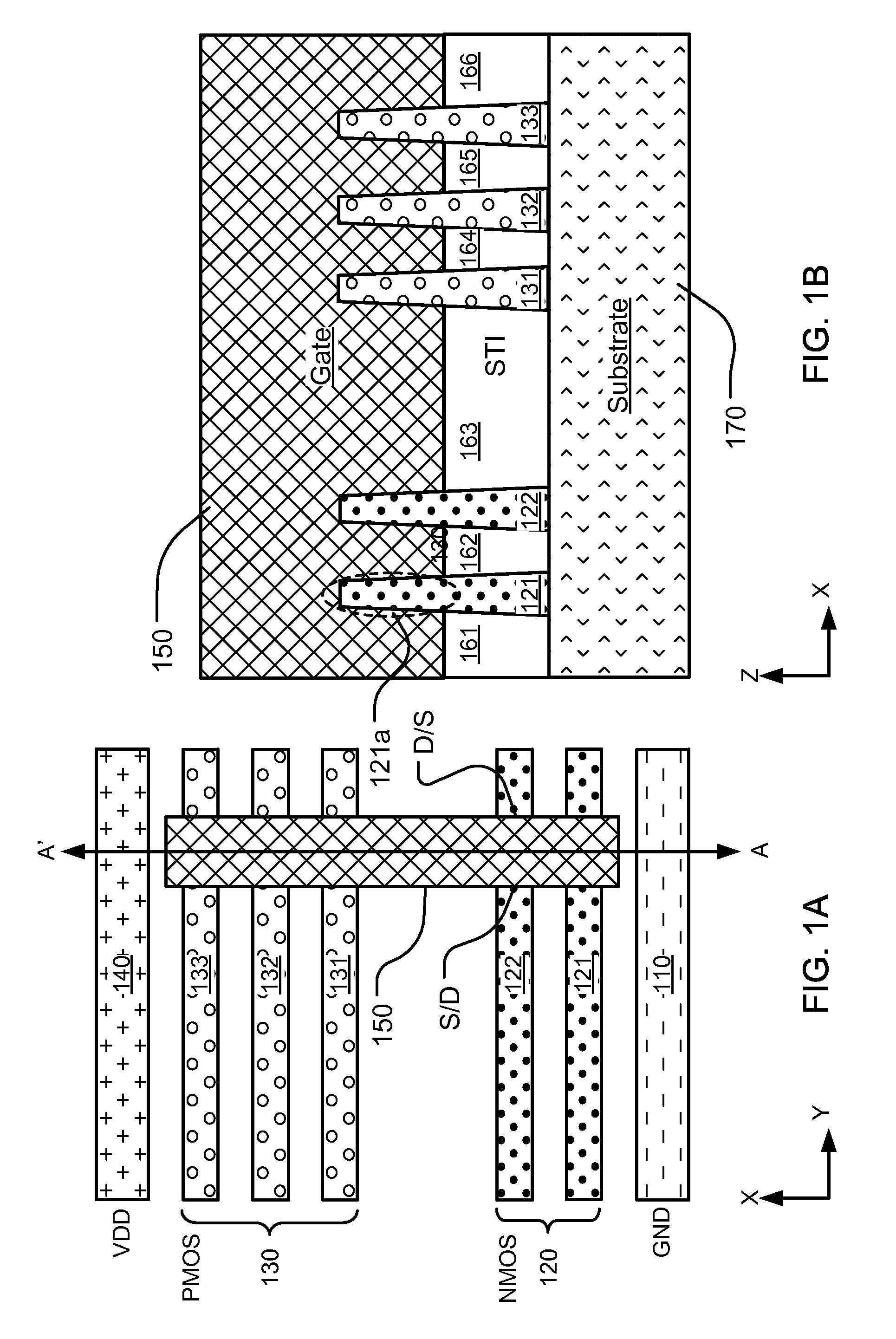

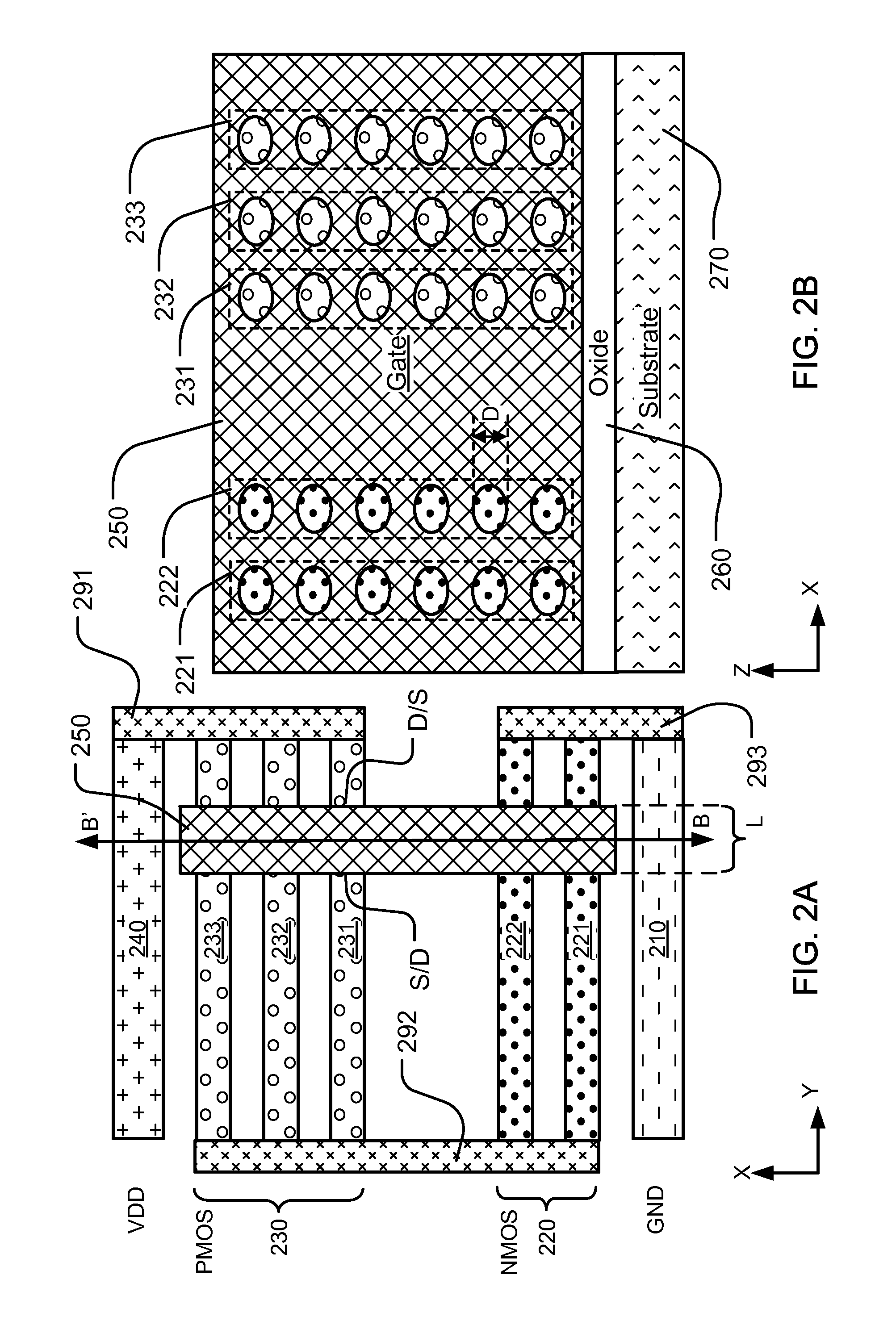

ActiveUS20150370947A1Improve the level ofDifferent performanceTransistorNanoinformaticsNanowireElectrical conductor

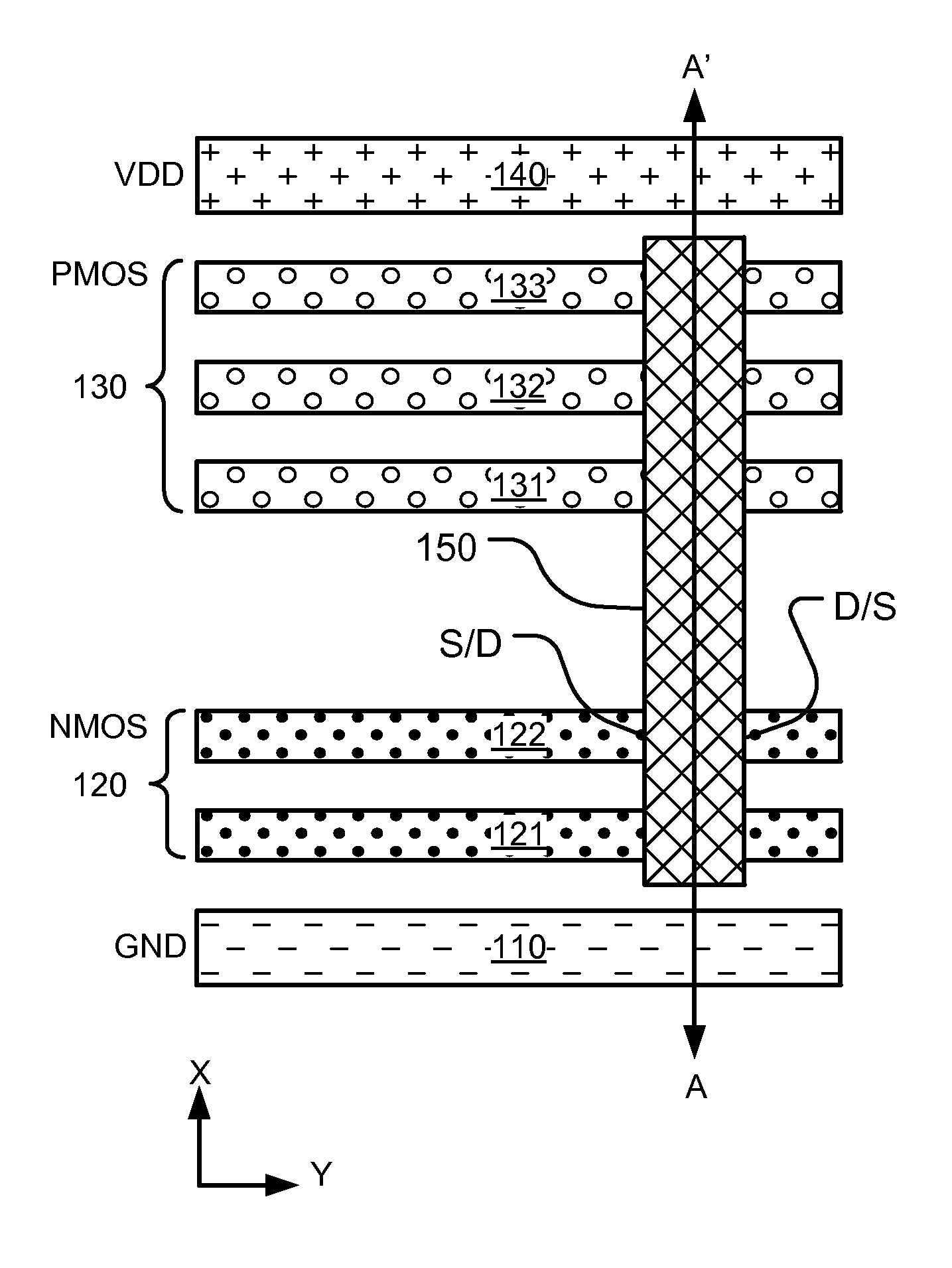

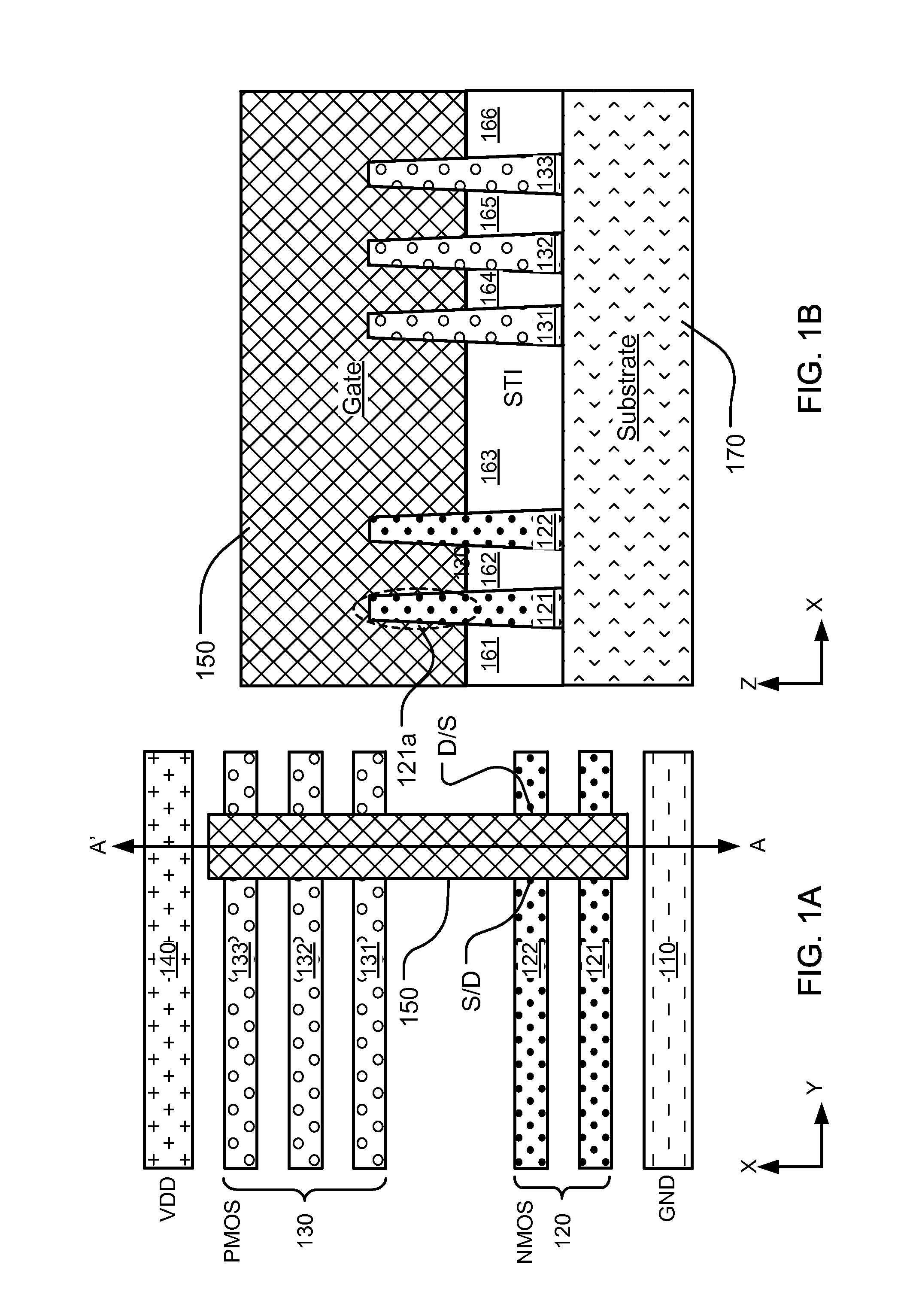

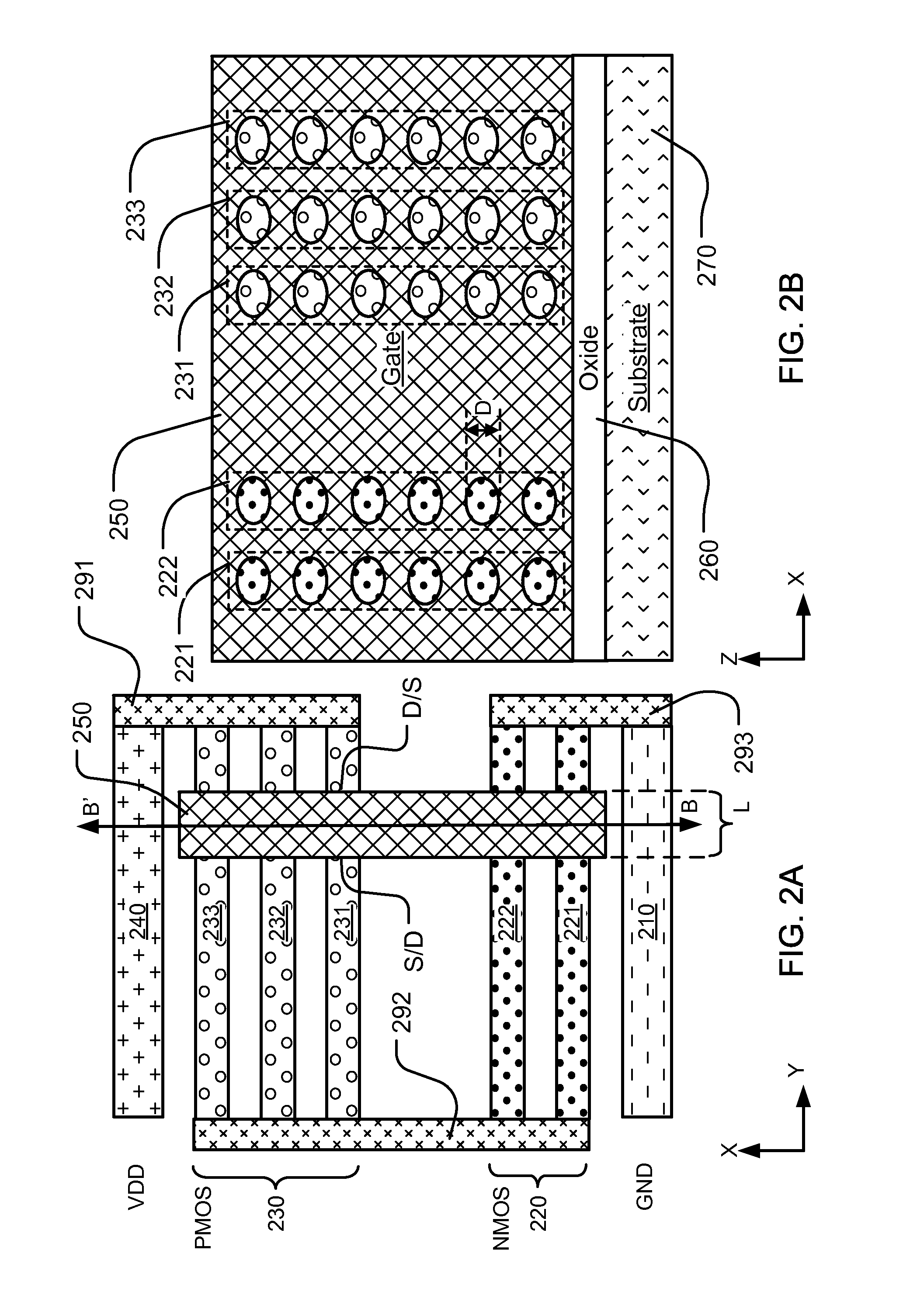

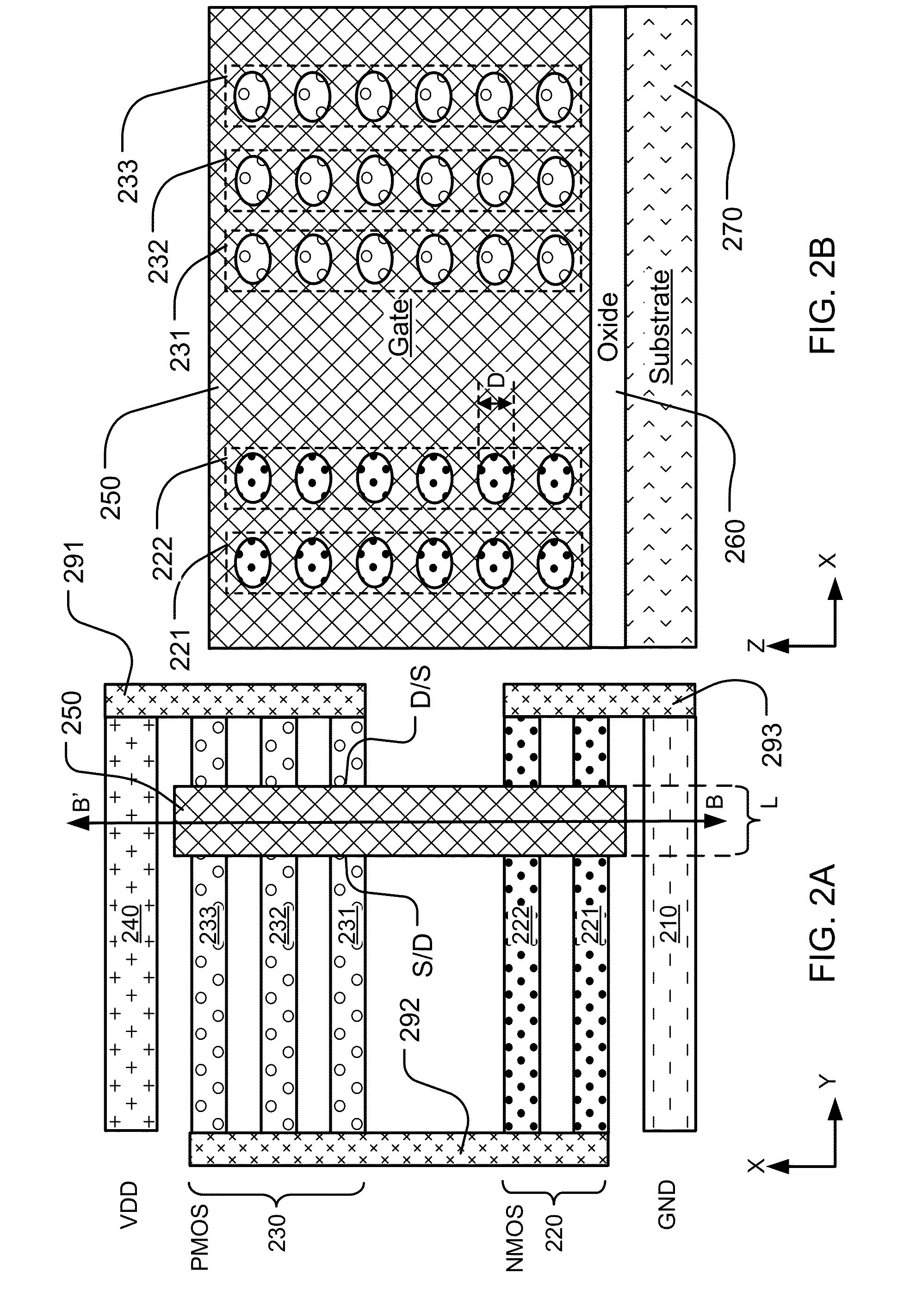

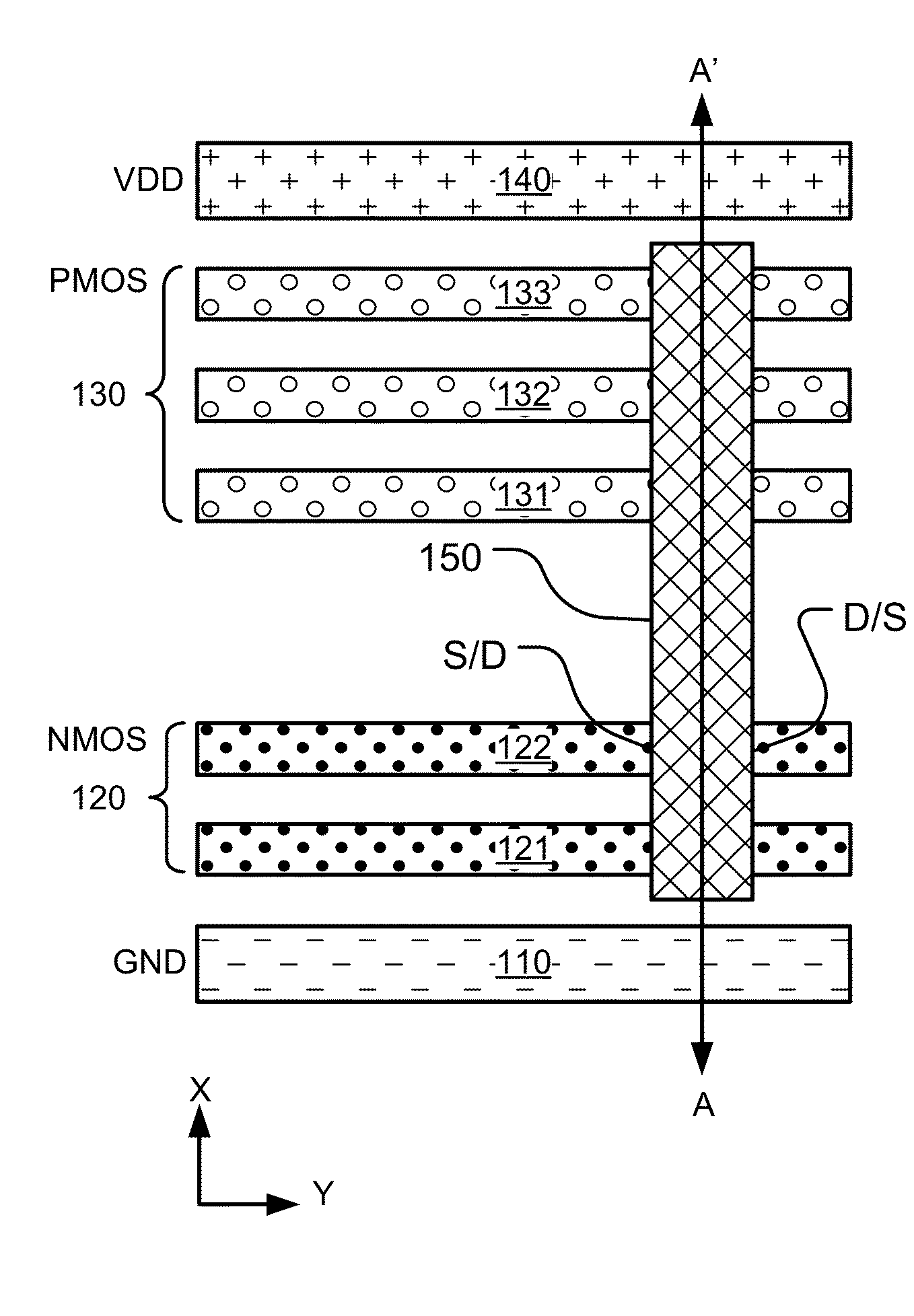

An integrated circuit design tool includes a cell library. An entry in the cell library comprises a specification of the cell including a first transistor and a second transistor. The first transistor can include a first set of nanowires or 2D material strips arranged in parallel to form a channel structure, and a gate conductor disposed across the first set of nanowires or 2D material strips. The second transistor can include a second set of nanowires or 2D material strips arranged in parallel to form a channel structure, and a gate conductor disposed across the first set of nanowires or 2D material strips. The number of nanowires or 2D material strips in the first set can be different from the number of nanowires or 2D material strips in the second set, so that the drive power of the individual transistors can be set with finer granularity.

Owner:SYNOPSYS INC

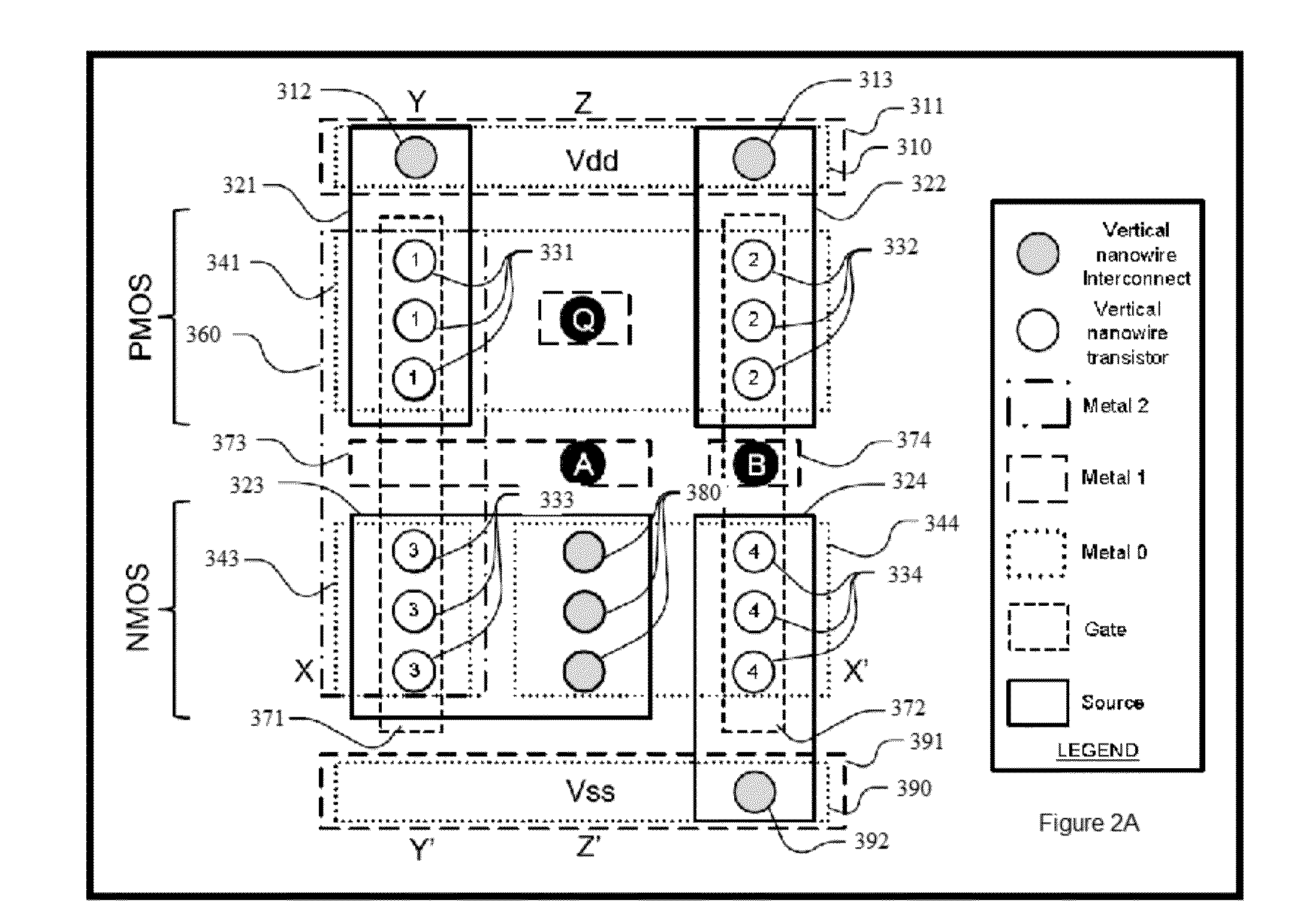

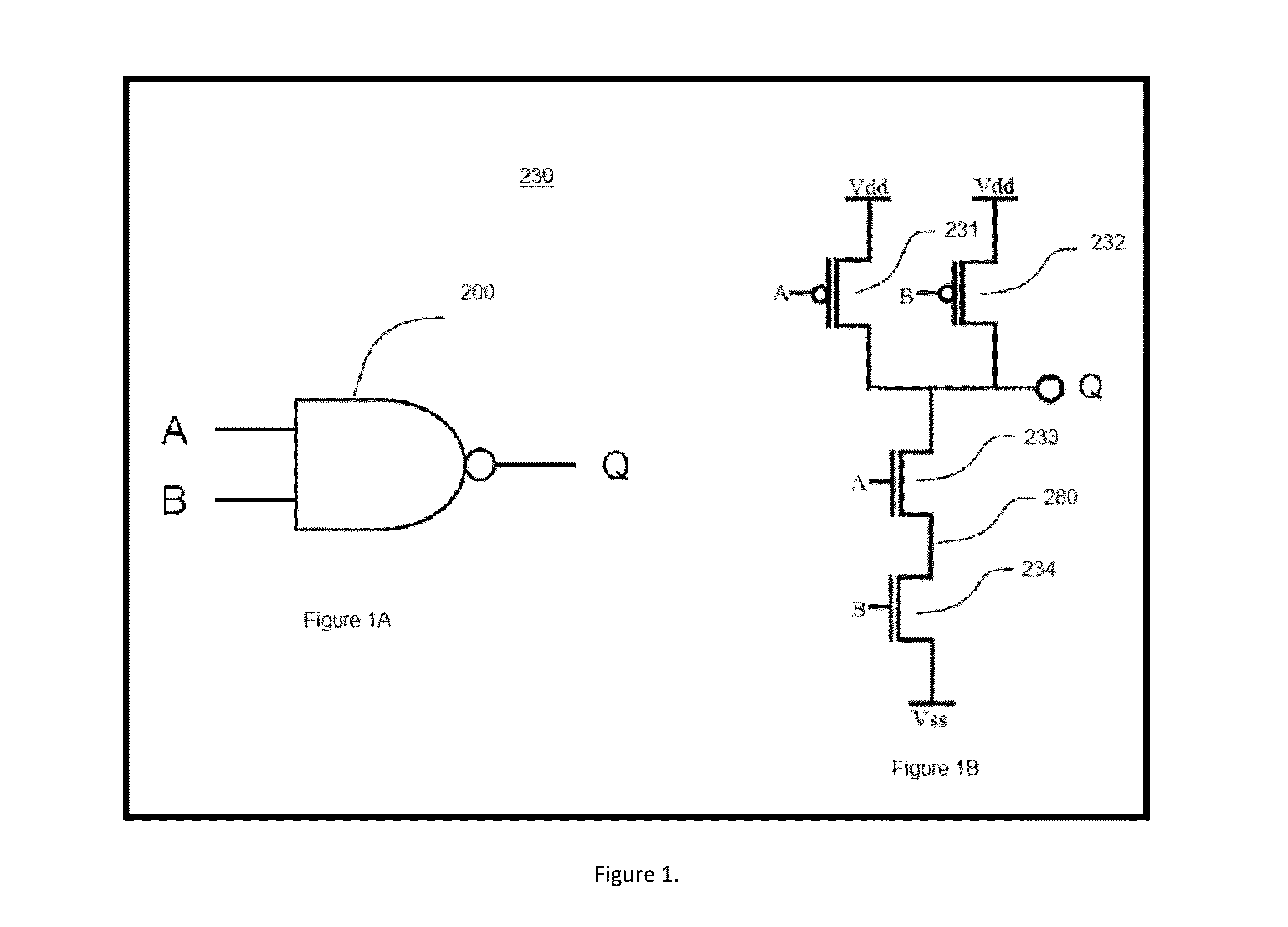

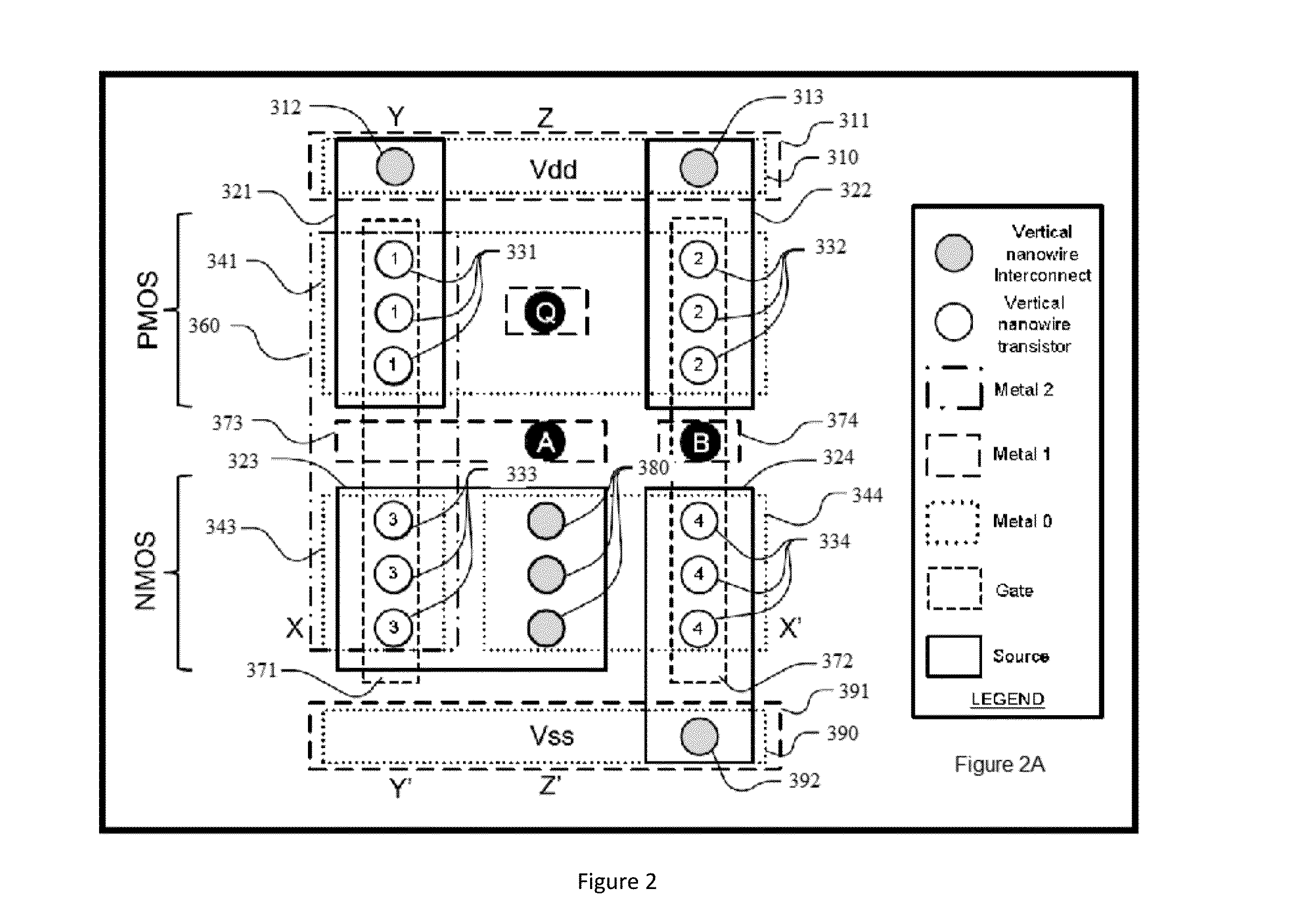

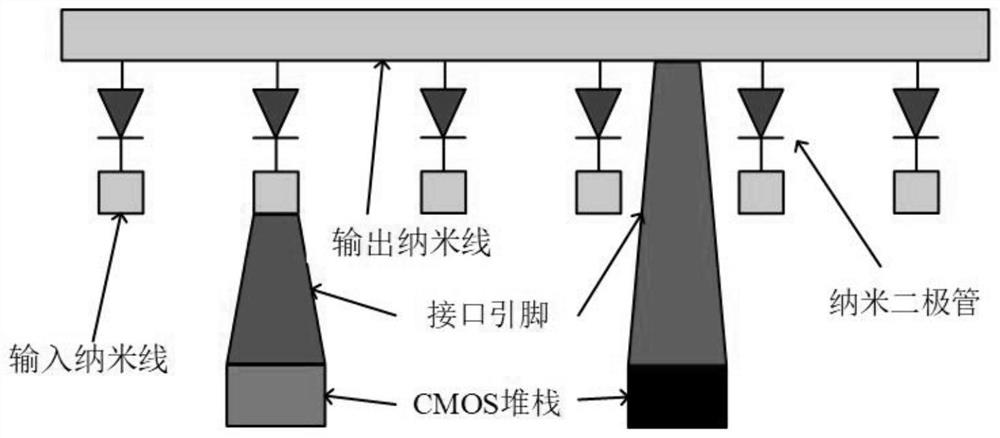

Arrays with compact series connection for vertical nanowires realizations

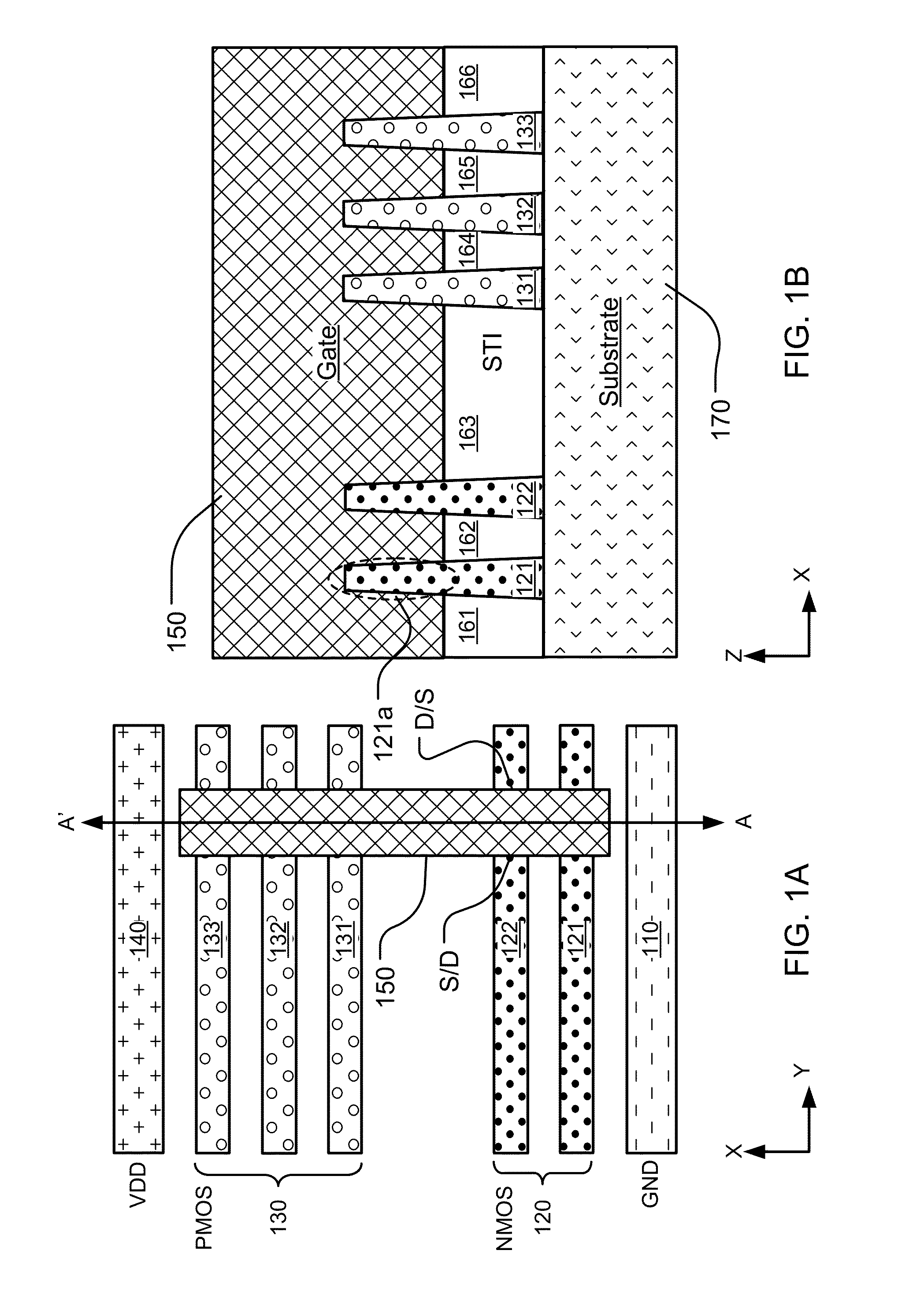

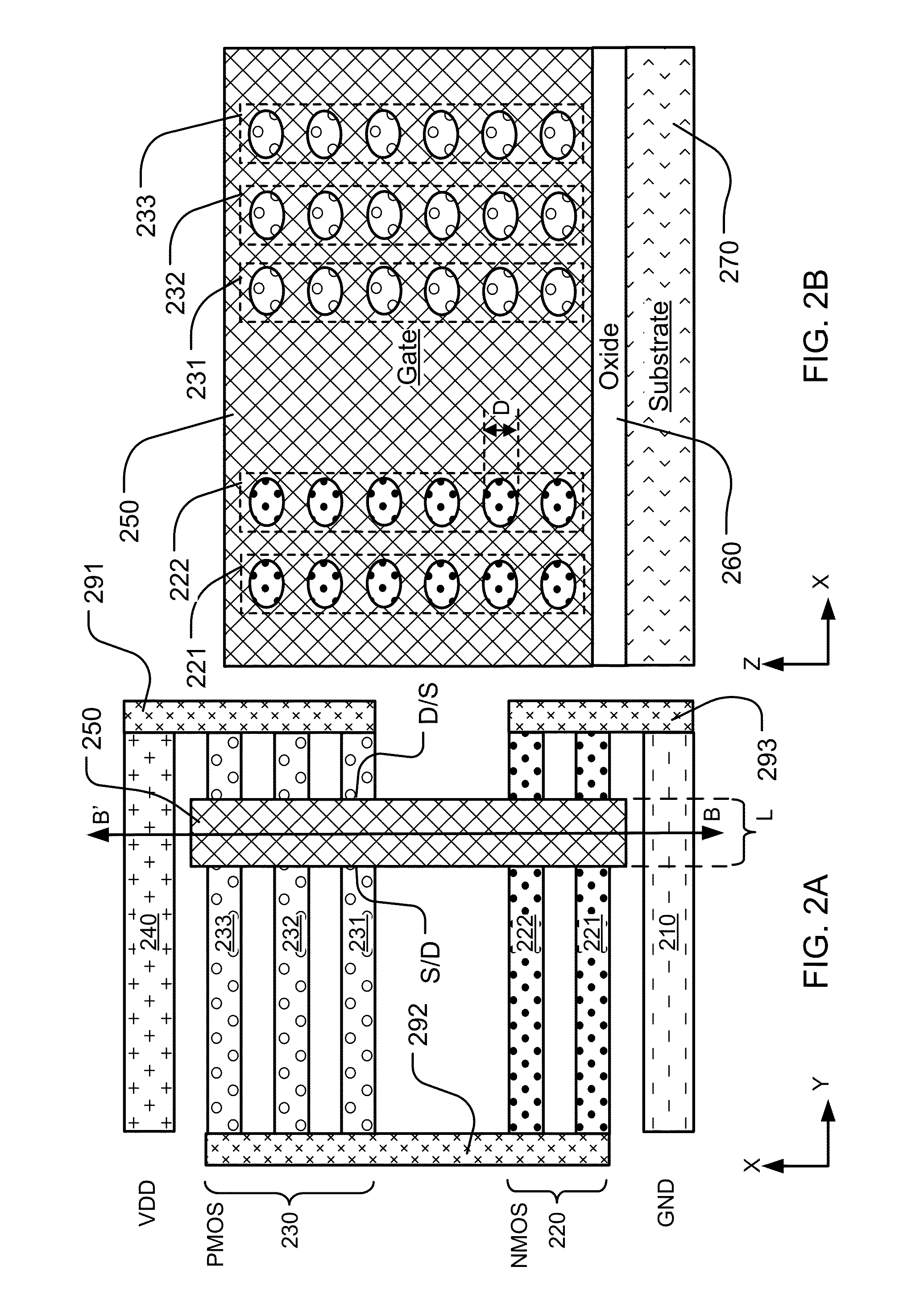

An integrated circuit design tool includes a functional cell library. An entry in the cell library comprises a specification of the cell. Entries in the cell library including specifications of particular cells in a computer executable language. At least one entry in the cell library comprising a specification of a cell including a plurality of transistors and an interconnect. At least two transistors in the plurality are in series via at least the interconnect. The transistors and the interconnect can be vertically oriented to support vertical current through a vertical channel relative to the substrate.

Owner:SYNOPSYS INC

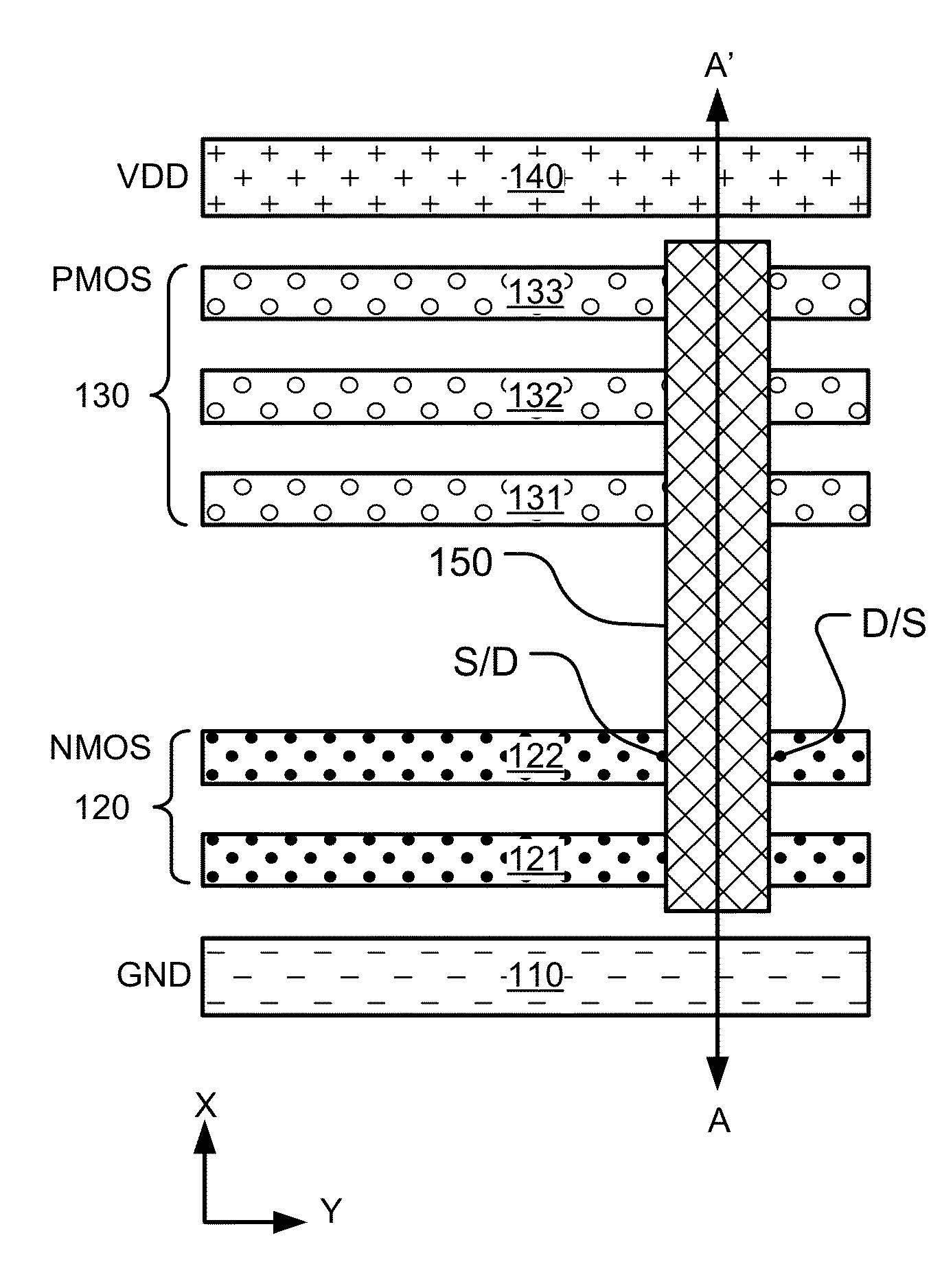

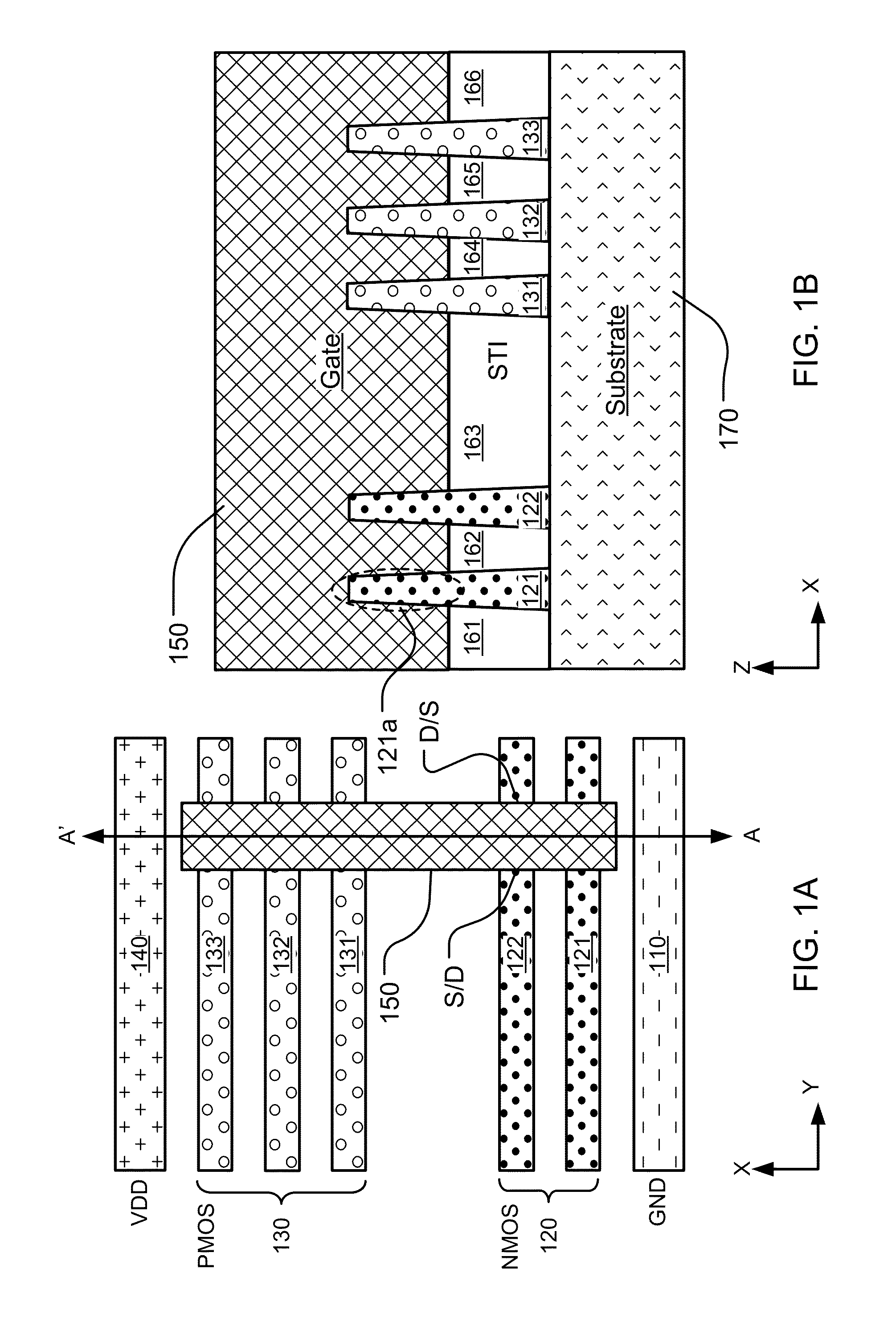

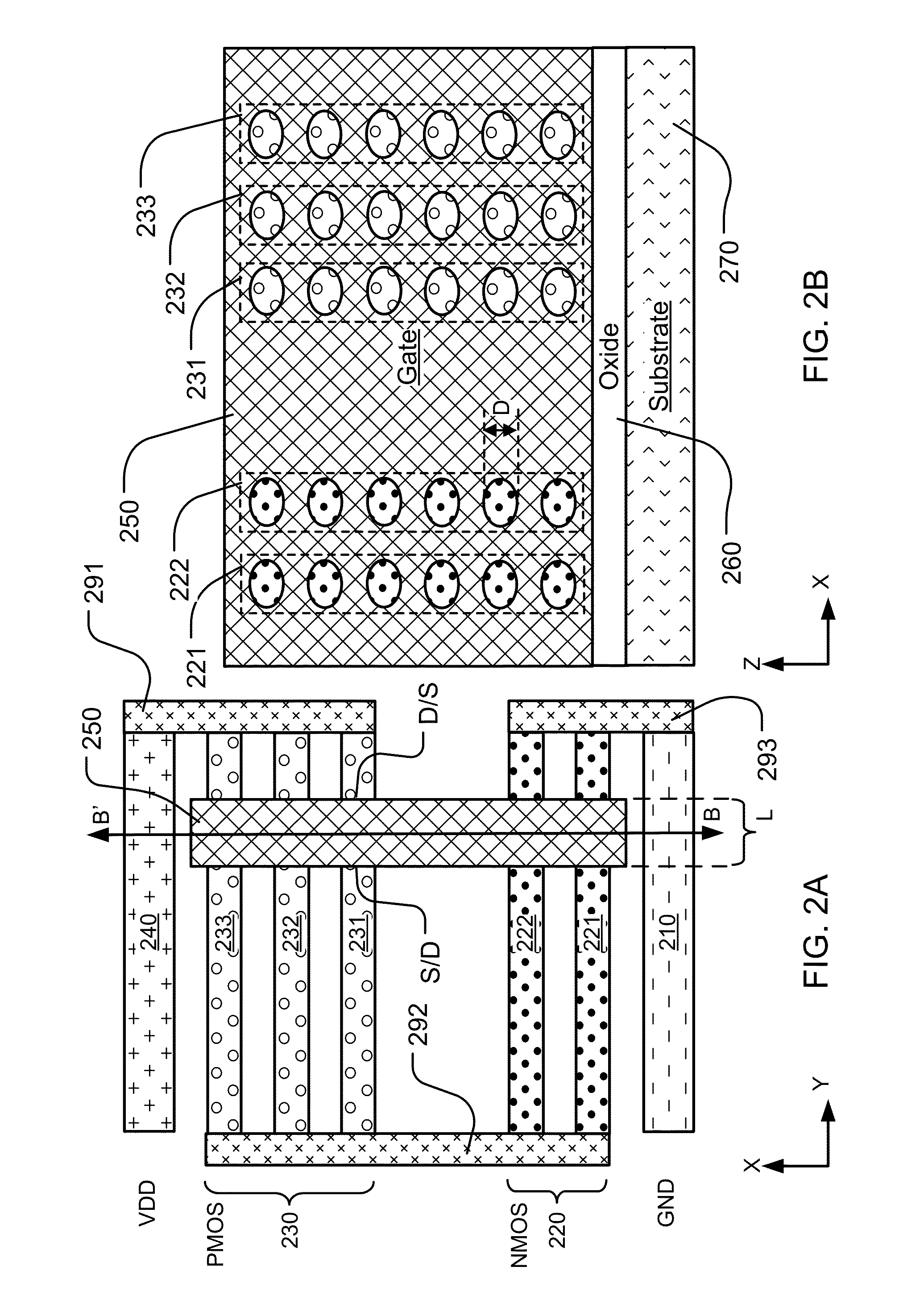

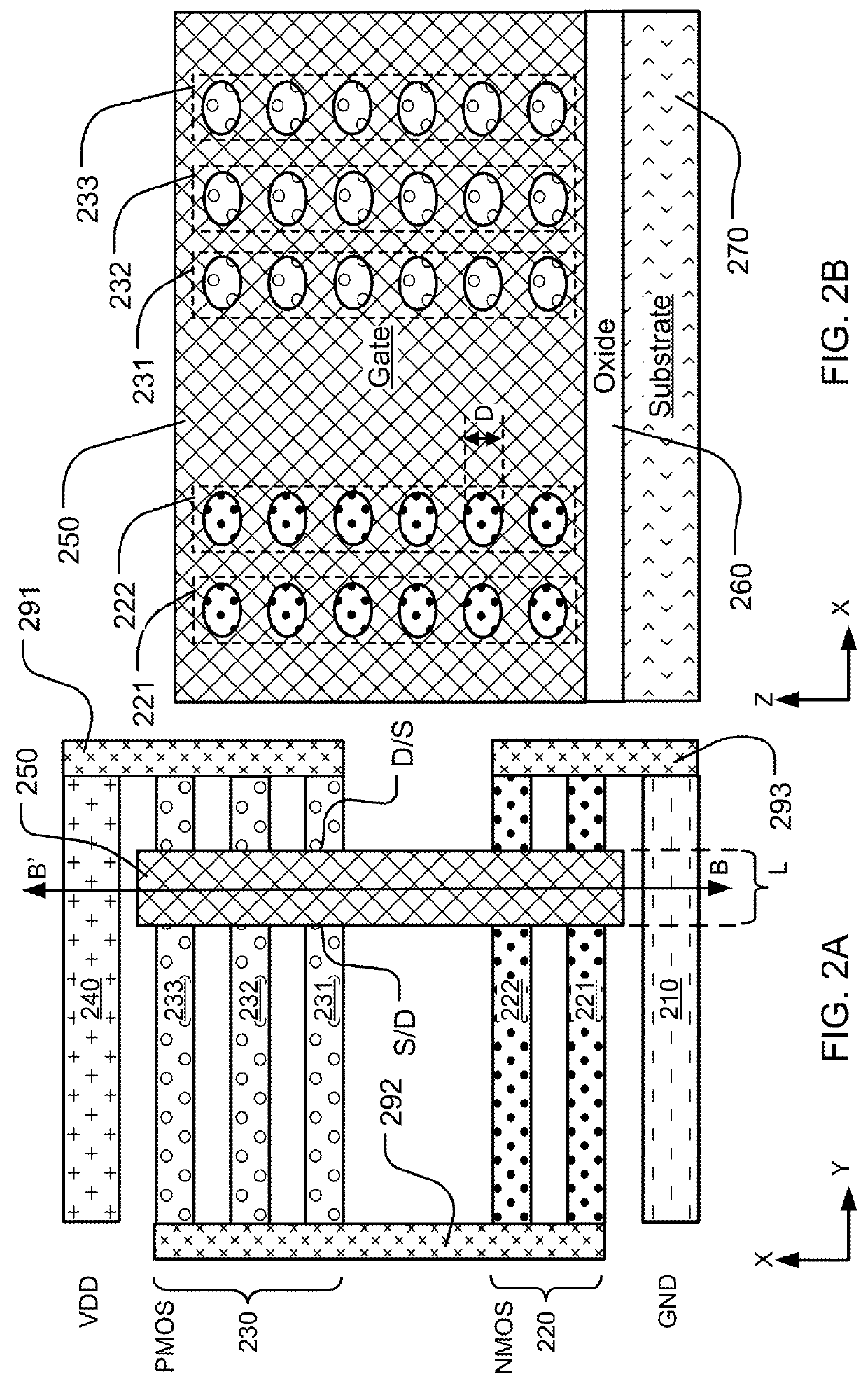

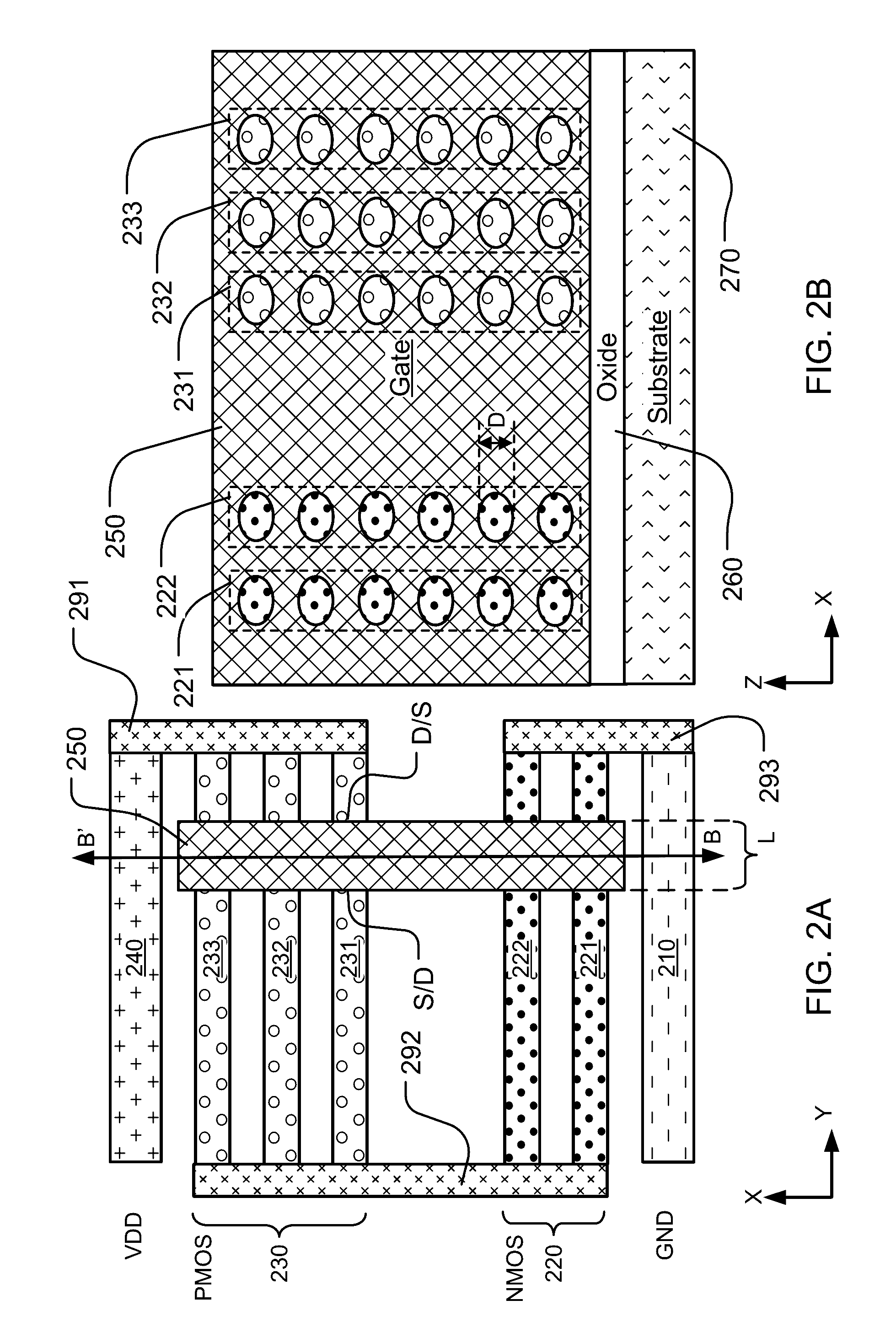

Nanowire or 2d material strips interconnects in an integrated circuit cell

ActiveUS20150370949A1Improve the level ofDifferent performanceTransistorSemiconductor/solid-state device detailsNanowireEngineering

An integrated circuit design tool includes a cell library. The cell library includes entries for a plurality of cells, entries in the cell library including specifications of particular cells in a computer executable language. At least one entry in the cell library can comprise a specification of physical structures and timing parameters of a circuit including a first transistor, a second transistor, and an interconnect connecting a terminal of the first transistor to a terminal of the second transistor, the interconnect comprising one or more nanowires or 2D material strips arranged in parallel. An integrated circuit including the circuit is described.

Owner:SYNOPSYS INC

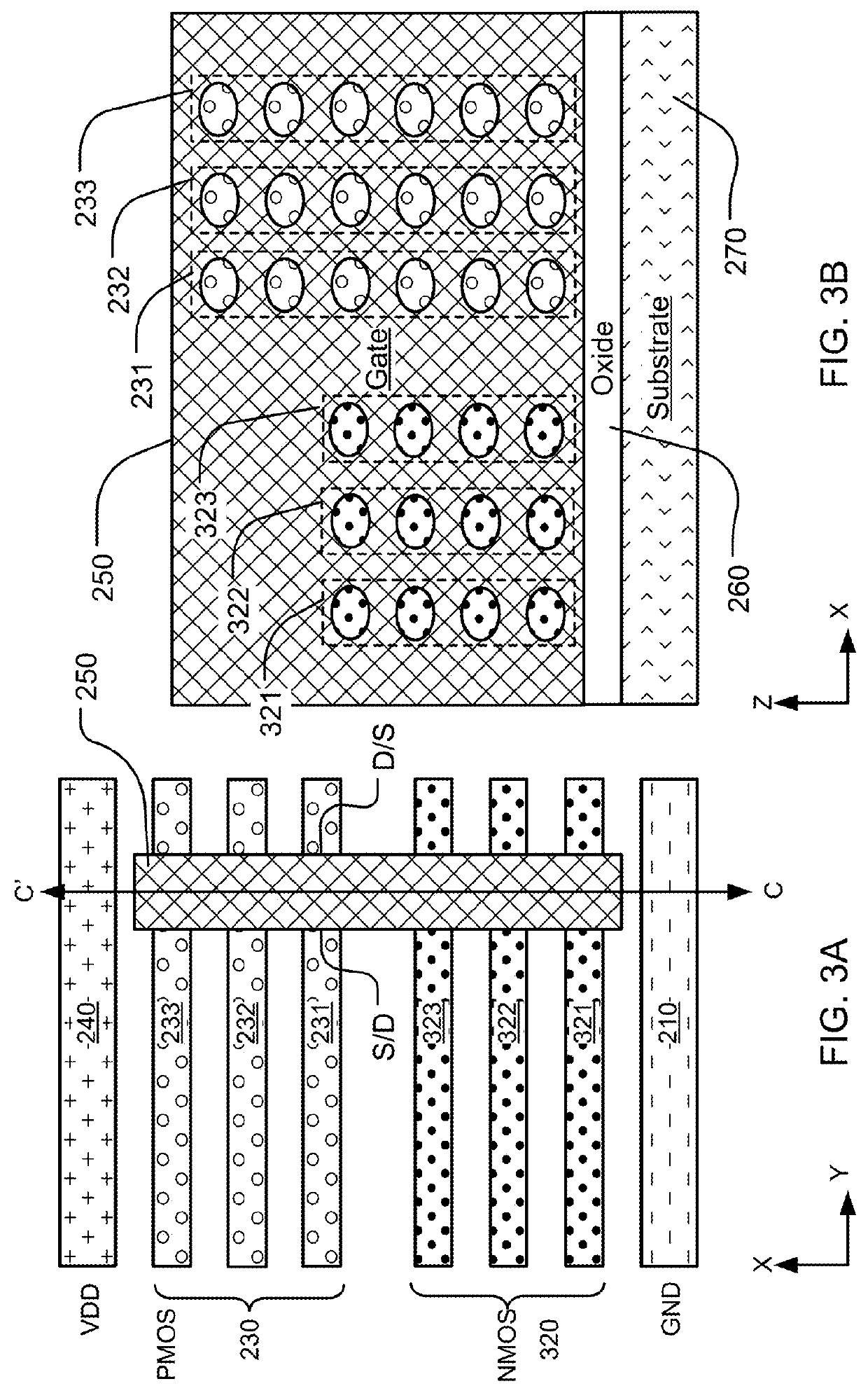

Cells having transistors and interconnects including nanowires or 2d material strips

ActiveUS20150370951A1Improve the level ofDifferent performanceTransistorNanoinformaticsNanowireEngineering

An integrated circuit design tool includes a cell library. The cell library includes entries for a plurality of cells, entries in the cell library including specifications of particular cells in a computer executable language. At least one entry in the cell library can comprise a specification of physical structures and timing parameters of a plurality of transistors and an interconnect; wherein a transistor in the plurality has a channel comprising one or more nanowires or 2D material strips arranged in parallel, and the interconnect comprises one or more nanowires or 2D material strips arranged in parallel and connected to terminals of more than one of the transistors in the plurality of transistors. An integrated circuit including the plurality of transistors and the interconnect is described.

Owner:SYNOPSYS INC

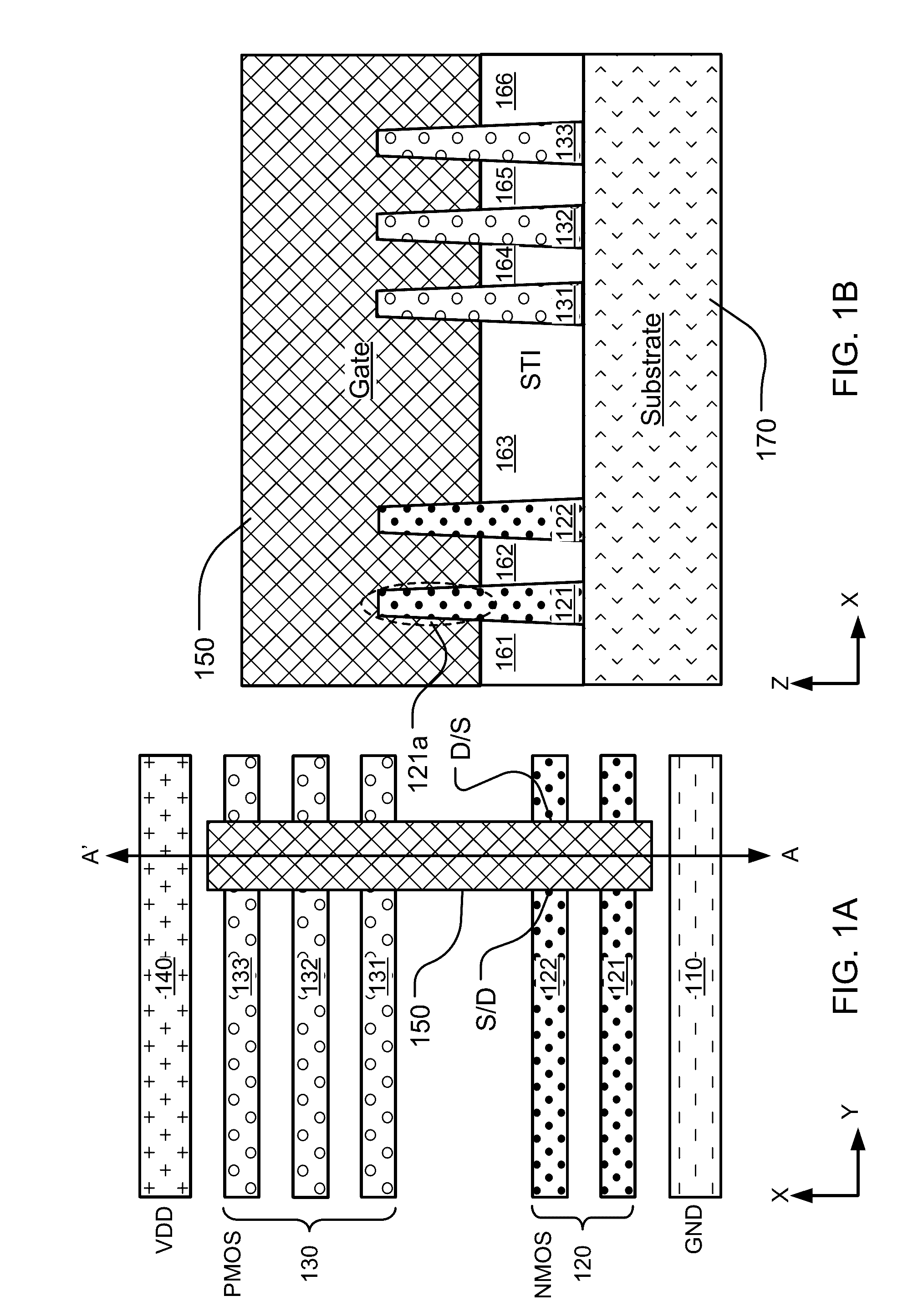

Memory cells having transistors with different numbers of nanowires or 2d material strips

InactiveUS20150370948A1Improve the level ofDifferent performanceTransistorSemiconductor/solid-state device detailsIntegrated circuitEngineering

An integrated circuit design tool includes a cell library. The cell library includes entries for a plurality of cells, entries in the cell library including specifications of particular cells in a computer executable language. At least one entry in the cell library can comprise a specification of physical structures and timing parameters of a memory cell including a plurality of transistors, at least some of the transistors in the plurality having channels comprising respective sets of one or more nanowires or 2D material strips, and wherein the channel of one of the transistors in the plurality has a different number of nanowires or 2D material strips than a channel of another transistor in the plurality. An integrated circuit including the memory cell is described.

Owner:SYNOPSYS INC

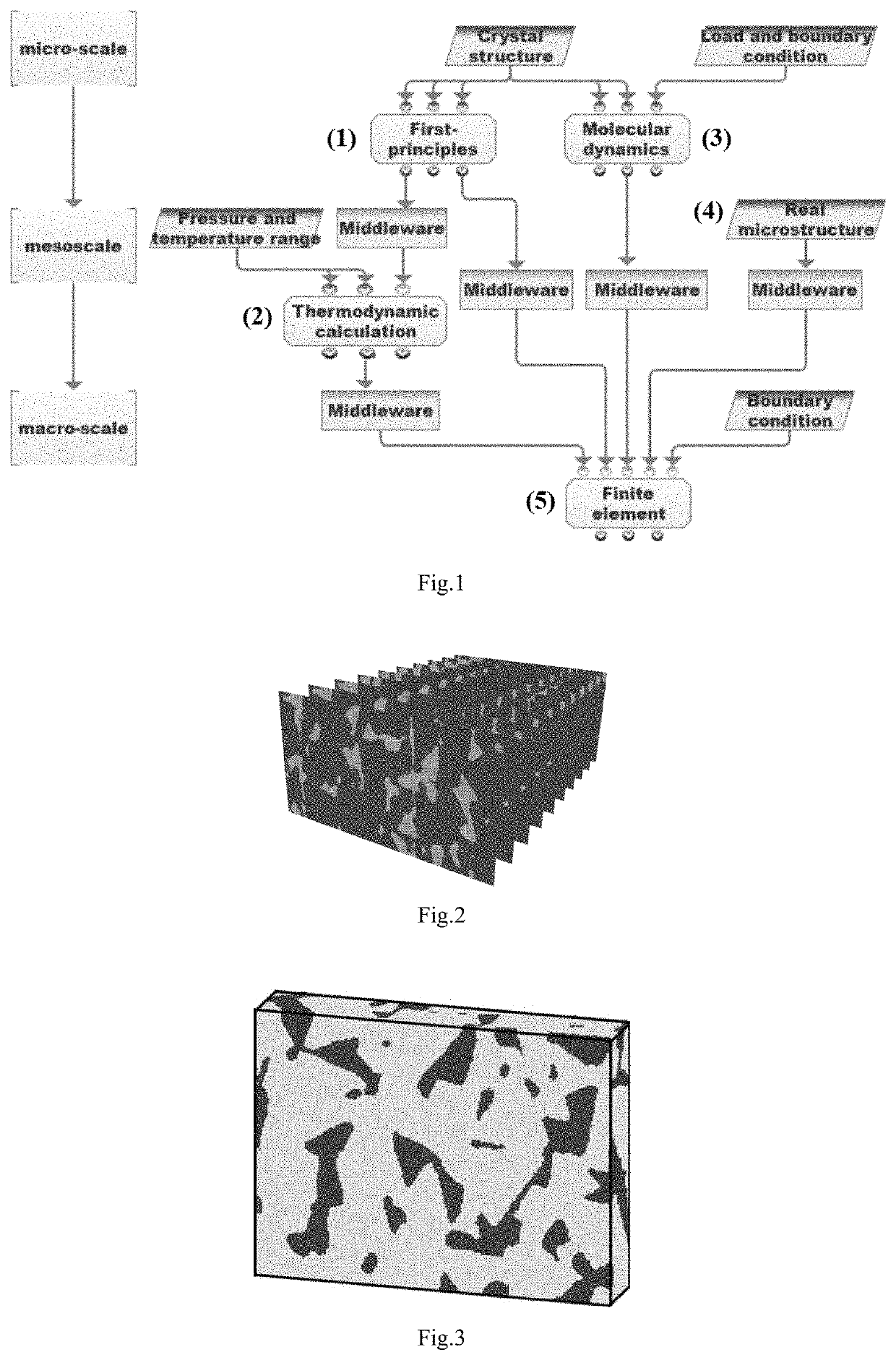

Multi-scale method for simulating mechanical behaviors of multiphase composite materials

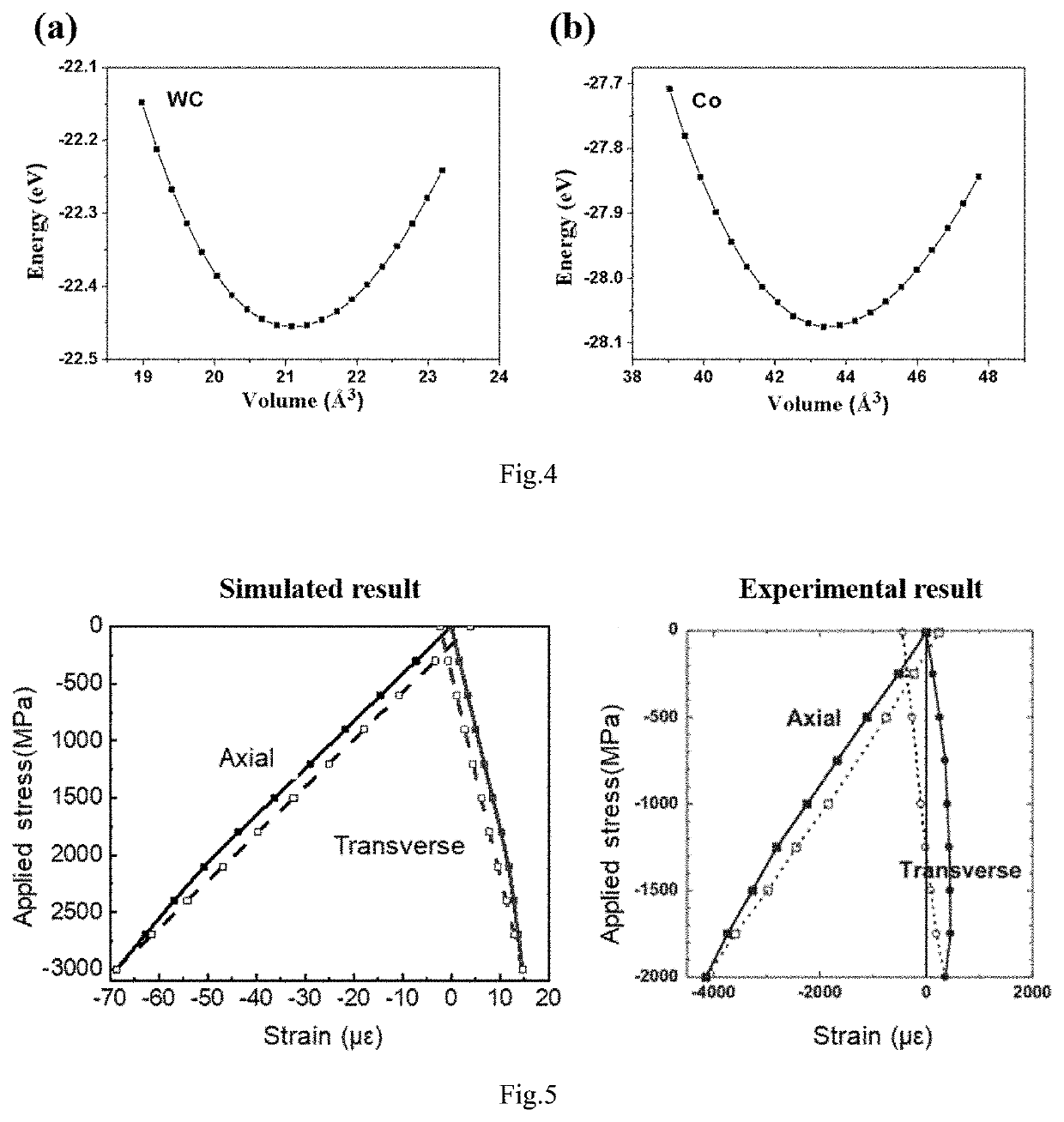

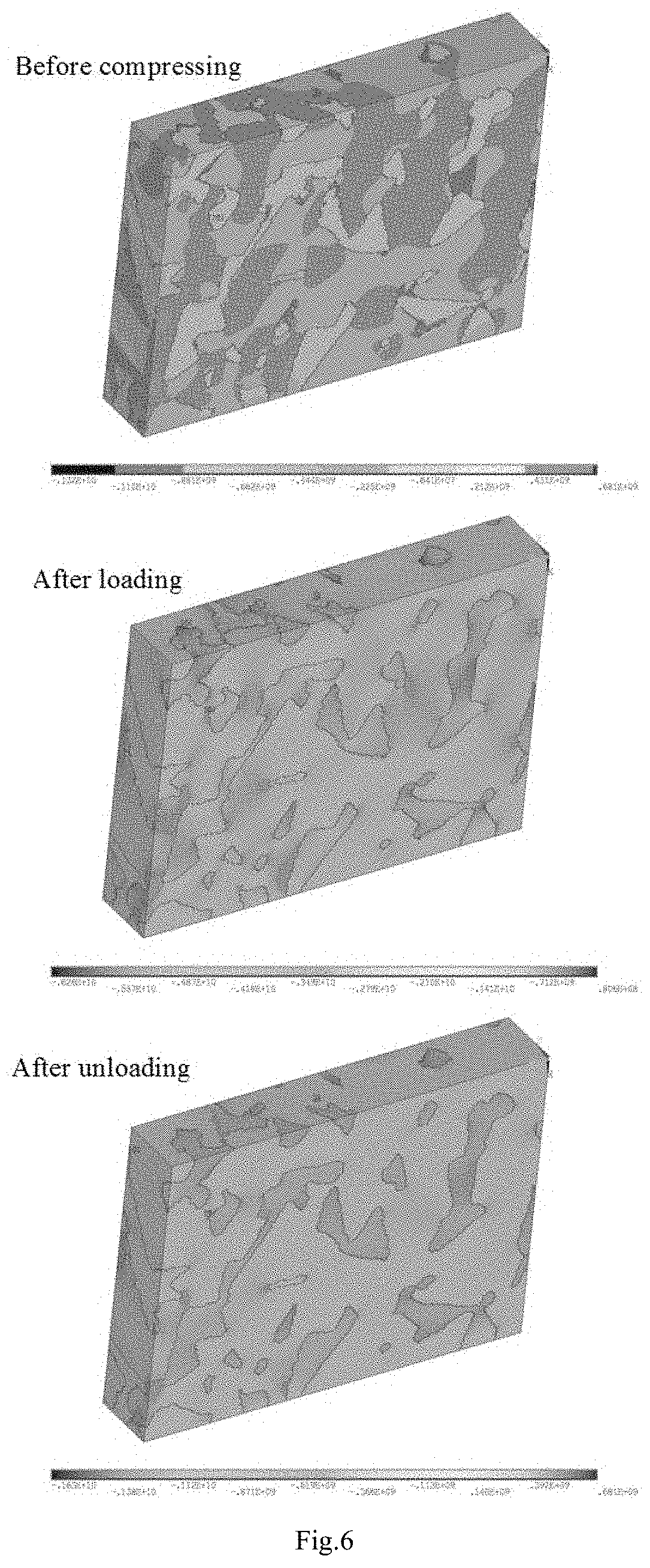

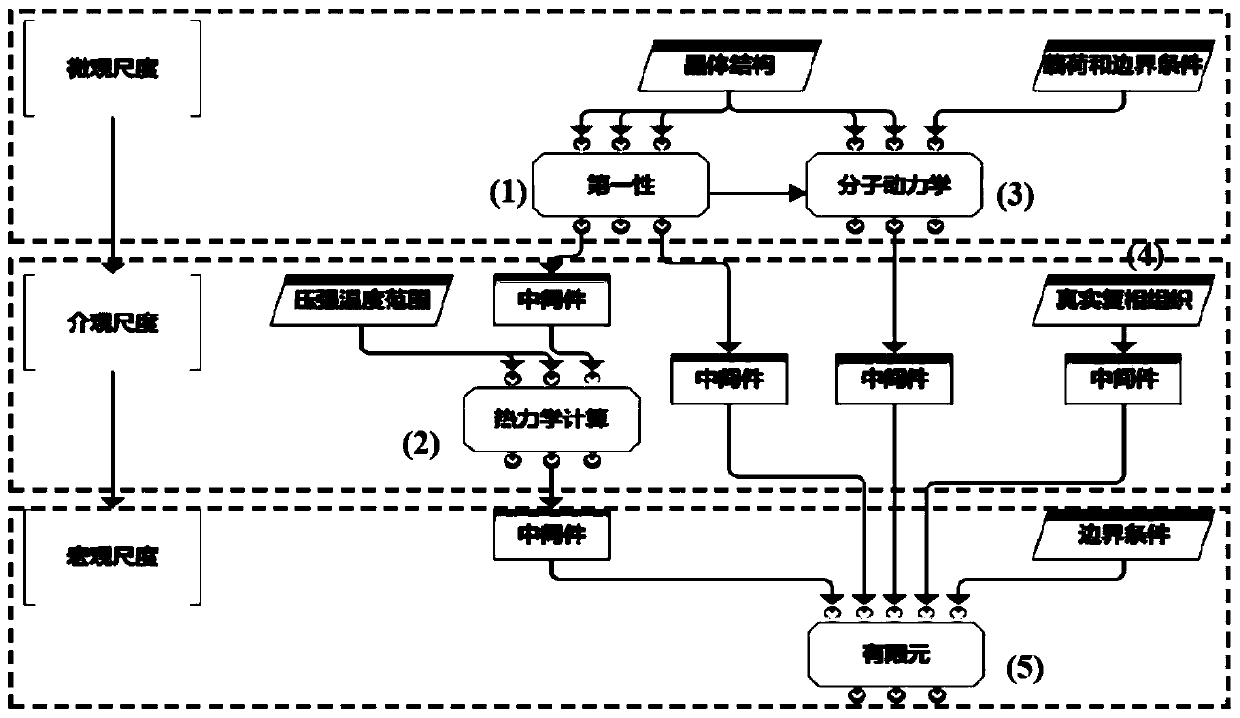

PendingUS20210118530A1Plasticity of hard and brittle ceramic phase is negligibleWay accurateChemical property predictionDesign optimisation/simulationMicro structureMacroscopic scale

A computer simulation analysis method suitable for describing the mechanical behavior of multiphase composites based on the real microstructure of materials relates to a multidisciplinary field such as computational material science, simulation and high throughput calculation. Through the first-principles calculation under nano scale, the molecular dynamics simulation under micro scale, and the thermodynamic calculation under mesoscopic scale, various physical parameters needed for the finite element simulation under macro scale can be obtained, including the elastic and plastic physical parameters of each phase in the composite at different temperature and different grain sizes. Focused ion beam experiment and image processing are adopted to obtain real material microstructure. Through the parameter coupling and parameter transfer among the calculated results of various scales, combining the microstructure of the material, stress-strain relationship, stress distribution and its evolution law, plastic deformation and other mechanical behaviors of the multiphase composites under complex stress and different temperature can be simulated.

Owner:BEIJING UNIVERSITRY OF TECH

Multi-scale simulation method for mechanical behaviors of multi-phase composite material

ActiveCN110210103AImprove continuityRealize simulationChemical property predictionDesign optimisation/simulationMacroscopic scaleFirst principle

Owner:BEIJING UNIV OF TECH

Cells having transistors and interconnects including nanowires or 2D material strips

An integrated circuit design tool includes a cell library. The cell library includes entries for a plurality of cells, entries in the cell library including specifications of particular cells in a computer executable language. At least one entry in the cell library can comprise a specification of physical structures and timing parameters of a plurality of transistors and an interconnect; wherein a transistor in the plurality has a channel comprising one or more nanowires or 2D material strips arranged in parallel, and the interconnect comprises one or more nanowires or 2D material strips arranged in parallel and connected to terminals of more than one of the transistors in the plurality of transistors. An integrated circuit including the plurality of transistors and the interconnect is described.

Owner:SYNOPSYS INC

Nanowire or 2D material strips interconnects in an integrated circuit cell

ActiveUS9361418B2Fine granularityImprove the level ofTransistorSemiconductor/solid-state device detailsNanowireEngineering

An integrated circuit design tool includes a cell library. The cell library includes entries for a plurality of cells, entries in the cell library including specifications of particular cells in a computer executable language. At least one entry in the cell library can comprise a specification of physical structures and timing parameters of a circuit including a first transistor, a second transistor, and an interconnect connecting a terminal of the first transistor to a terminal of the second transistor, the interconnect comprising one or more nanowires or 2D material strips arranged in parallel. An integrated circuit including the circuit is described.

Owner:SYNOPSYS INC

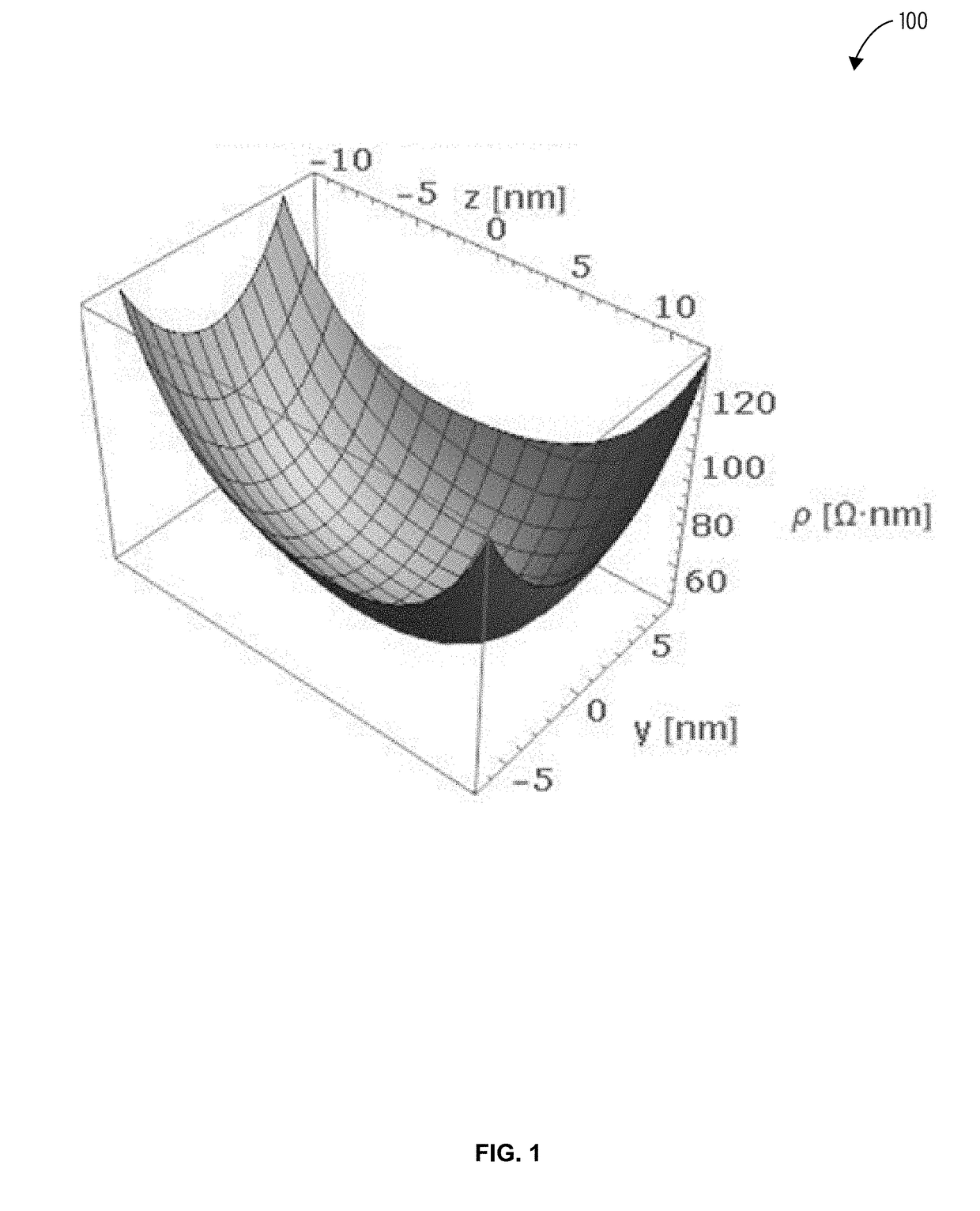

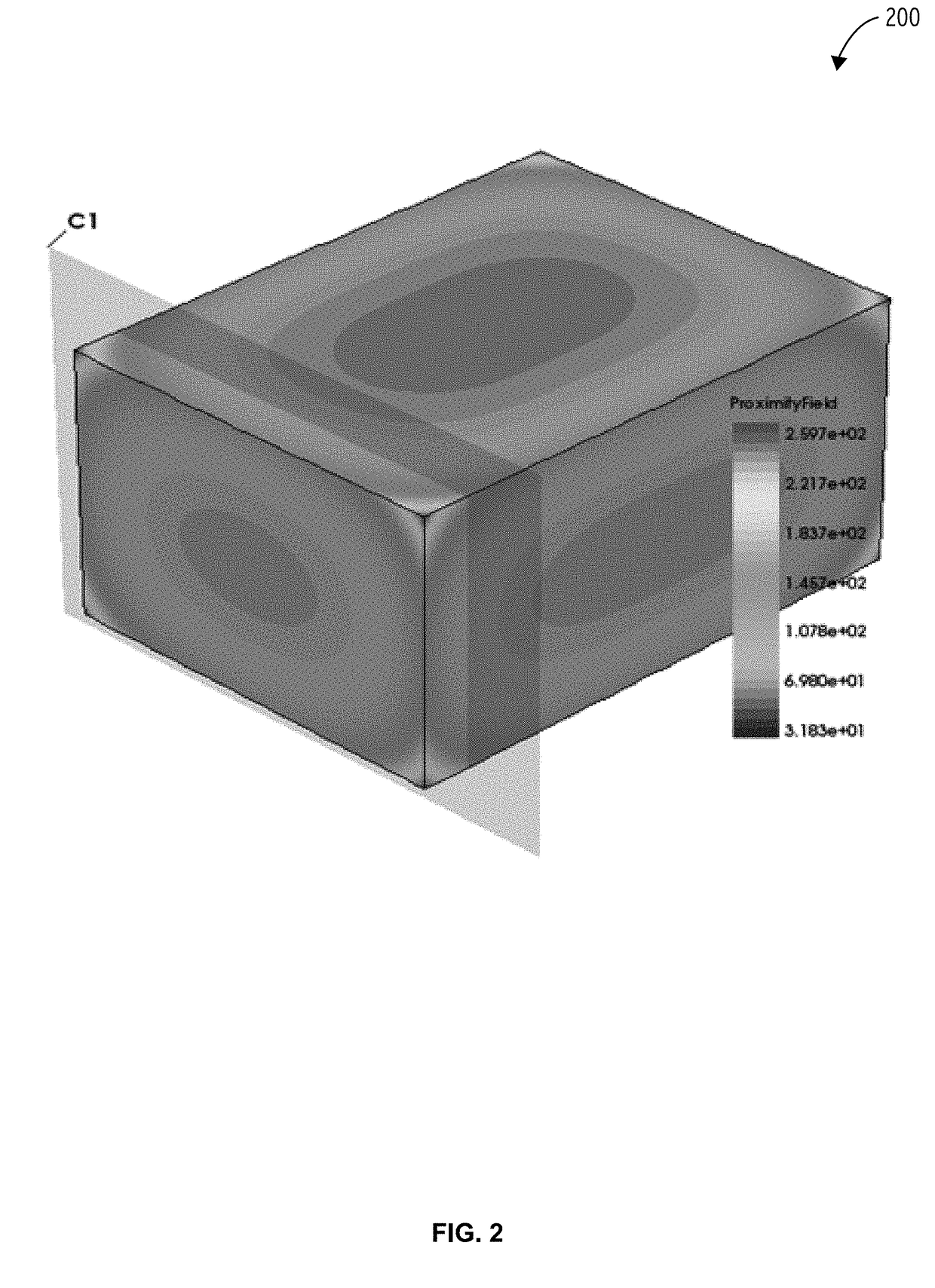

Nano-wire resistance model

ActiveUS20180157783A1Improve efficiencyReduced processing resourceSemiconductor/solid-state device detailsCAD circuit designElectrical resistance and conductanceComputerized system

An integrated circuit design tool for modeling resistance of an interconnect specifies a structure of the interconnect in a data structure in memory in or accessible by the computer system using 3D coordinate system. For each of a plurality of volume elements in the specified structure, the tool specifies a location and one of first and second materials of the interconnect having specified resistivities, and for each volume element generates a model resistivity for the volume element as a function of resistivity of volume elements within a neighborhood of the volume element and a specified transition region length λ.

Owner:SYNOPSYS INC

Cells having transistors and interconnects including nanowires or 2d material strips

ActiveUS20160329313A1Fine granularityImprove the level ofTransistorNanoinformaticsNanowireEngineering

An integrated circuit design tool includes a cell library. The cell library includes entries for a plurality of cells, entries in the cell library including specifications of particular cells in a computer executable language. At least one entry in the cell library can comprise a specification of physical structures and timing parameters of a plurality of transistors and an interconnect; wherein a transistor in the plurality has a channel comprising one or more nanowires or 2D material strips arranged in parallel, and the interconnect comprises one or more nanowires or 2D material strips arranged in parallel and connected to terminals of more than one of the transistors in the plurality of transistors. An integrated circuit including the plurality of transistors and the interconnect is described.

Owner:SYNOPSYS INC

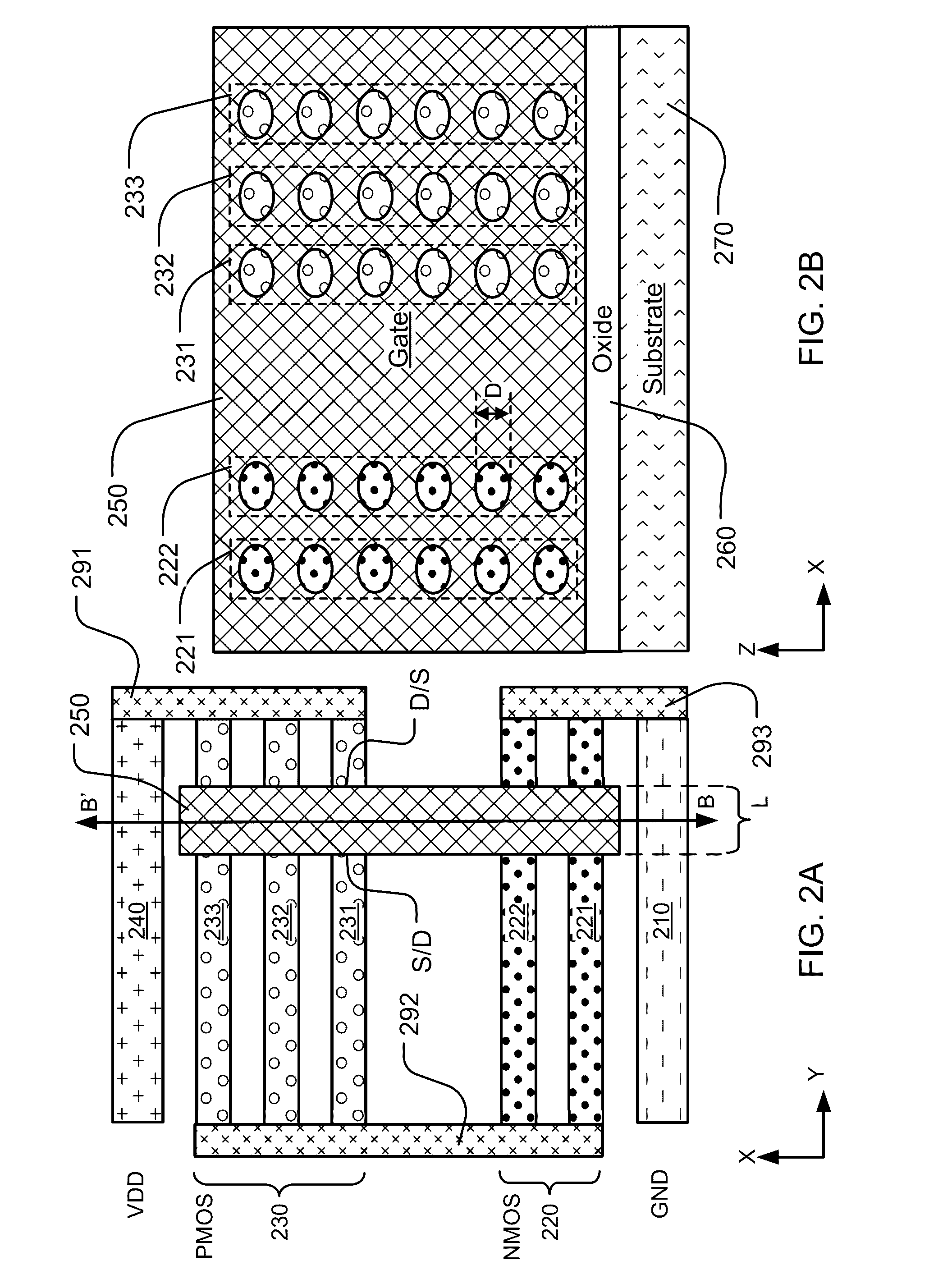

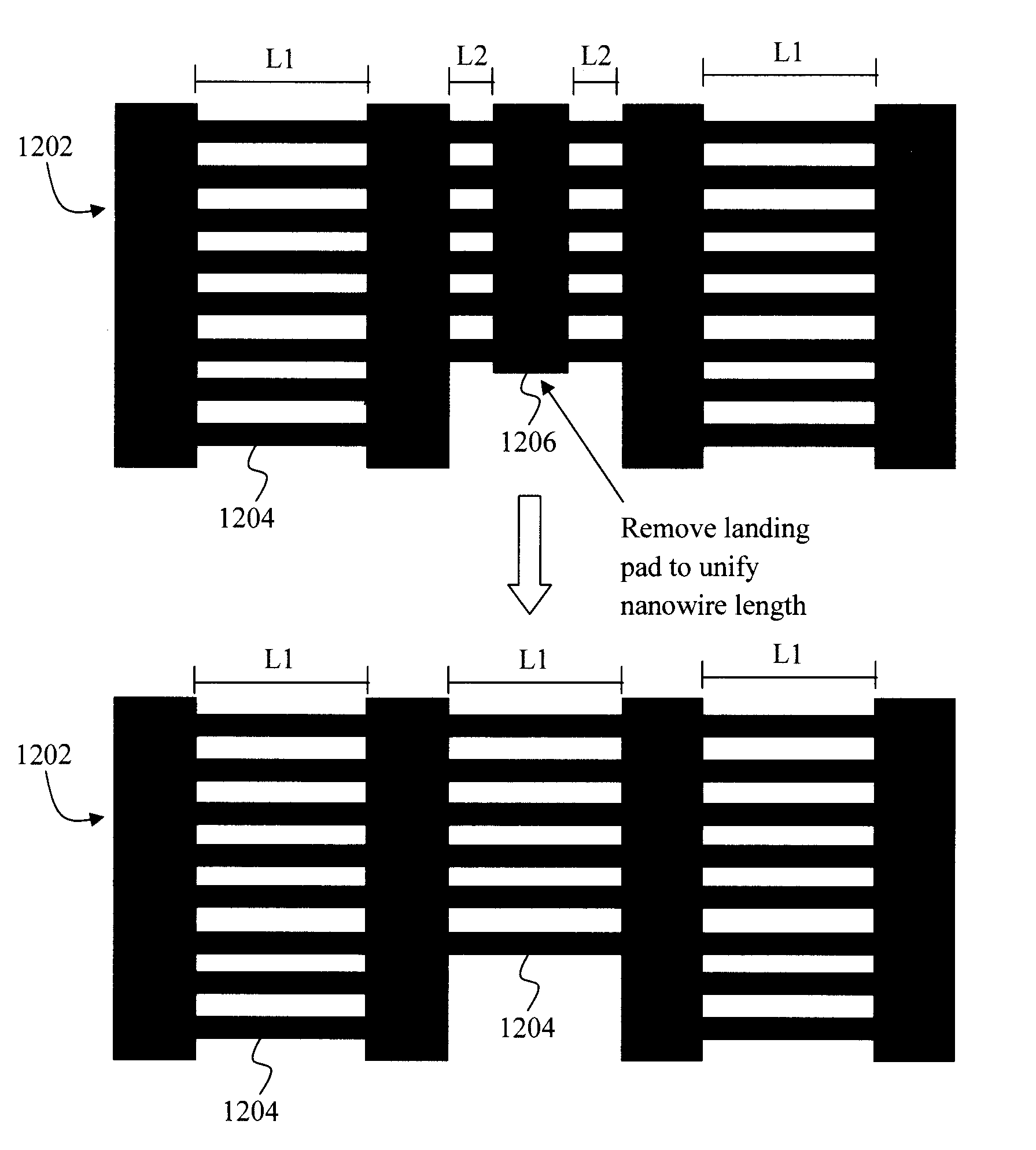

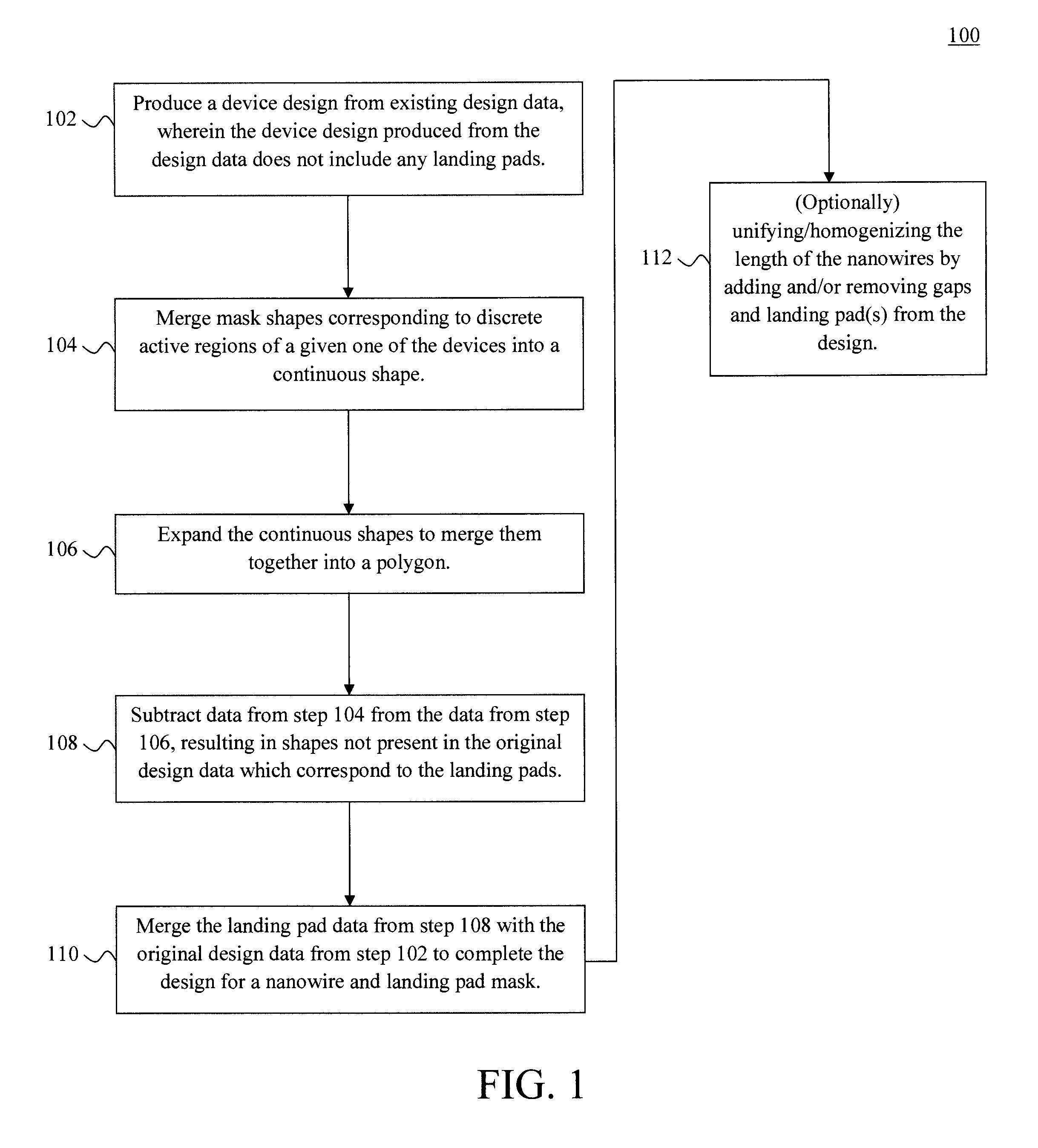

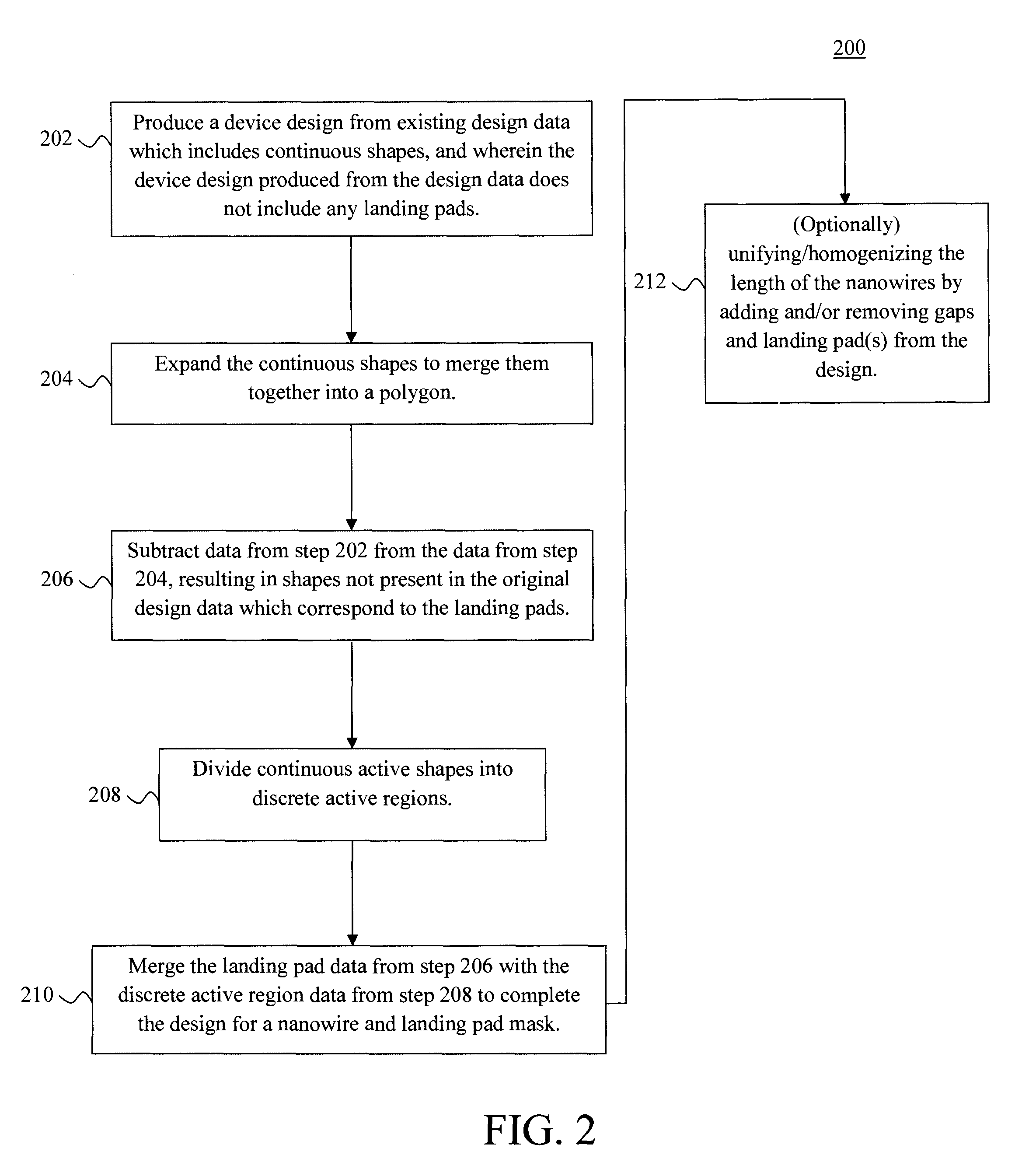

Techniques for Generating Nanowire Pad Data from Pre-Existing Design Data

InactiveUS20150356223A1Semiconductor/solid-state device manufacturingCAD circuit designPre-existingCMOS

In one aspect, a CAD-based method for designing a lithographic mask for nanowire-based devices is provided which includes the steps of: create a design for the mask from existing (e.g., FINFET or planar CMOS) design data which includes, for each of the devices, one or more nanowire mask shapes (FINFET design data) or continuous shapes (planar CMOS design data); for FINFET design data, merging the nanowire mask shapes into continuous shapes; expanding the continuous shapes to join all of the continuous shapes in the design together forming a single polygon shape; removing the continuous shapes from the single polygon shape resulting in landing pad shapes for anchoring the nanowire mask shapes; for CMOS design data, dividing the continuous active shapes into one or more nanowire mask shapes; and merging the landing pad shapes with the nanowire mask shapes to form the lithographic mask.

Owner:IBM CORP

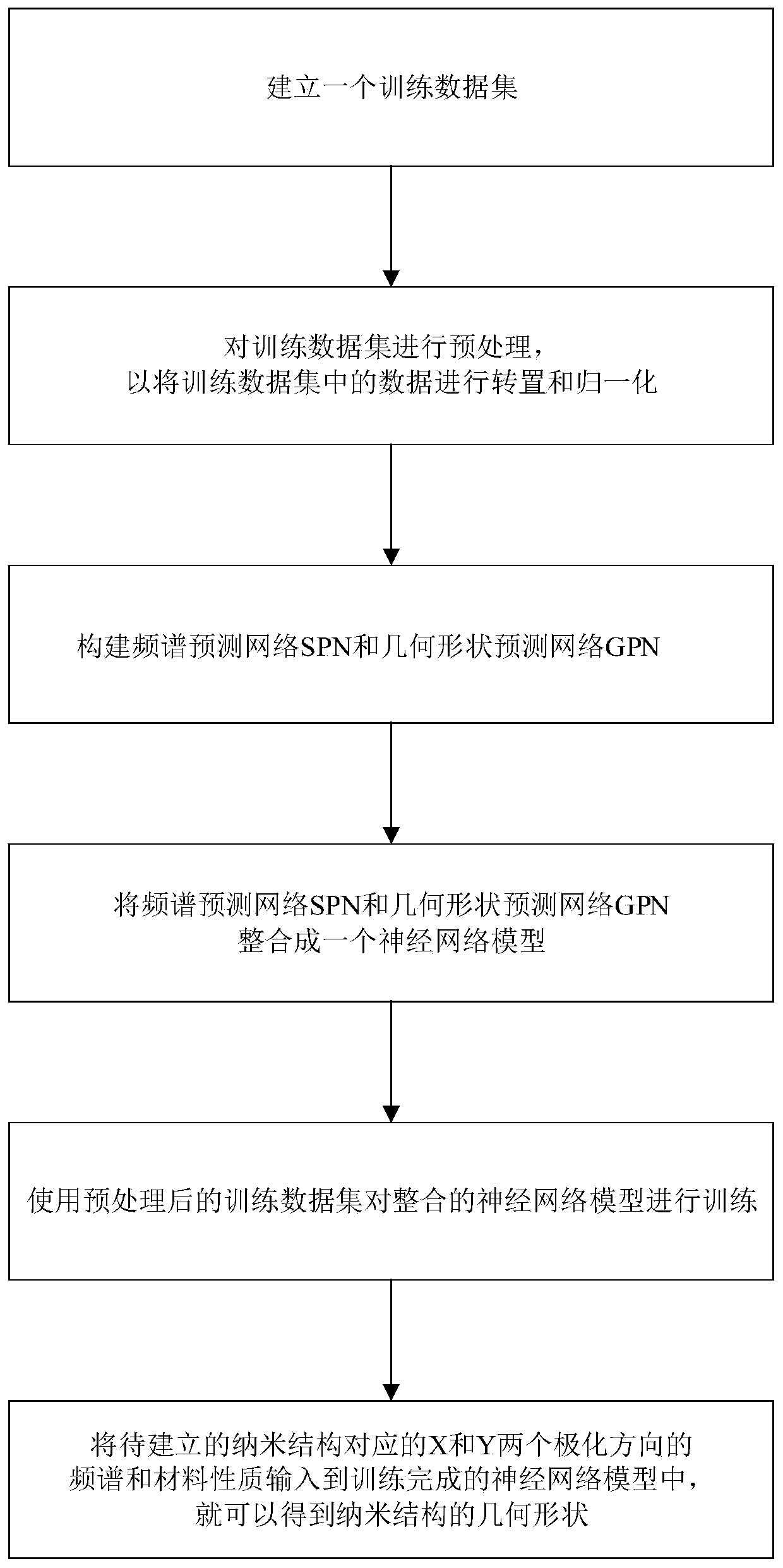

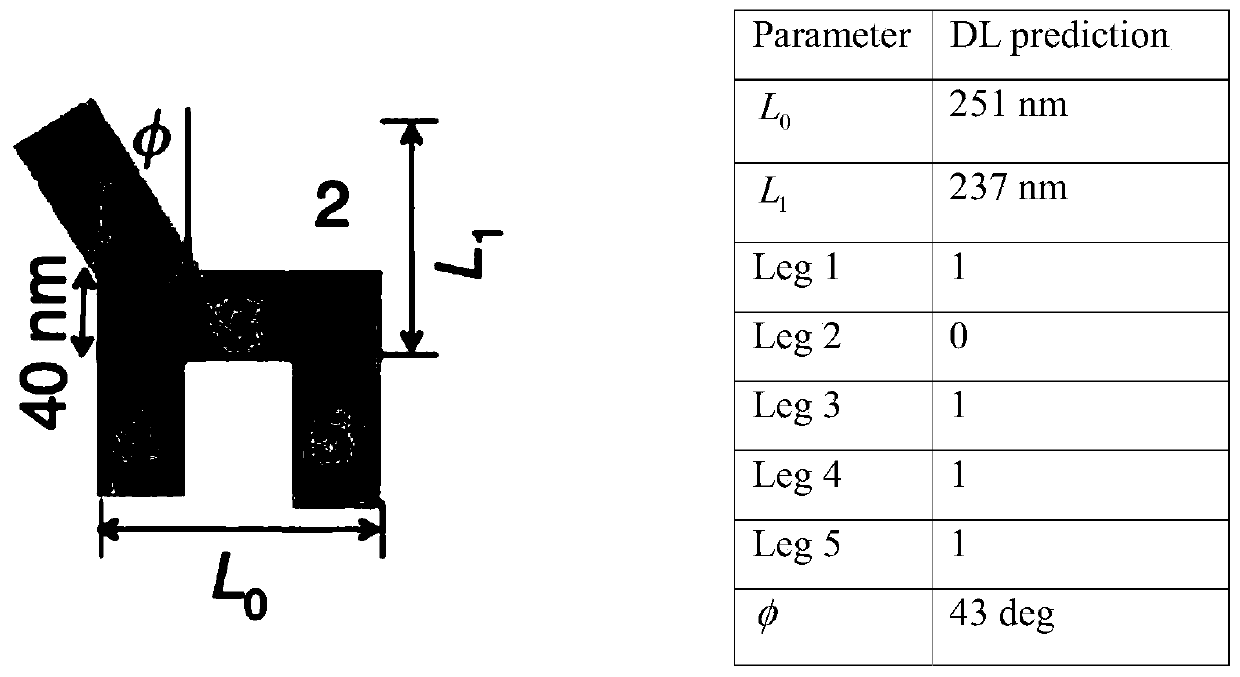

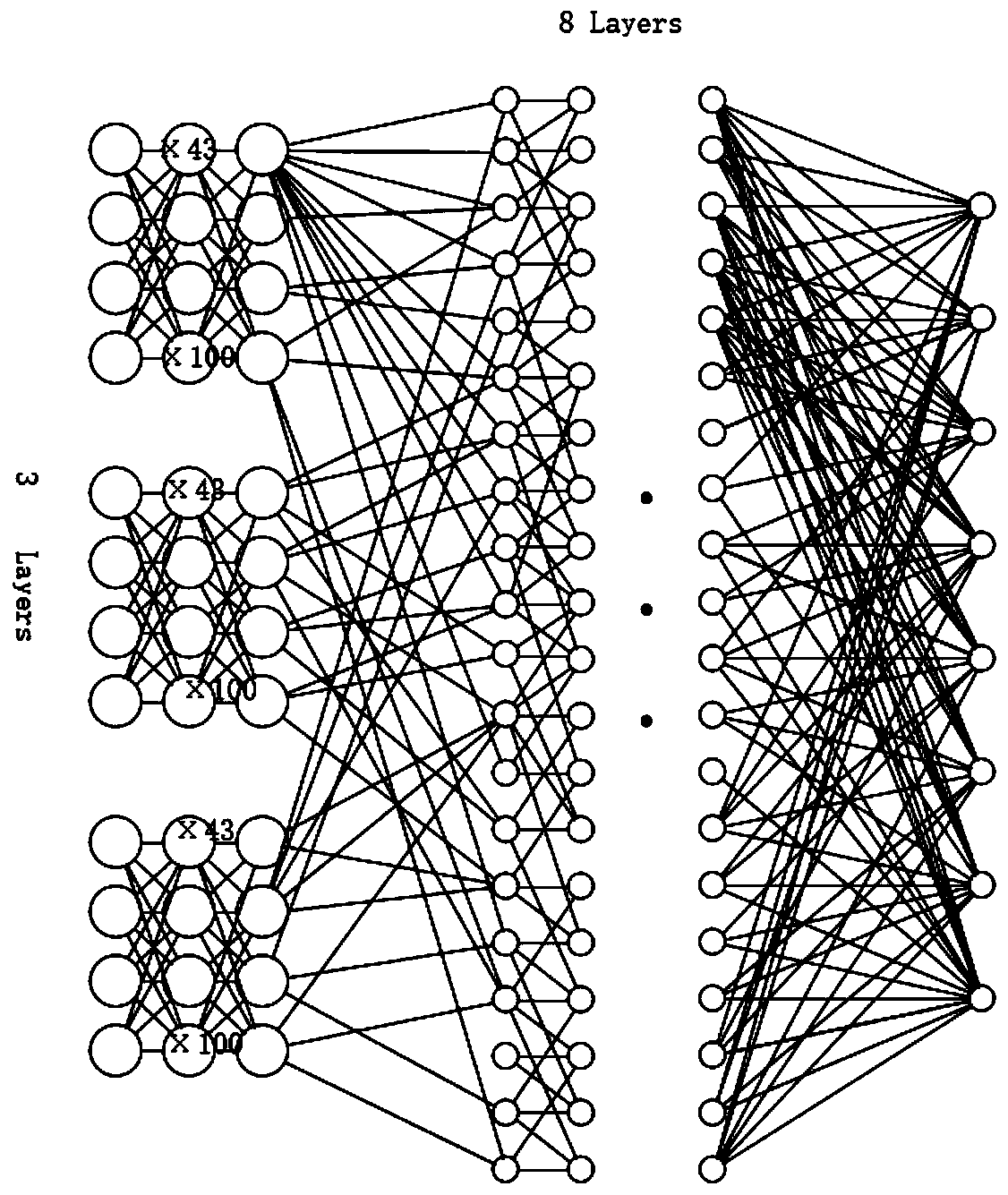

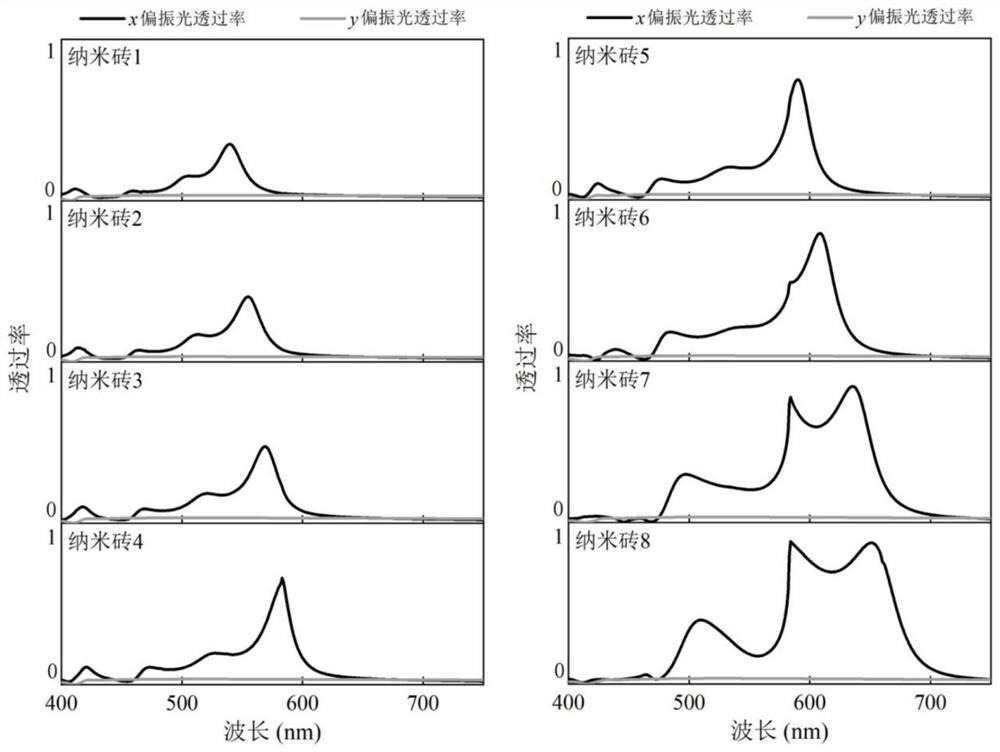

Nanostructure design method based on deep learning

The invention provides a nanostructure design method based on deep learning, and the method comprises the steps: building a training data set which comprises any kind of nanostructure information; preprocessing the training data set to transpose and normalize the data in the training data set; constructing a spectrum prediction network SPN and a geometrical shape prediction network GPN; integrating the spectrum prediction network SPN and the geometrical shape prediction network GPN into a neural network model, wherein the output of the spectrum prediction network SPN is connected with the input of the geometrical shape prediction network GPN; training the integrated neural network model by using the preprocessed training data set, and finishing the training of the neural network model whenthe loss function reaches a preset value; and inputting the frequency spectrums and the material properties in the X and Y polarization directions corresponding to the to-be-established nanostructureinto the trained neural network model to obtain eight nanostructure characterization points of the nanostructure, thereby obtaining the geometrical shape of the nanostructure.

Owner:CHINA UNIV OF GEOSCIENCES (WUHAN)

Design Tools For Converting a FinFet Circuit into a Circuit Including Nanowires and 2D Material Strips

InactiveUS20160335387A1Fine granularityImprove the level ofTransistorNanoinformaticsElectrical conductorNanowire

An integrated circuit design tool includes a cell library. An entry in the cell library comprises a specification of the cell including a first transistor and a second transistor. The first transistor can include a first set of nanowires or 2D material strips arranged in parallel to form a channel structure, and a gate conductor disposed across the first set of nanowires or 2D material strips. The second transistor can include a second set of nanowires or 2D material strips arranged in parallel to form a channel structure, and a gate conductor disposed across the first set of nanowires or 2D material strips. The number of nanowires or 2D material strips in the first set can be different from the number of nanowires or 2D material strips in the second set, so that the drive power of the individual transistors can be set with finer granularity.

Owner:SYNOPSYS INC

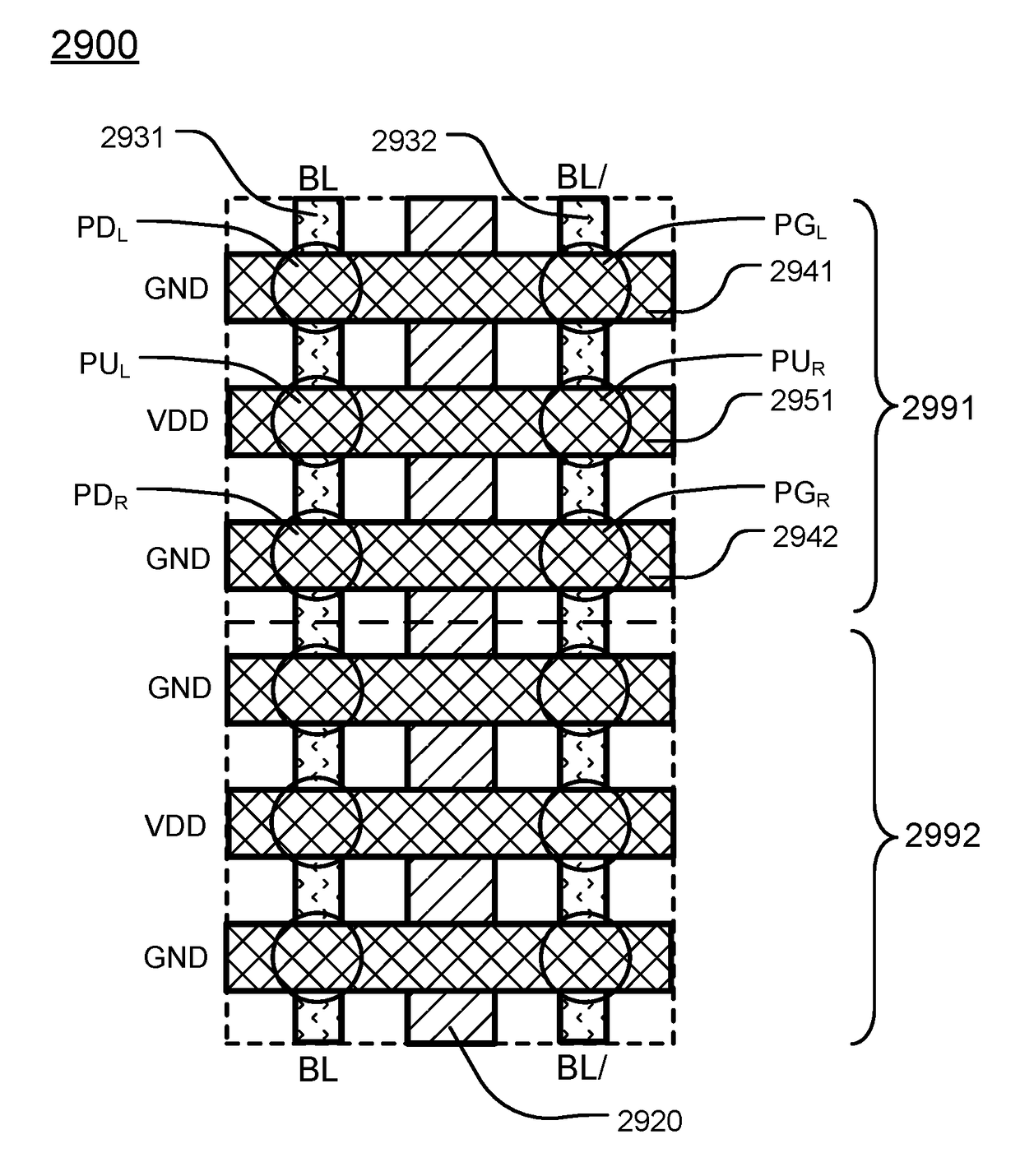

Memory cell including vertical transistors and horizontal nanowire bit lines

ActiveUS10037397B2Fine granularityImprove the level ofTransistorNanoinformaticsBit lineElectrical conductor

An integrated circuit design tool includes a cell library. An entry in the cell library comprises a specification of the cell including a first transistor and a second transistor. The first transistor can include a first set of nanowires or 2D material strips arranged in parallel to form a channel structure, and a gate conductor disposed across the first set of nanowires or 2D material strips. The second transistor can include a second set of nanowires or 2D material strips arranged in parallel to form a channel structure, and a gate conductor disposed across the first set of nanowires or 2D material strips. The number of nanowires or 2D material strips in the first set can be different from the number of nanowires or 2D material strips in the second set, so that the drive power of the individual transistors can be set with finer granularity.

Owner:SYNOPSYS INC

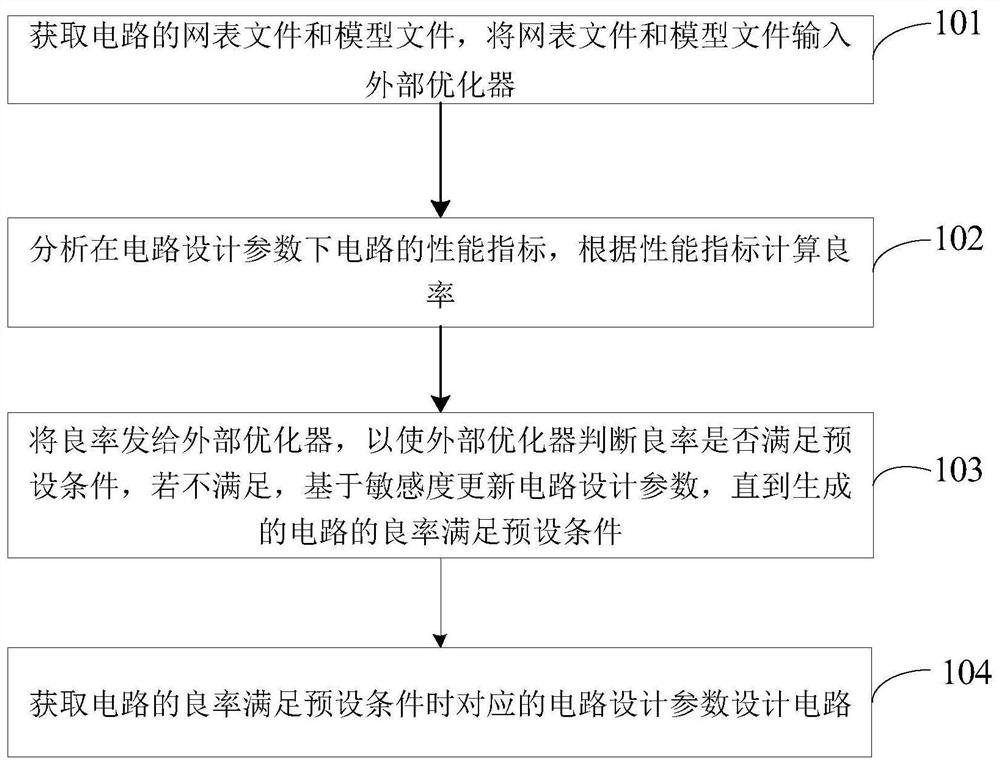

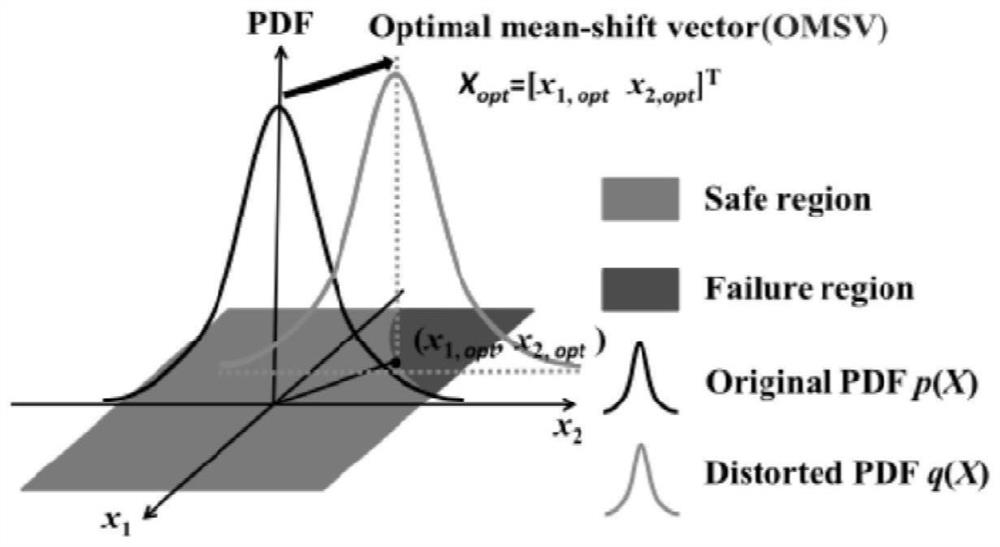

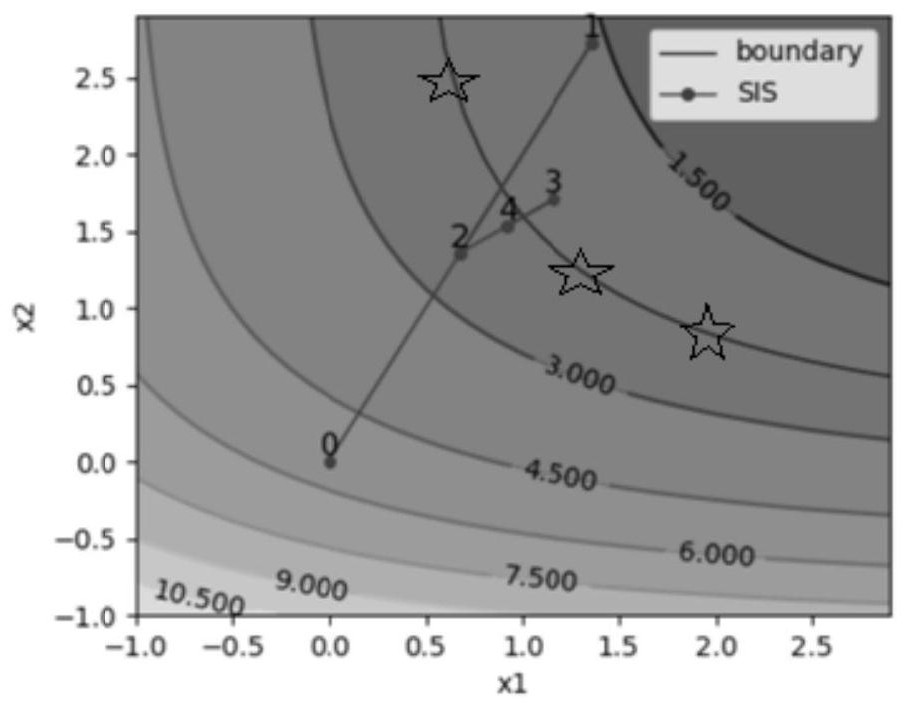

Full-sensitivity confrontation importance sampling yield optimization method and device

ActiveCN112861459ASampling avoidanceSampling EliminationCharacter and pattern recognitionDesign optimisation/simulationMean-shiftHemt circuits

The invention provides a full-sensitivity confrontation importance sampling yield optimization method and device, and relates to the technical field of data processing, and the method comprises the steps: obtaining a netlist file and a model file of a circuit, and inputting the netlist file and the model file into an external optimizer; analyzing performance indexes of the circuit under the circuit design parameters, and calculating the yield according to the performance indexes; sending the yield to the external optimizer, so that the external optimizer judges whether the yield meets a preset condition or not, and if not, circuit design parameters are updated based on the sensitivity until the yield of the generated circuit meets the preset condition; and obtaining corresponding circuit design parameters when the yield of the circuit meets a preset condition to design the circuit. Thus, sampling in an external optimization process is avoided based on the sensitivity. Meanwhile, the invention provides a yield analysis method for rapid sensitivity importance sampling so as to eliminate searching of an optimal mean shift vector in importance sampling and sampling in subsequent sampling.

Owner:TSINGHUA UNIV

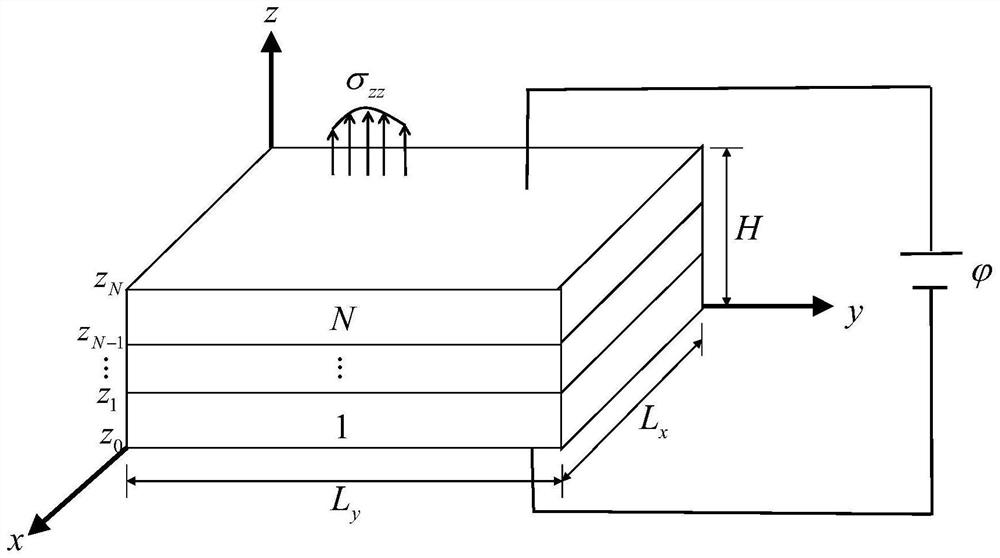

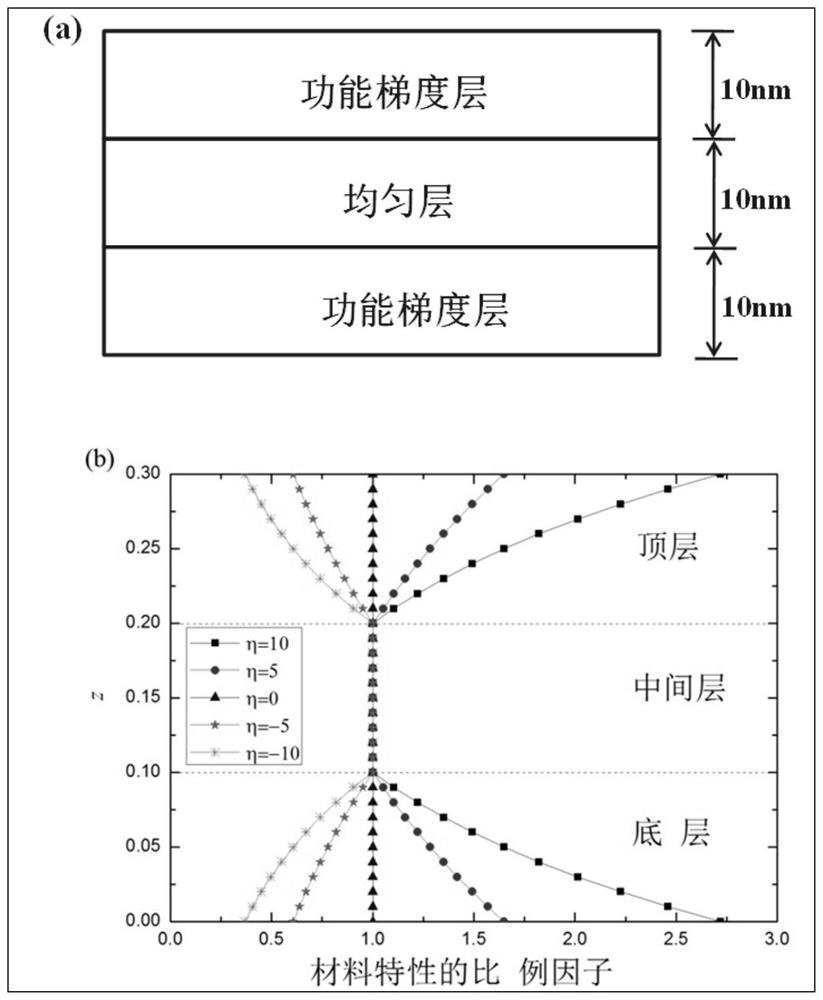

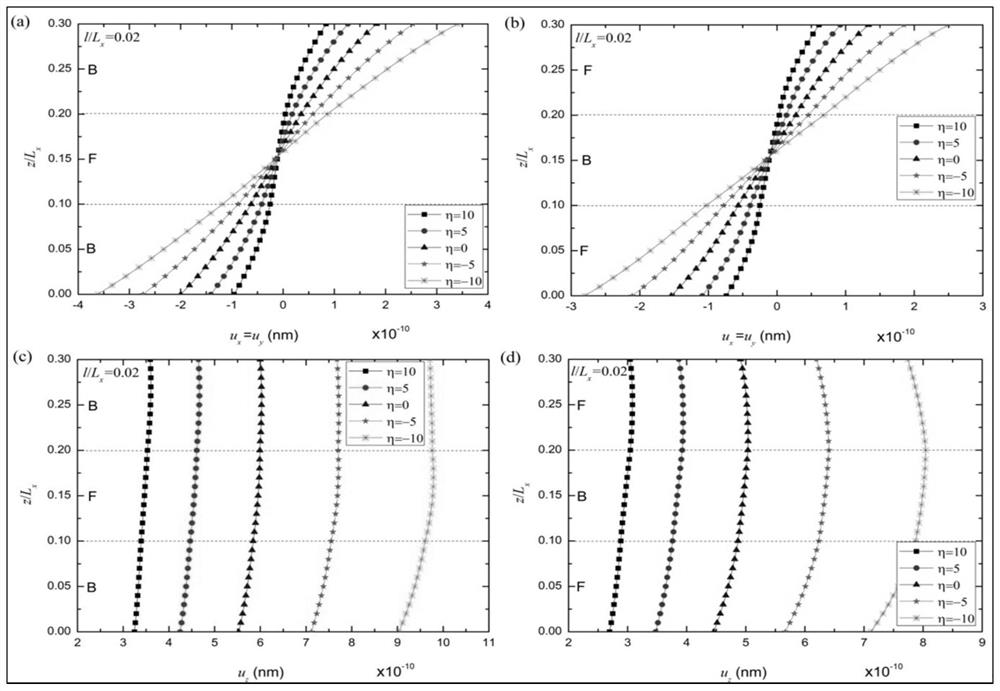

Method and device for analyzing bending deformation of functionally gradient multilayer magnetoelectric elastic nano-plate

ActiveCN111783319ASolve the technical problem of low accuracy in analysisReveal small-scale mechanical behaviorDesign optimisation/simulationSpecial data processing applicationsEngineeringMechanical engineering

The invention discloses a method and device for analyzing bending deformation of a functionally gradient multilayer magnetoelectric elastic nano-plate. The method comprises the following steps: establishing a three-dimensional coordinate system; establishing a coupling constitutive relation formula, an expansion strain-displacement relation formula and a balance equation; calculating an extended displacement vector of a functionally graded magnetic-electric-elastic nano-plate under a simply supported boundary condition, sequentially substituting the extended displacement vector into the expansion strain-displacement relation formula, the coupling constitutive relation formula and the balance equation to obtain a linear intrinsic equation set, and finally determining a general solution formula to calculate a general solution; determining a general solution expression, then applying a force load and an electric load to the top surface, then calculating an expansion displacement vector and a stress vector at any depth of each layer, and finally, calculating all quantities and corresponding in-plane components. The method is helpful for revealing small-scale mechanical behaviors, and provides a theoretical basis for the design and application of the functionally graded magnetoelectric elastic nano-multilayer board and the miniaturized design and manufacturing of an engineering intelligent structure.

Owner:INNER MONGOLIA UNIV OF TECH

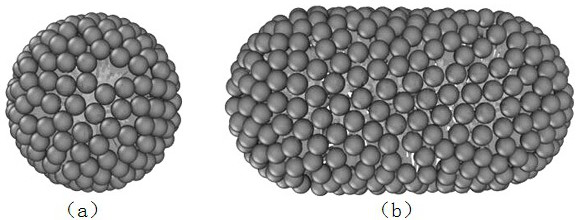

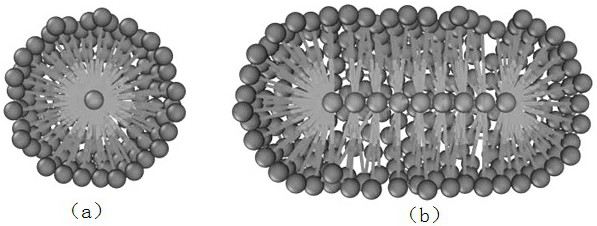

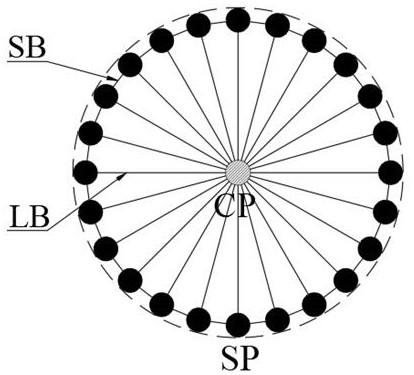

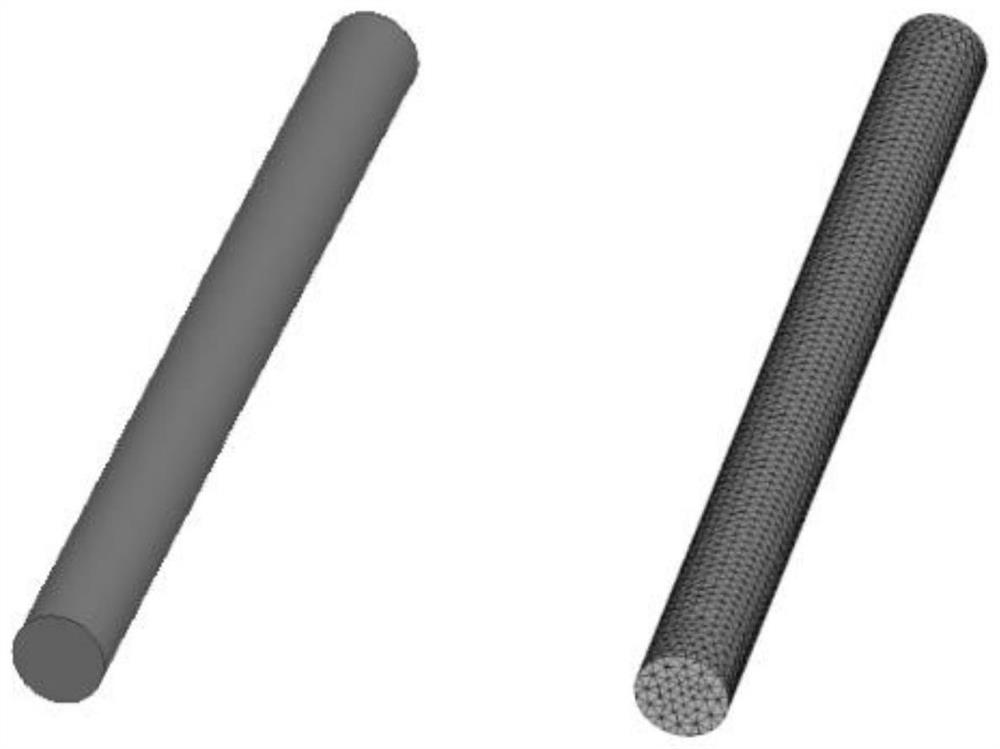

General force field rodlike nanoparticle coarse graining model and establishment method thereof

PendingCN114566225AKinetic performance unchangedControl lengthDesign optimisation/simulationComputational theoretical chemistryNanoparticleNanochemistry

The invention provides a general force field rodlike nanoparticle coarse graining model and an establishment method thereof, and belongs to the technical field of nanometer chemical calculation. The model is divided into a central bead cluster and outer-layer cylindrical shell-shaped beads, the outermost-layer beads arranged at the two ends are hemispherical spherical shells, and the outermost-layer beads arranged at the middle section are cylindrical shell-shaped beads; two types of beads are defined in a used force field, the molar mass and potential action parameters are assigned, and a central bead cluster and the outermost beads are connected through keys, so that it is guaranteed that deformation and collapse do not occur during molecular dynamics simulation, and the overall property is kept unchanged; the whole coarse graining model only has the outermost layer of beads and the central bead cluster, so that the number of the beads is greatly reduced, the accuracy of molecular dynamics calculation can be ensured, meanwhile, the calculation amount is greatly reduced, the calculation speed is increased, and the waste of calculation power is avoided.

Owner:TAIYUAN UNIV OF TECH

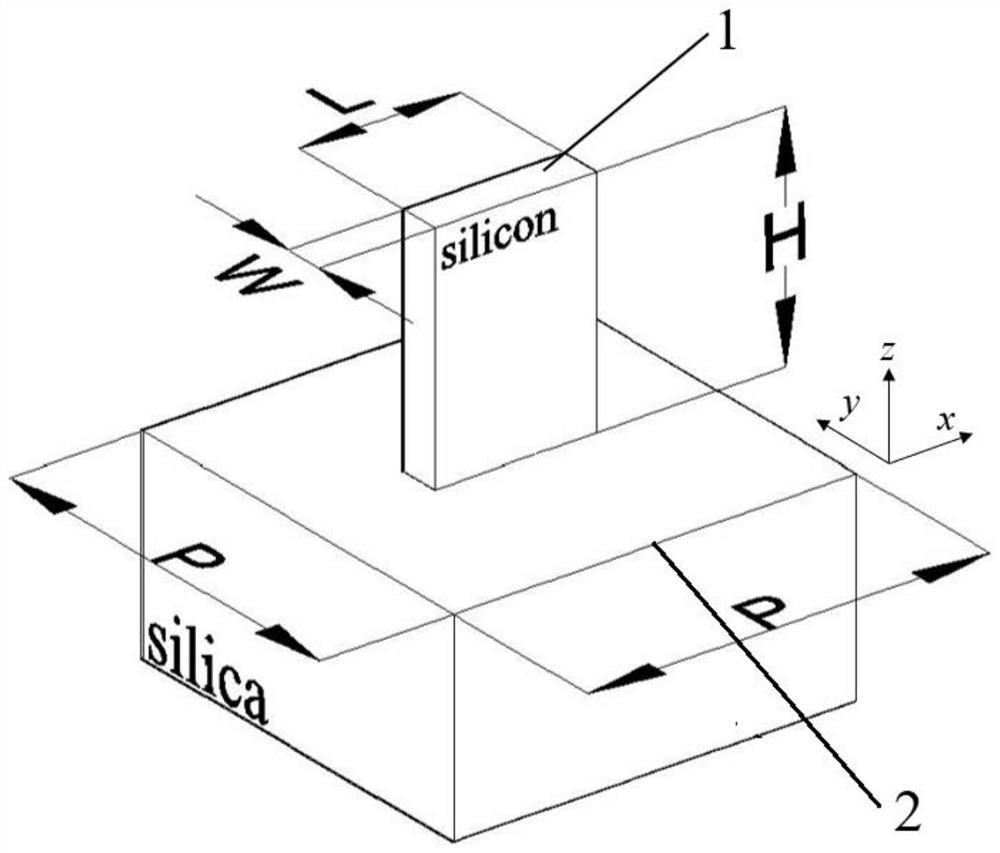

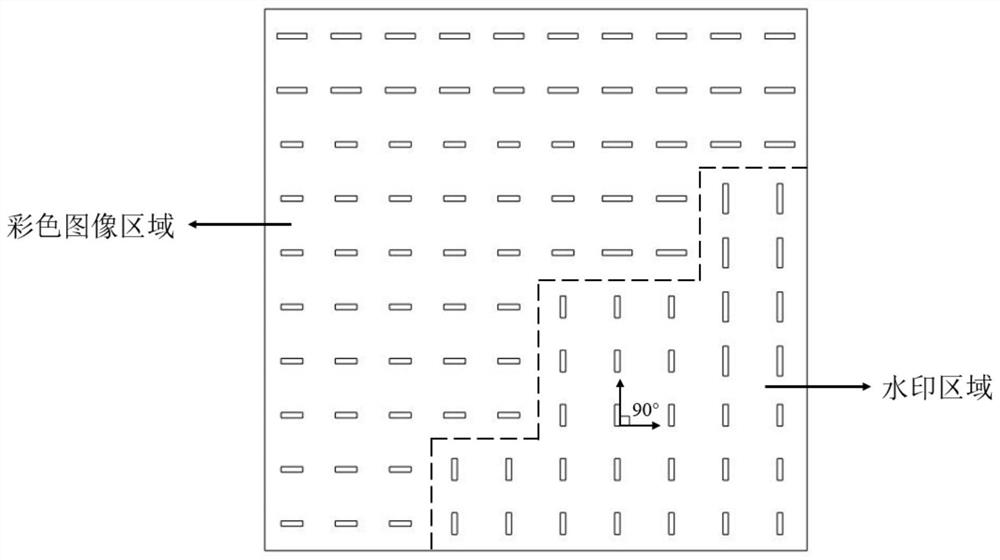

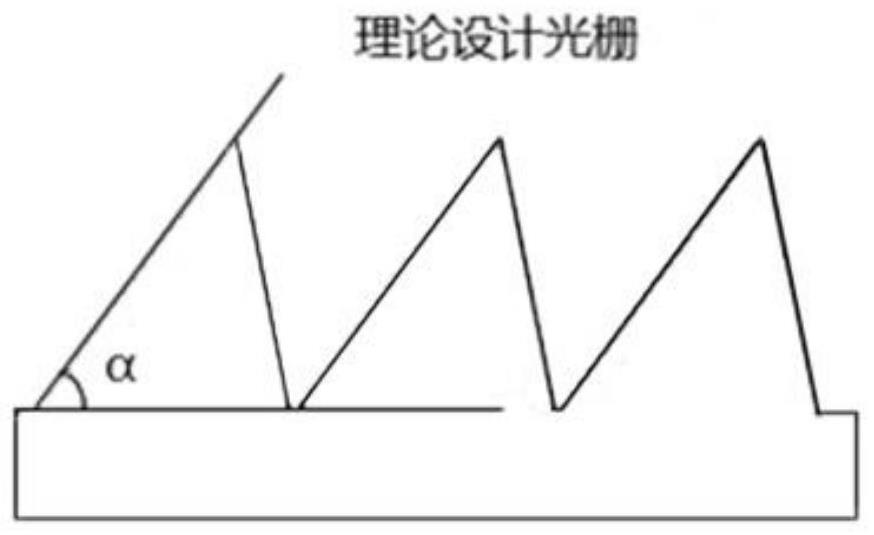

Design method of super-surface color nanometer printing device capable of reconstructing watermarks

ActiveCN112733343AReduce design difficultyReduce processing difficultyGeometric CADDesign optimisation/simulationColor imageComputer graphics (images)

The invention provides a design method of a super-surface color nano printing device for realizing reconfigurable watermarks. The design method comprises the following steps: constructing a super-surface array; optimizing and simulating to obtain reflection spectrums of the nano-brick structural units with multiple groups of size parameters, and calculating to obtain structural colors of the nano-brick structural units; designing a target color image, and selecting several groups of size parameters with structure colors meeting requirements as alternative size parameters according to color distribution of the target color image; finding size parameters corresponding to the nano-brick structure units corresponding to the pixel points from the alternative size parameters according to the colors of the pixel points of the target color image; and designing a watermark image to be superposed, setting the nano-brick steering angle of the nano-brick structure unit corresponding to the pixel points without watermark superposition as alpha on the basis of the steps, and setting the nano-brick steering angle of the nano-brick structure unit corresponding to the pixel points with watermark superposition as alpha + / -90 degrees. The machining error tolerance is high, the design and machining difficulty is reduced, and the good development prospect is achieved.

Owner:WUHAN UNIV

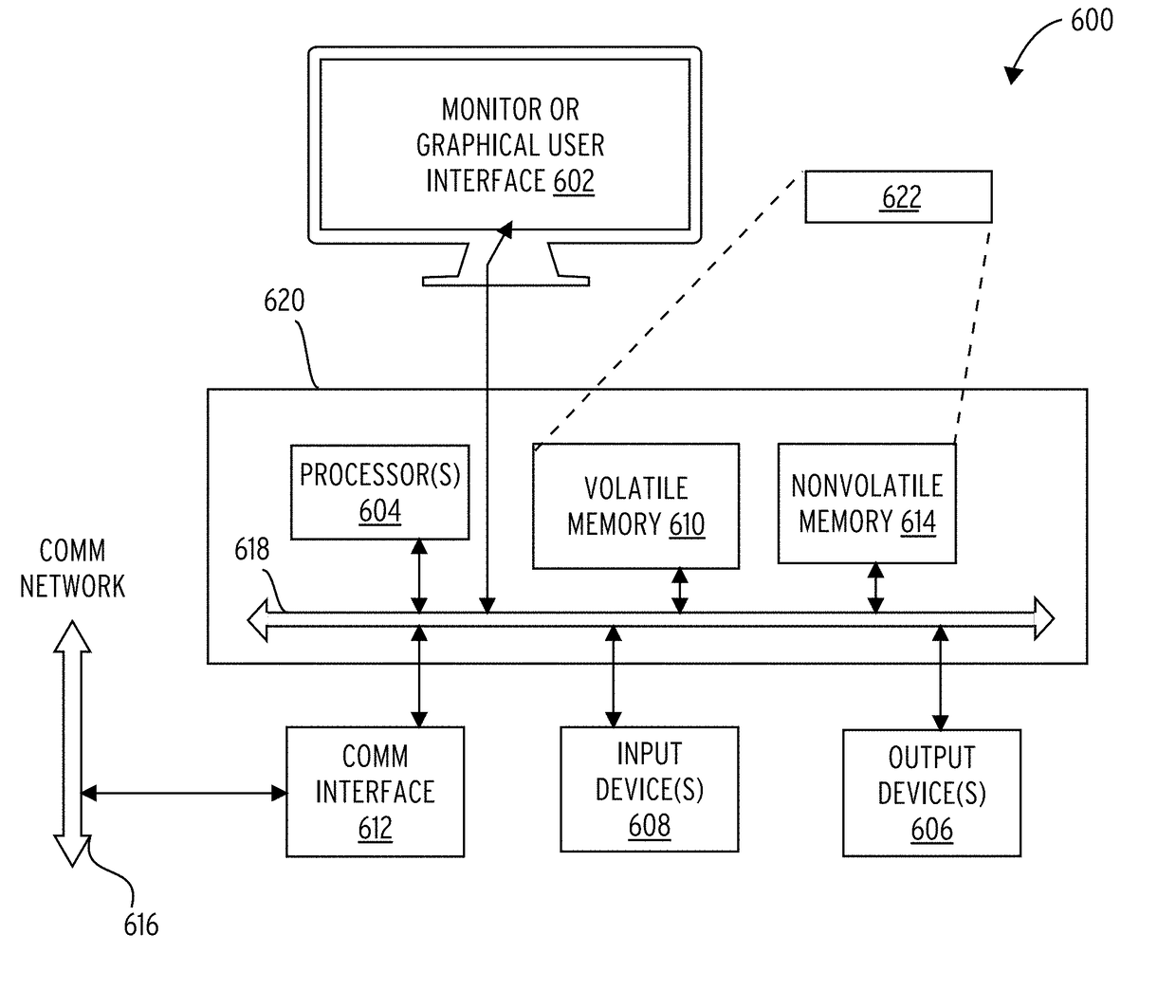

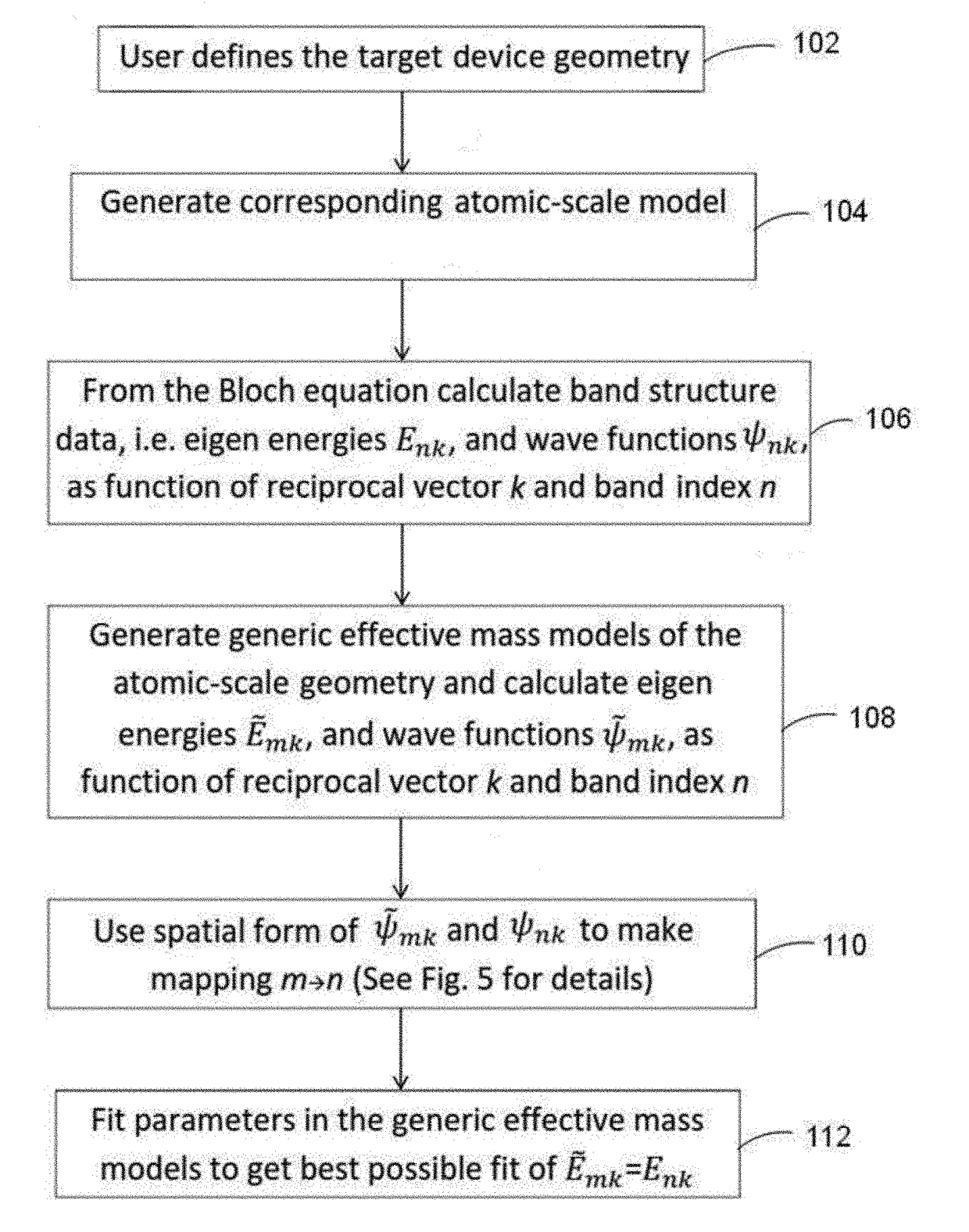

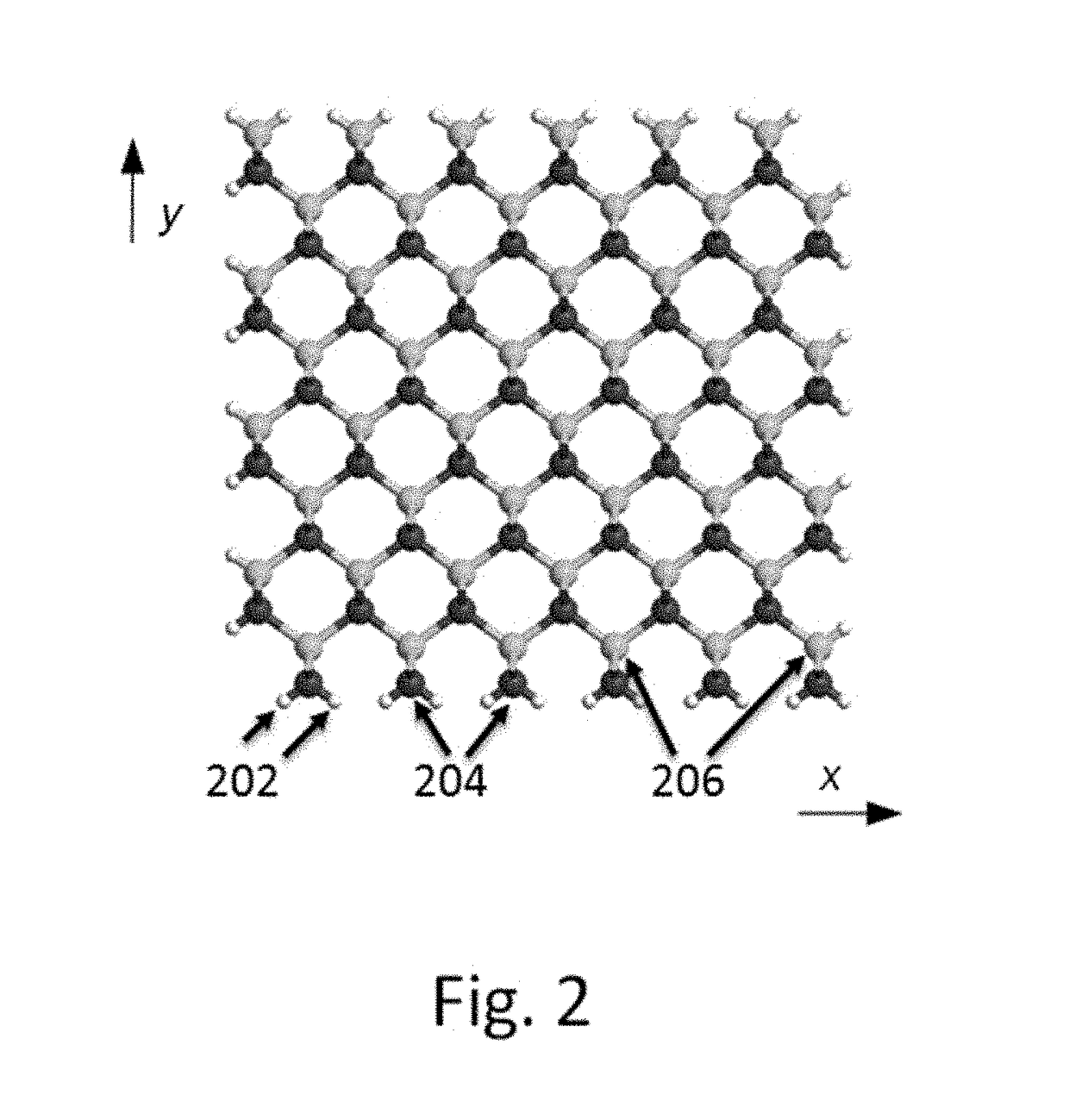

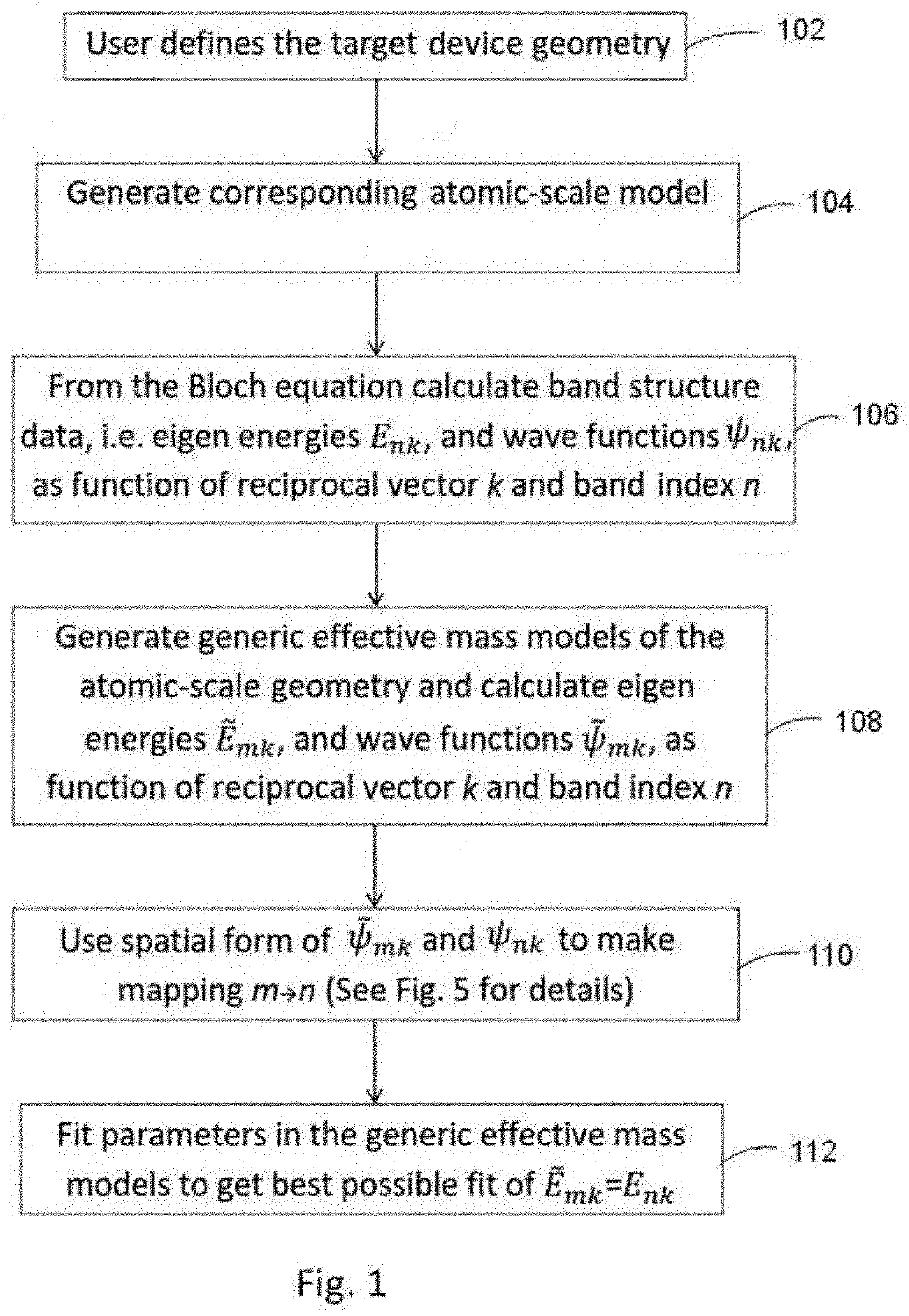

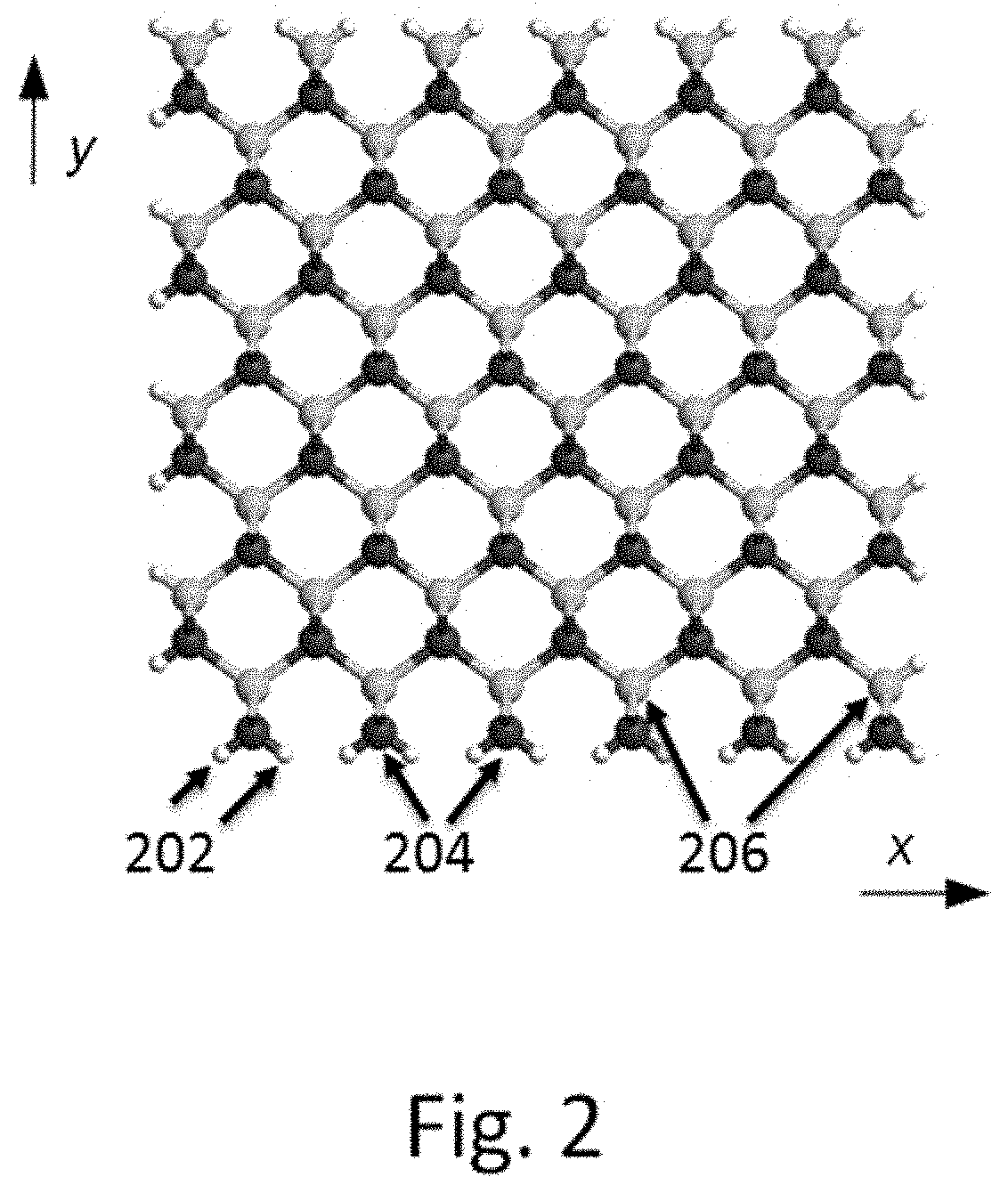

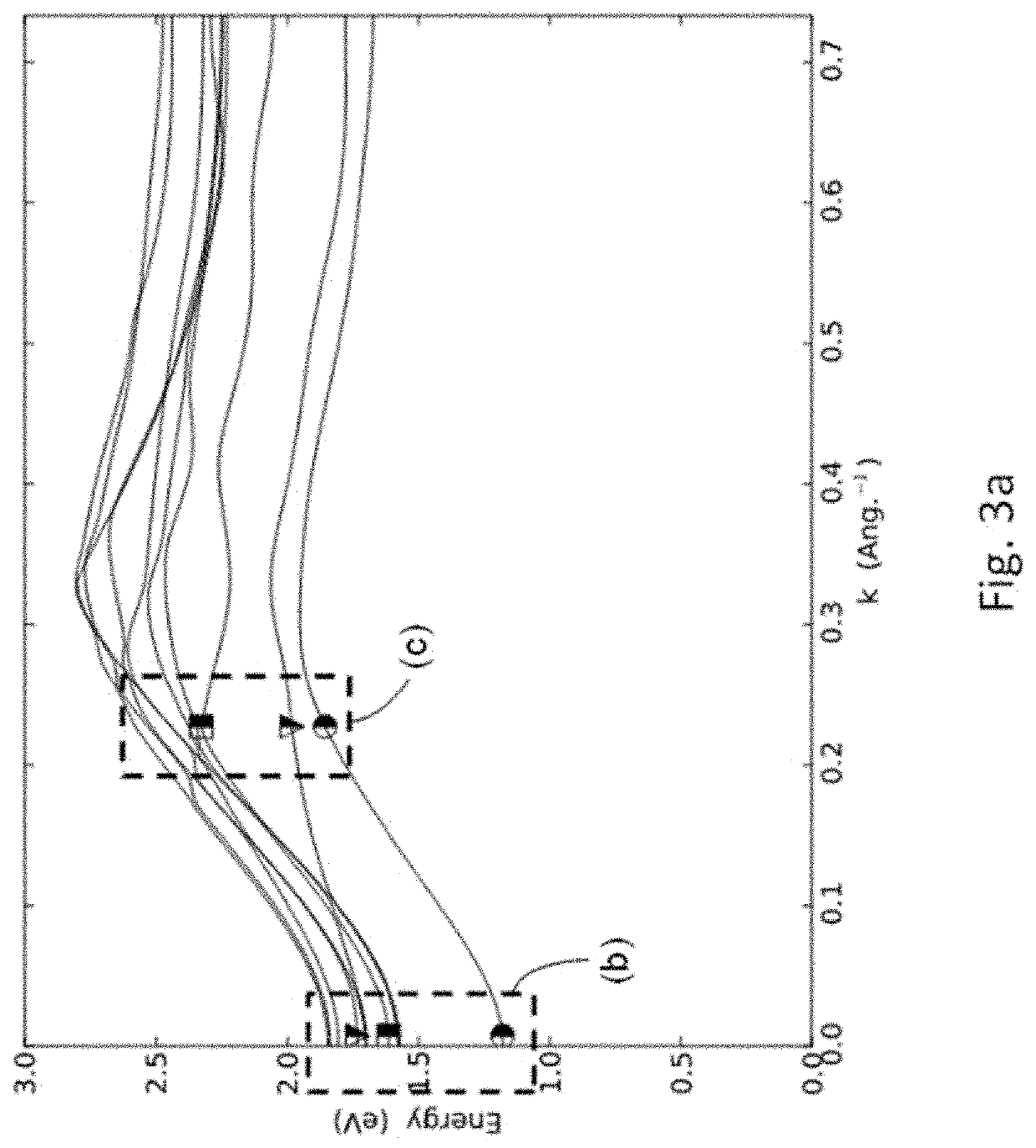

Systems and Methods for Providing Approximate Electronic-Structure Models from Calculated Band Structure Data

ActiveUS20180129765A1Precise structureAccurate descriptionConfiguration CADDesign optimisation/simulationScale modelCharacteristic energy

Computer-aided methods for simulating confined nanodevices are disclosed. In example implementations, atomic-scale model of the nanodevices are generated so that dimensions and materials are specified. Then, band structures which comprise wave functions and Eigen energies are calculated using First Principles Methods (FPM). Effective mass modeled which comprise wave functions and Eigen energies are generated. After that, spatial wave functions of the calculated FPM band structures are mapped to the generated effective mass band structures wave functions by considering global behavior. In response to the mapping, generated effective mass models are fitted to calculated FPM energies so that approximate electronic band structures of the confined nanodevices are modeled. Computer programs for carrying out the methods, data media and computer systems are also disclosed.

Owner:SYNOPSYS INC

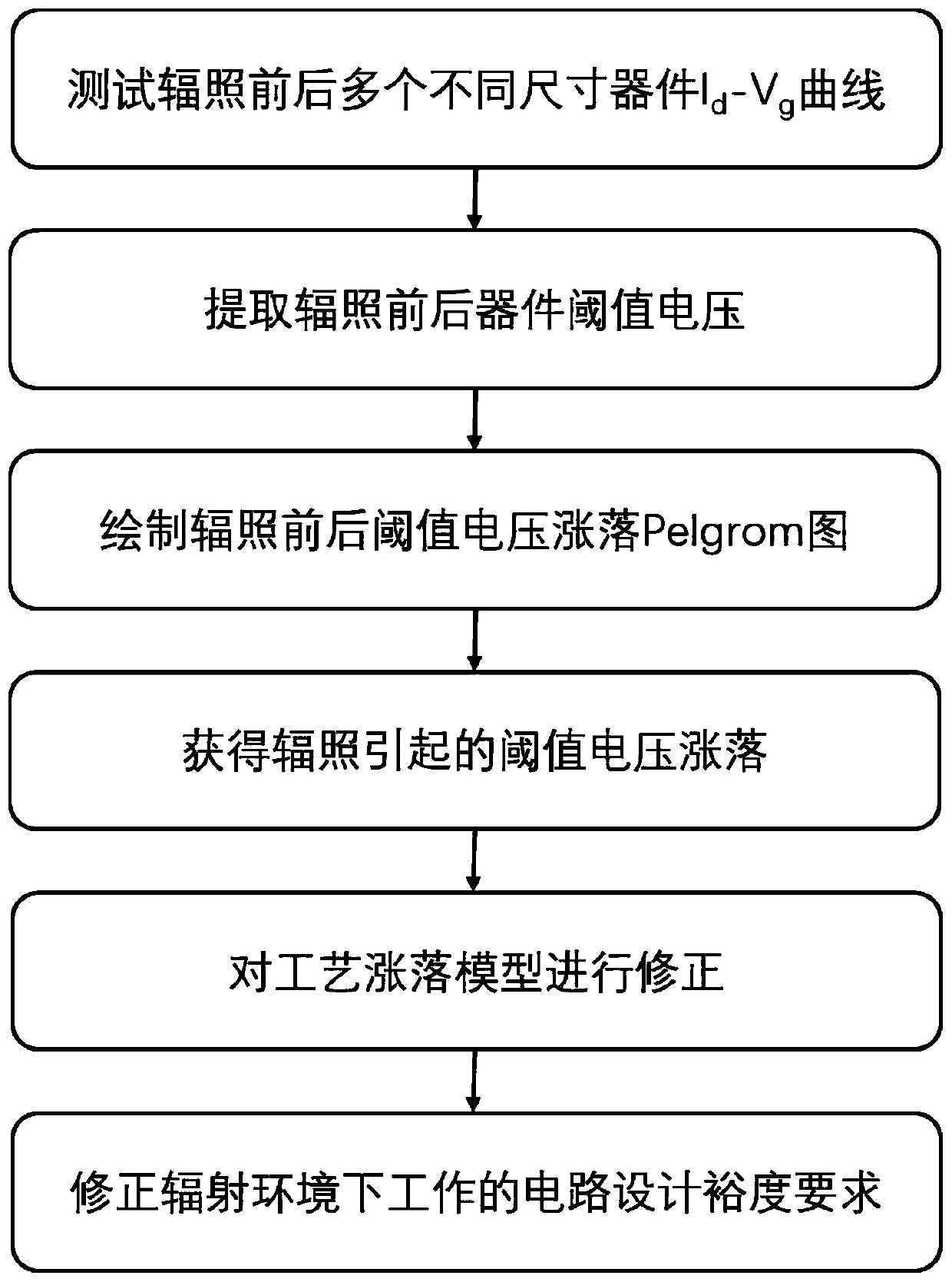

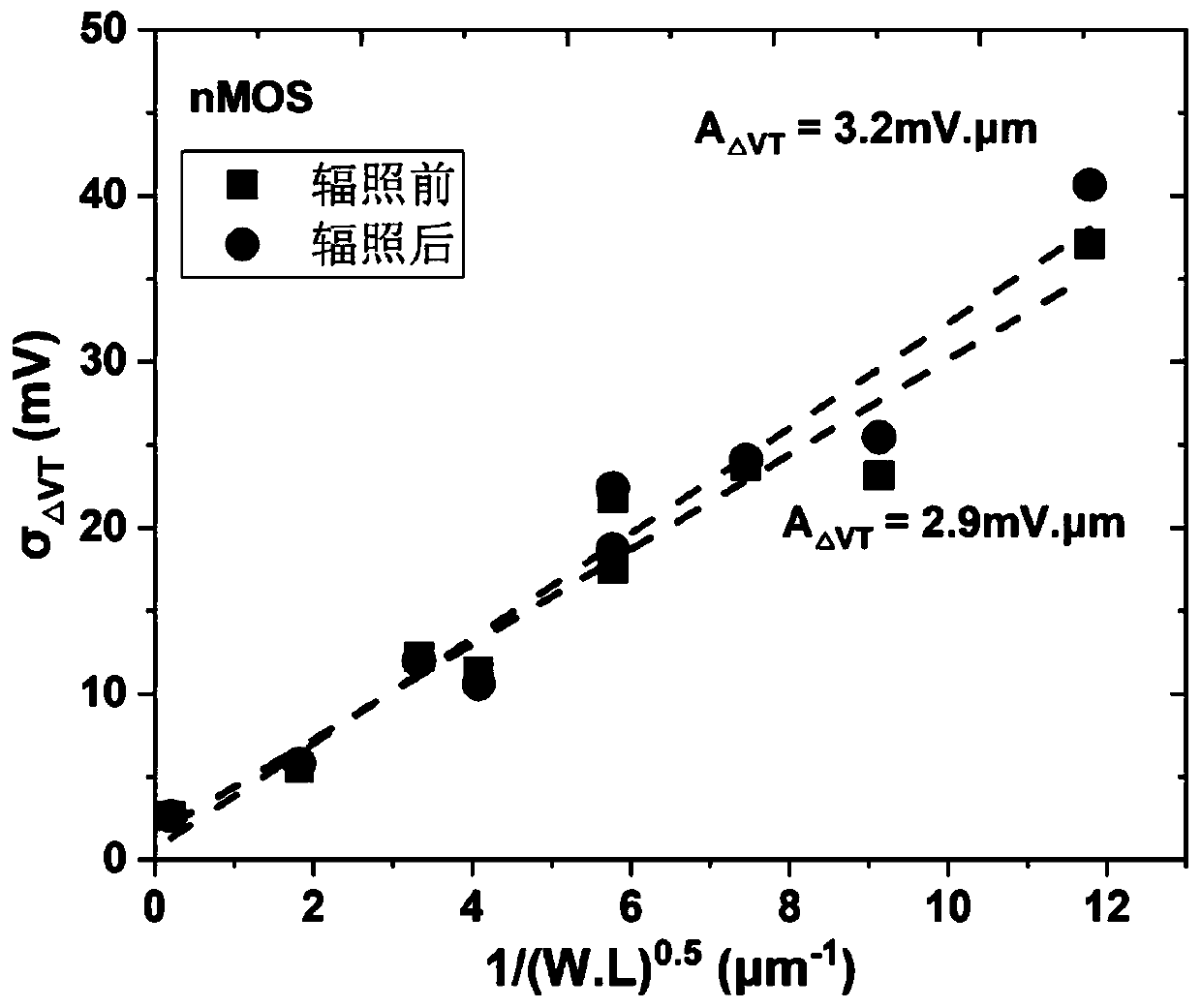

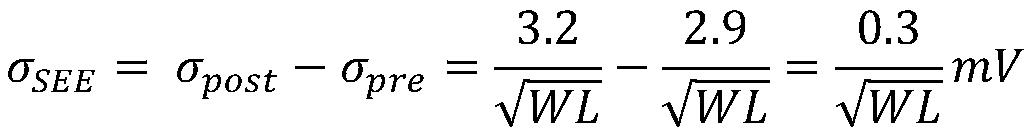

Characterization method and application of fluctuation introduced by single-particle irradiation

ActiveCN110929468AModified Design Margin RequirementsImprove reliabilitySemiconductor operation lifetime testingDesign optimisation/simulationNuclear engineeringPhysical chemistry

The invention discloses a characterization method and application of fluctuation introduced by single-particle irradiation. Threshold voltage distribution of a plurality of devices with different sizes before and after single-particle irradiation is tested and extracted to acquire threshold voltage fluctuation caused by single-particle irradiation. Then a process fluctuation model is corrected, and the circuit design margin requirement of work in the radiation environment is corrected. A calculation method is simple, an application range is wide, the application requirements of different technical generations and different radiation environments can be met, the circuit design margin requirement of working in the radiation environment is corrected, and the working reliability of the nanoscale integrated circuit in the radiation environment is improved.

Owner:PEKING UNIV

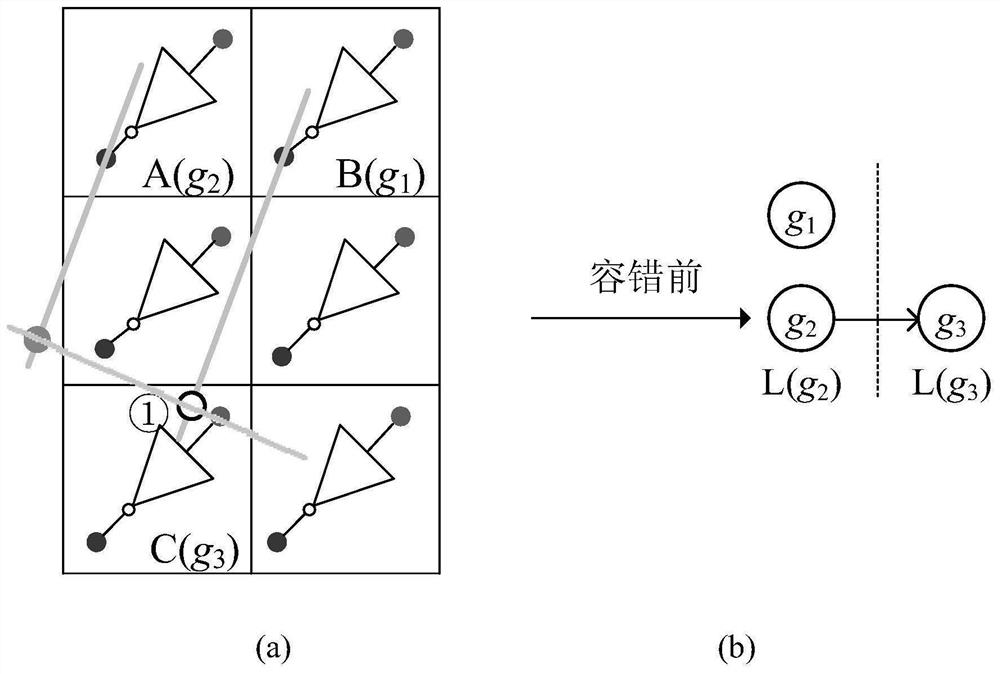

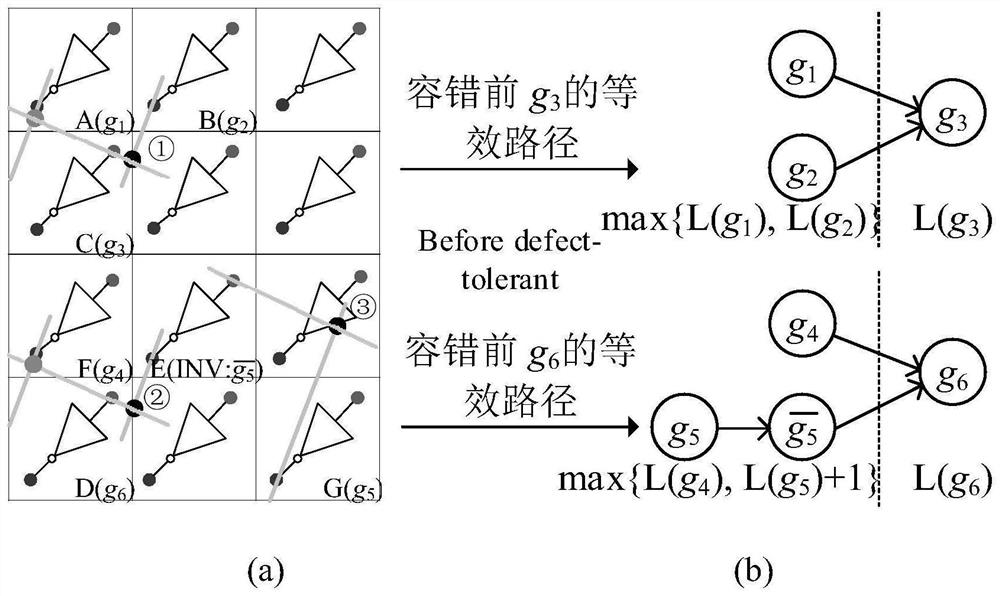

Nano CMOS circuit fault-tolerant mapping method capable of optimizing time delay

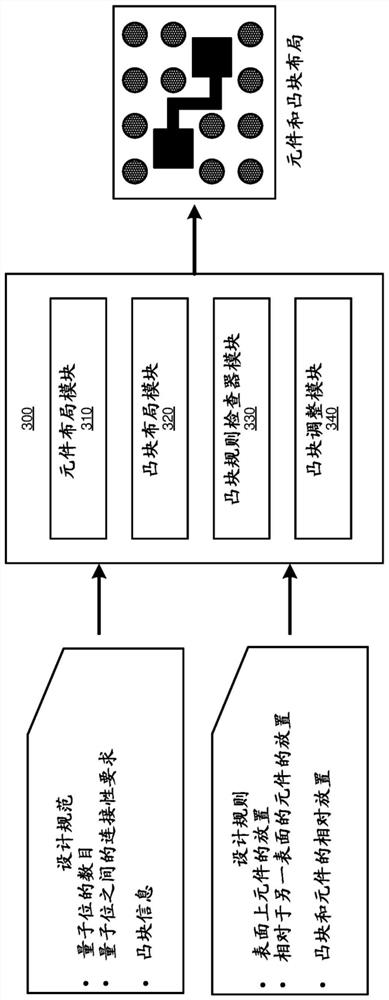

PendingCN112214946AImprove mapping abilityBig spaceSpecial data processing applicationsCAD with nanotechnologyTime delaysHemt circuits

The invention discloses a nano CMOS (Complementary Metal Oxide Semiconductor) circuit fault-tolerant mapping method capable of optimizing time delay, and aims to solve the problems of poor time delayperformance, poor solving speed, poor quality and the like in a nano CMOS circuit for realizing a correct logic function by adopting an existing fault-tolerant mapping method. Under the mapping constraints of defective nano CMOS circuit, the invention provides a nano CMOS circuit fault-tolerant mapping method capable of optimizing time delay. According to the fault-tolerant mapping method, the mapping process of a traditional nano CMOS circuit is optimized, the dividing technology of a logic level to a logic circuit to be mapped and the physical-level pre-planning technology with original input as an object are newly added, and the logic circuit is mapped by taking a path tree as a unit. Two mapping modes are adopted to be mapped into a pre-planned area in the nano CMOS circuit to optimizeeach path delay, the mapping success rate is improved by searching available defect units, and the delay performance of the delay mapping circuit is optimized on the basis of quickly eliminating theinfluence of defects on the logic function of the nano CMOS circuit.

Owner:NINGBO UNIV

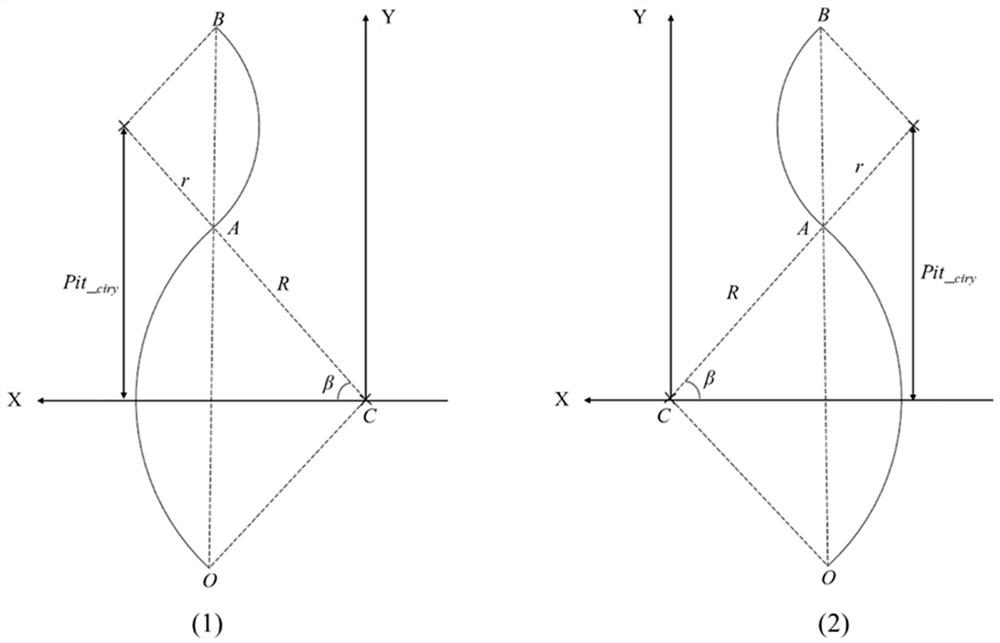

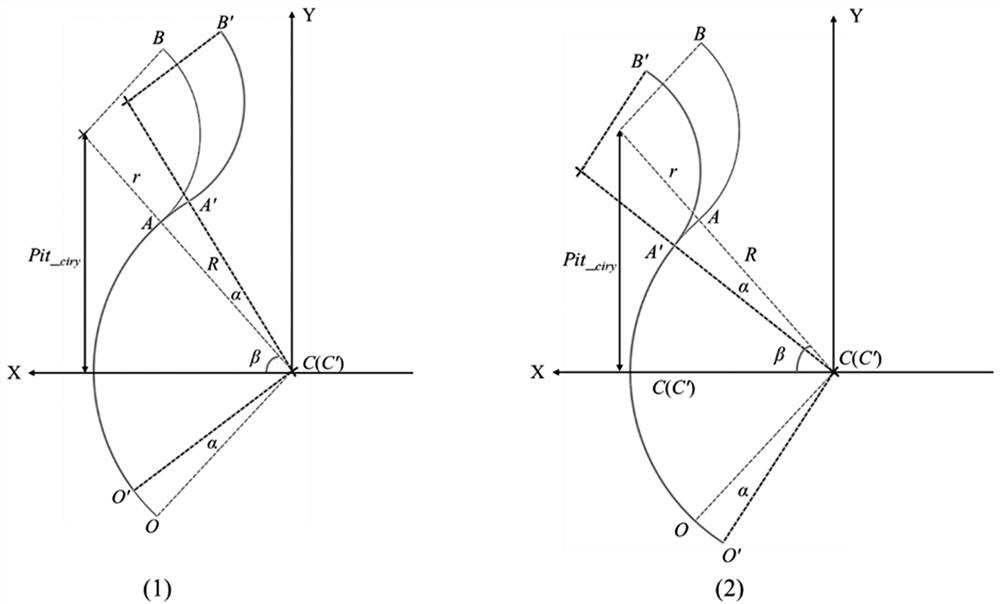

Parameterization rapid modeling method for profile radiator with taper corrugated fins

PendingCN114491833AImprove modeling efficiencyImprove Simulation EfficiencyGeometric CADDesign optimisation/simulationEngineeringDimensional modeling

The invention relates to a modeling scheme of a profile radiator, in particular to a parameterization rapid modeling method for a profile radiator with taper corrugated fins. Aiming at modeling of air-cooled fin radiators in medium and high power converter application occasions, particularly simulation modeling of tapered corrugated fin section bar radiators, a parameterized mathematical modeling method is adopted, and corrugated fin units with different radiuses and different sizes, fins with different tapers, different fin numbers and different substrate thicknesses are realized; according to the rapid modeling function of edge rib radiators with different fin offset distances and different sizes and shapes, a three-dimensional model can be automatically generated by software only by inputting key technical parameters, and the three-dimensional modeling and simulation efficiency is improved. The heat dissipation performance comparative analysis of the fin units in different shapes is facilitated, and the optimal structure scheme is determined.

Owner:CRRC YONGJI ELECTRIC CO LTD

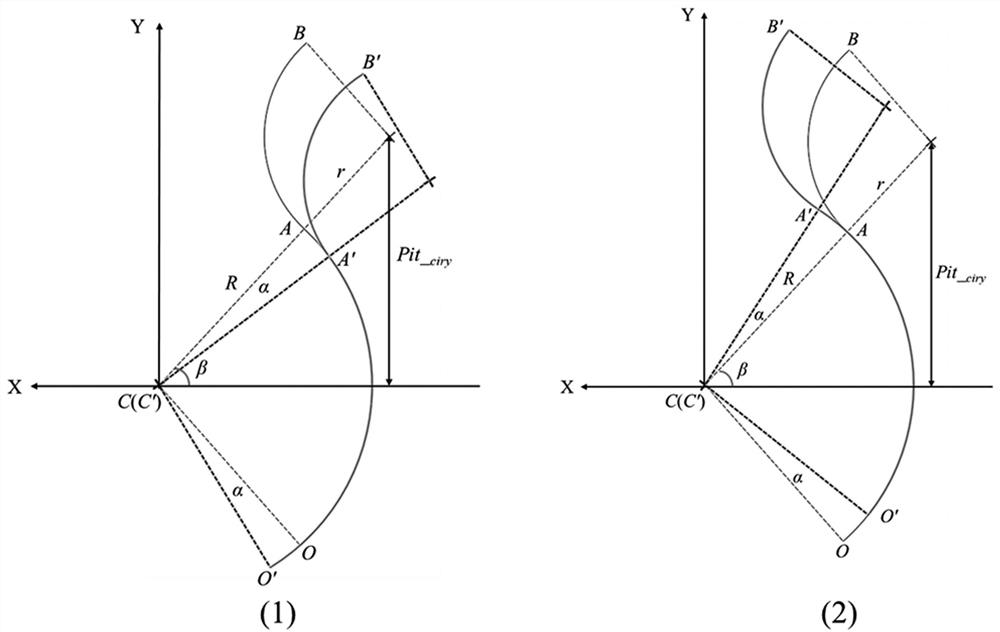

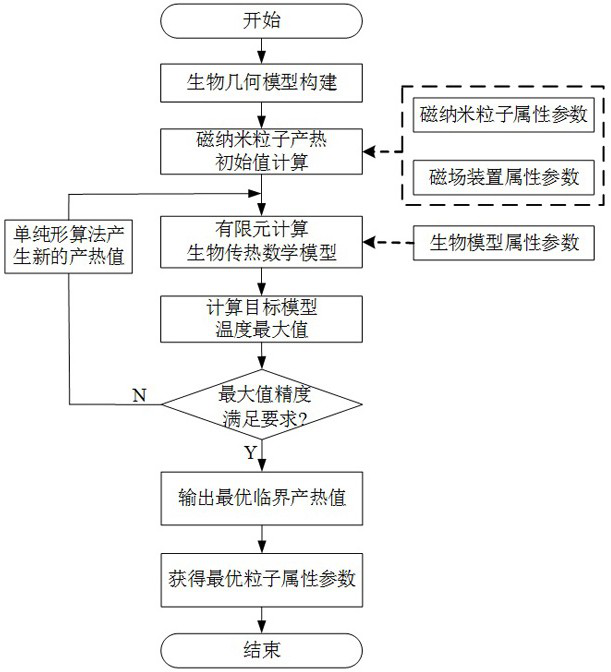

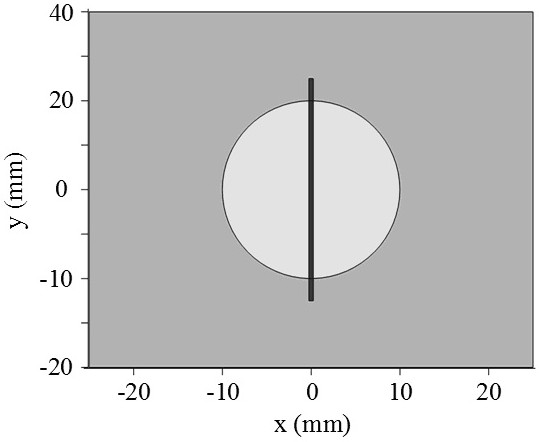

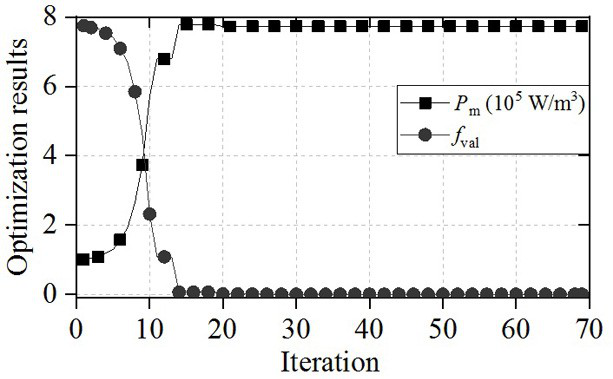

Automatic positioning method for critical heat production value of magnetic nanoparticles based on simplex algorithm

ActiveCN111680444AEffectively locate the critical calorific valueOptimizing Effective PropertiesDesign optimisation/simulationSpecial data processing applicationsMathematical modelMagnetite Nanoparticles

The invention relates to an automatic positioning method for a critical heat production value of magnetic nanoparticles based on a simplex algorithm. After a simplex algorithm and a magnetic nanoparticle critical heat production technology are introduced, a finite element method is applied to solve the biological heat transfer mathematical model based on magnetic nanoparticle heat production, andthe magnetic nanoparticle critical heat production value is automatically positioned through algorithm optimization; on the basis, the application of the improved magnetic nanoparticle heat productiontheory effectively improves the prediction precision of the temperature distribution of the target geometric model. According to the invention, the optimal particle attribute of the magnetic nanoparticles during the magnetic hyperthermia period can be finally optimized so as to be applied to the magnetic nanometer hyperthermia instrument, and the magnetic hyperthermia effect of the magnetic nanometer hyperthermia instrument is improved.

Owner:FUZHOU UNIV

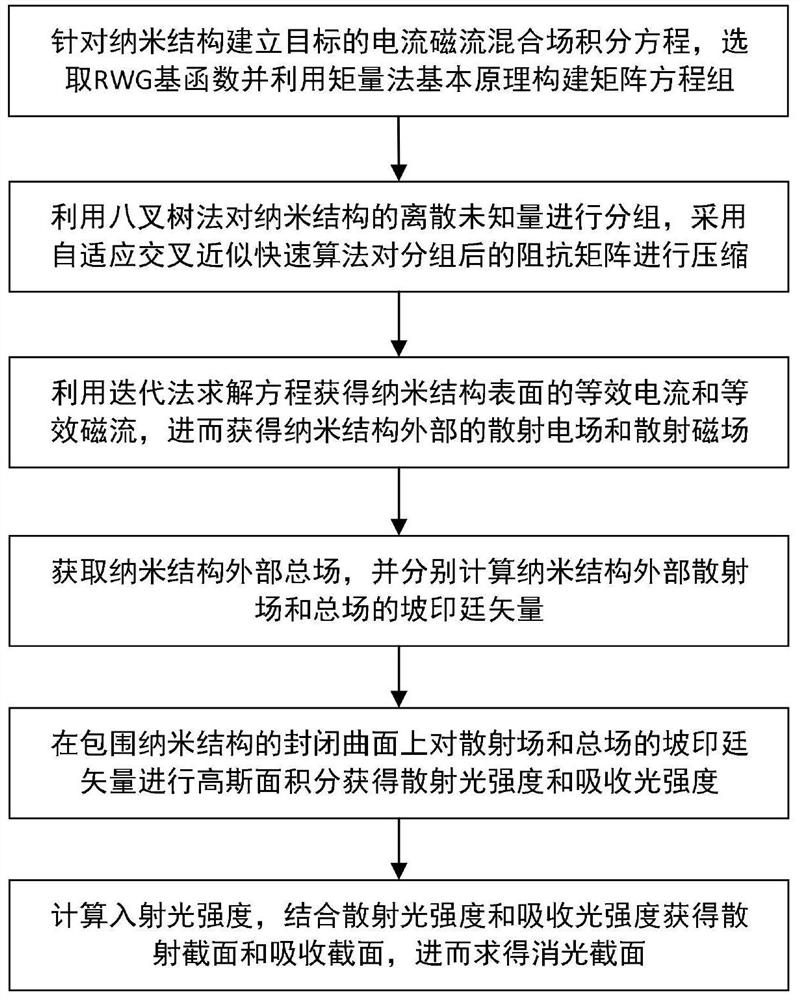

Nanostructure extinction characteristic simulation method based on moment method in combination with adaptive cross approximation fast algorithm

InactiveCN112711856AHigh precisionLittle unknownDesign optimisation/simulationCAD numerical modellingNumerical methodologyFast algorithm

The invention discloses a nanostructure extinction characteristic simulation method based on a moment method in combination with an adaptive cross approximation fast algorithm. According to the method, a moment method in an integral equation method is adopted for solving, and compared with a traditional numerical method such as a finite element method based on a differential equation method, dispersion errors do not exist, and the accuracy is high. According to the method, the extinction characteristic of the large-scale nanostructure can be solved by combining the adaptive cross approximation fast algorithm on the basis of the moment method, transplantation can be conveniently carried out under different background media, and the application range is wide.

Owner:NANJING UNIV OF POSTS & TELECOMM

Systems and methods for providing approximate electronic-structure models from calculated band structure data

ActiveUS11023639B2Precise structureAccurate descriptionCAD circuit designSpecial data processing applicationsElectronic structureResponse generation

Computer-aided methods for simulating confined nanodevices are disclosed. In example implementations, atomic-scale model of the nanodevices are generated so that dimensions and materials are specified. Then, band structures which comprise wave functions and Eigen energies are calculated using First Principles Methods (FPM). Effective mass modeled which comprise wave functions and Eigen energies are generated. After that, spatial wave functions of the calculated FPM band structures are mapped to the generated effective mass band structures wave functions by considering global behavior. In response to the mapping, generated effective mass models are fitted to calculated FPM energies so that approximate electronic band structures of the confined nanodevices are modeled. Computer programs for carrying out the methods, data media and computer systems are also disclosed.

Owner:SYNOPSYS INC

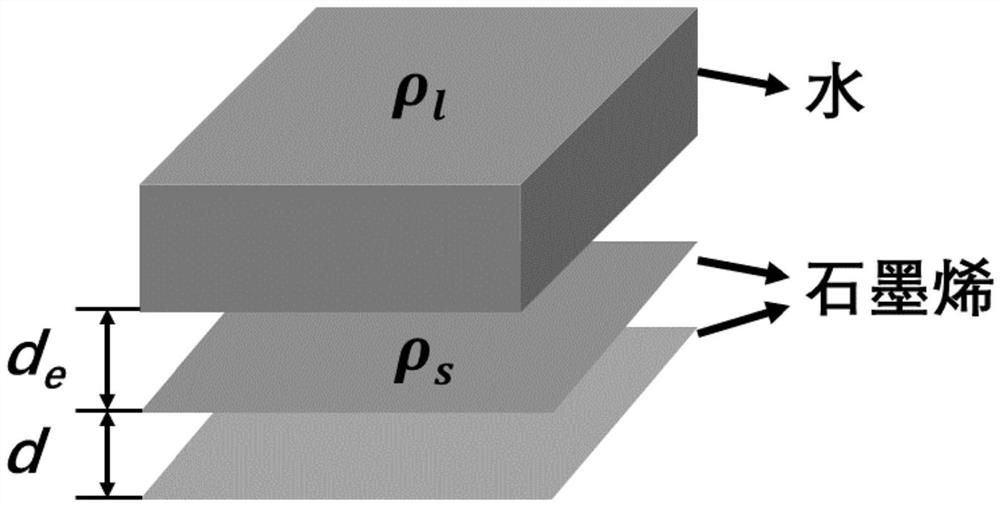

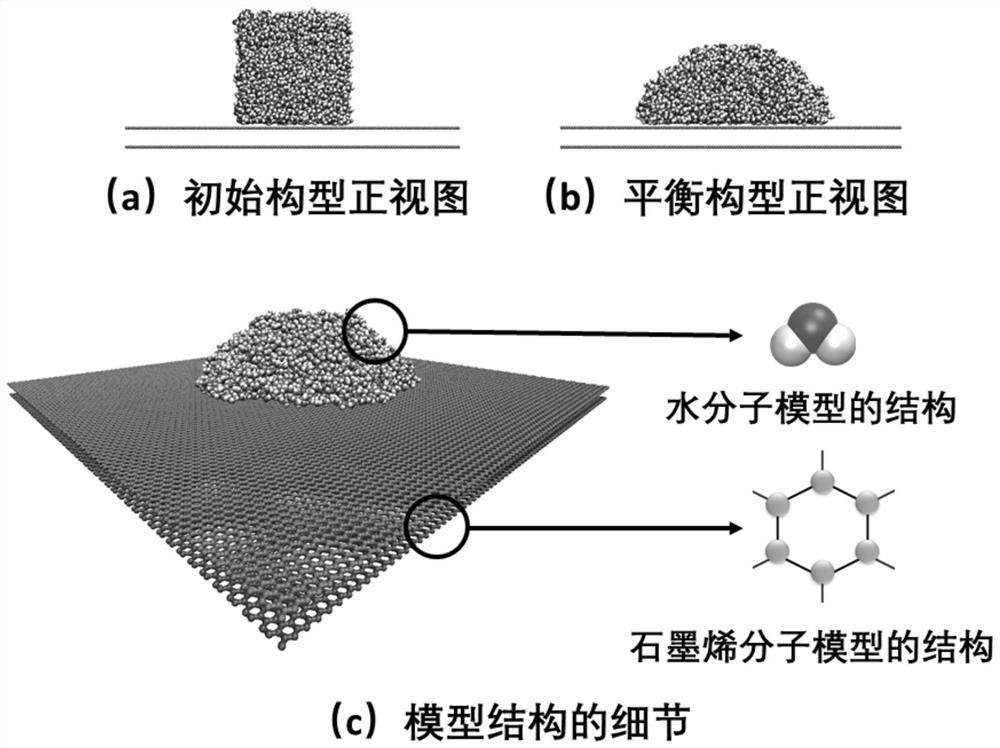

Method for accurately regulating and controlling wettability of double-layer two-dimensional material based on interlayer spacing

ActiveCN114741885AQuick calculationEffective calculationGeneral water supply conservationDesign optimisation/simulationBi layerNumerical models

The invention discloses a method for accurately regulating and controlling wettability of a double-layer two-dimensional material based on interlayer spacing, and belongs to the technical field of calculation of two-dimensional nano materials. Firstly, a numerical model of double-layer two-dimensional material wetting is established; secondly, establishing a wettability characterization theory based on the numerical model; the adhesion energy Wa between solid and liquid in a wetting system is calculated and substituted into a wetting theoretical formula, so that an expression of a contact angle of a wetting theoretical numerical model is established. And finally, through the steps, establishing an explicit relational expression of the contact angle theta and the interlayer spacing d for representing wettability. According to the method, the wettability can be accurately regulated and controlled based on the interlayer spacing of the two-dimensional material, the established theoretical model can accurately, quickly and effectively calculate the contact angle of the liquid on the surface of the corresponding material, the efficiency is greatly improved, a new strategy is provided for constructing the wettability-controllable material surface, and the method is suitable for popularization and application. And the problems of high cost, difficulty in operation, poor applicability and the like caused by experiments are avoided.

Owner:DALIAN UNIV OF TECH

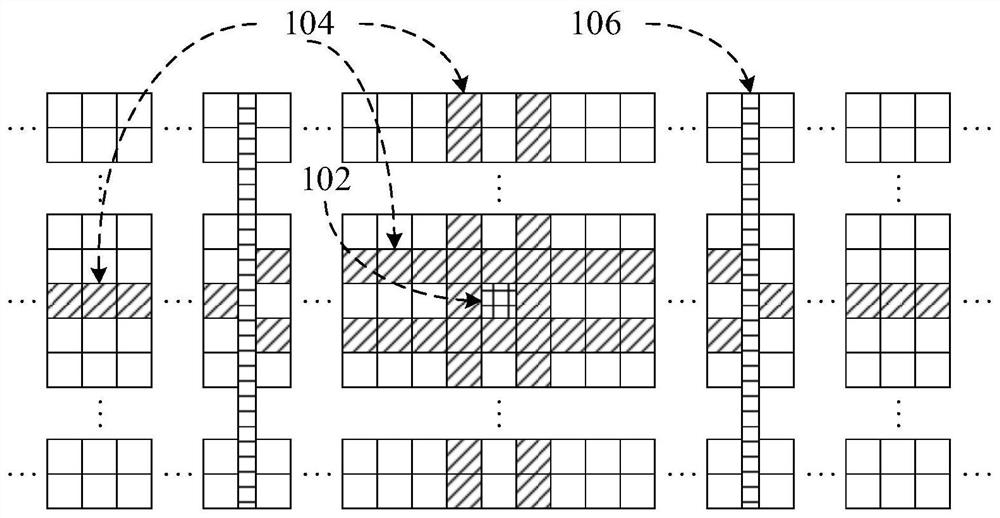

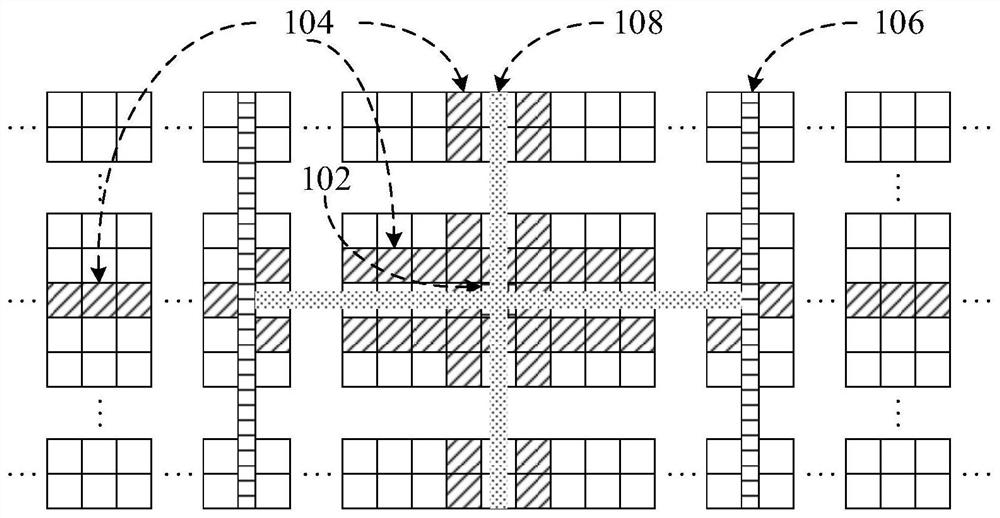

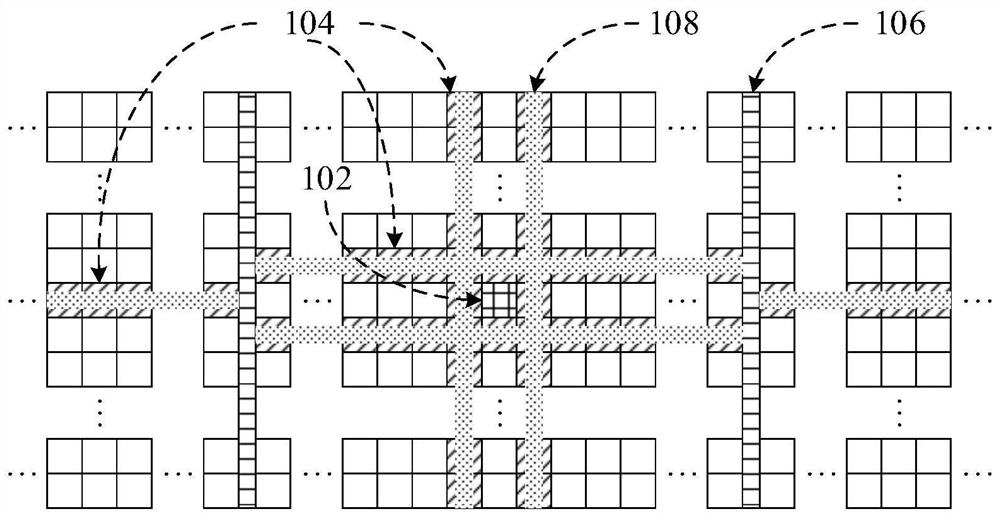

Bump connection placement in quantum devices in a flip chip configuration

PendingCN113906429AQuantum computersSemiconductor/solid-state device detailsQuantum devicesEngineering

Within a layout of a first surface in a flip chip configuration, a bump restriction area is mapped according to a set of bump placement restrictions, wherein a first bump placement restriction specifies an allowed distance range between a bump and a qubit chip element in a layout of the first surface, and wherein a second bump placement restriction specifies an allowed distance range between the bump and a qubit chip element in a layout of a second surface in the flip chip configuration. An electrically conductive material is deposited outside the bump restriction area, to form the bump, wherein the bump comprises an electrically conductive structure that electrically couples a signal between the first surface and the second surface and is positioned according to the set of bump placement restrictions.

Owner:IBM CORP

Wafer detection data processing method and computer readable storage medium

PendingCN114186524AIncrease productionImprove yieldCharacter and pattern recognitionStatic storageWaferingDependability

The invention provides a wafer detection data processing method and a computer readable storage medium, and relates to the technical field of wafer manufacturing. The wafer detection data processing method comprises the following steps: determining a new failure bit generated in a completed wafer detection process; obtaining a repair record of the new invalid bit and a repair record of an adjacent bit of the new invalid bit; the repair record is analyzed to determine attribute information of the new failure bit and the adjacent bit, and the attribute information comprises at least one of position information, standby circuit information, a unit graph of the new failure bit and a wafer detection process; performing classified learning according to the attribute information to obtain a failure bit prediction model; and predicting a failure bit to be subjected to wafer detection through the failure bit prediction model. According to the technical scheme, the reliability of failure bit prediction is improved, and the yield of wafer products can be improved.

Owner:CHANGXIN MEMORY TECH INC

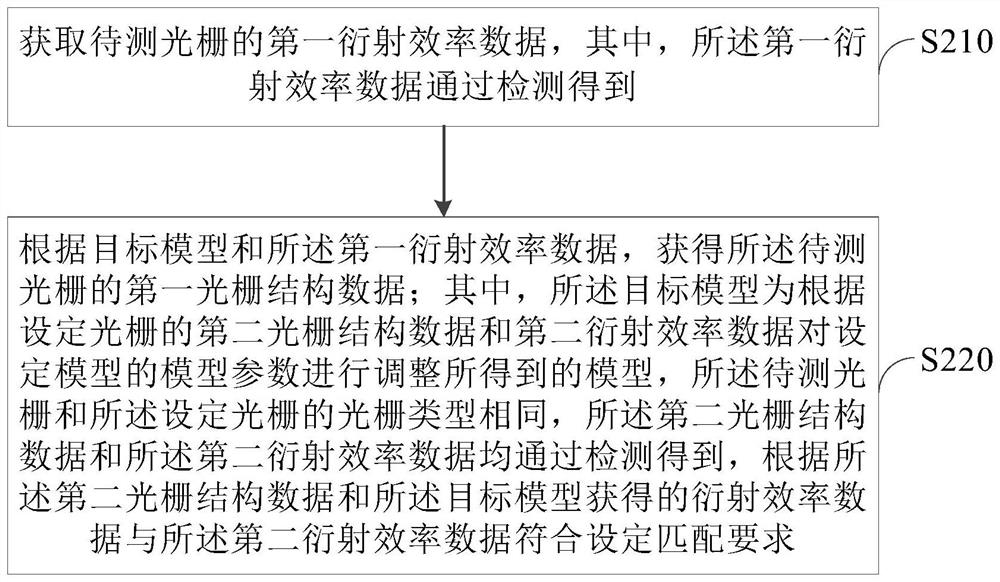

Method and device for acquiring grating structure data and readable storage medium

PendingCN114169224AAccurately reflectDesign optimisation/simulationNeural architecturesMaterials scienceModel parameter

The invention relates to a method and device for obtaining grating structure data and a readable storage medium, and the method comprises the steps: obtaining the first diffraction efficiency data of a to-be-detected grating, and enabling the first diffraction efficiency data to be obtained through detection; obtaining first grating structure data of the grating to be measured according to a target model and the first diffraction efficiency data; wherein the target model is a model obtained by adjusting model parameters of a set model according to second grating structure data and second diffraction efficiency data of a set grating, and the grating type of the to-be-measured grating is the same as that of the set grating. The second grating structure data and the second diffraction efficiency data are obtained through detection, and the diffraction efficiency data obtained according to the second grating structure data and the target model and the second diffraction efficiency data meet set matching requirements.

Owner:GOERTEK INC