AD7609 multi-channel analog signal synchronous acquisition system based on FPGA

A technology of AD7609 and synchronous acquisition, applied in general control systems, simulators, control/regulation systems, etc., can solve problems such as inability to realize multi-channel synchronous acquisition, susceptibility to external electromagnetic interference, complex circuit design, etc., to increase signal drive ability and anti-interference ability, realize the effect of configurable and simple sequence

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0021] This embodiment provides an FPGA-based AD7609 multi-channel analog signal synchronous acquisition system, through optimized system hardware circuit design, and FPGA hardware programming, receiving external multi-channel analog current signals, and synchronously acquiring multi-channel analog signals.

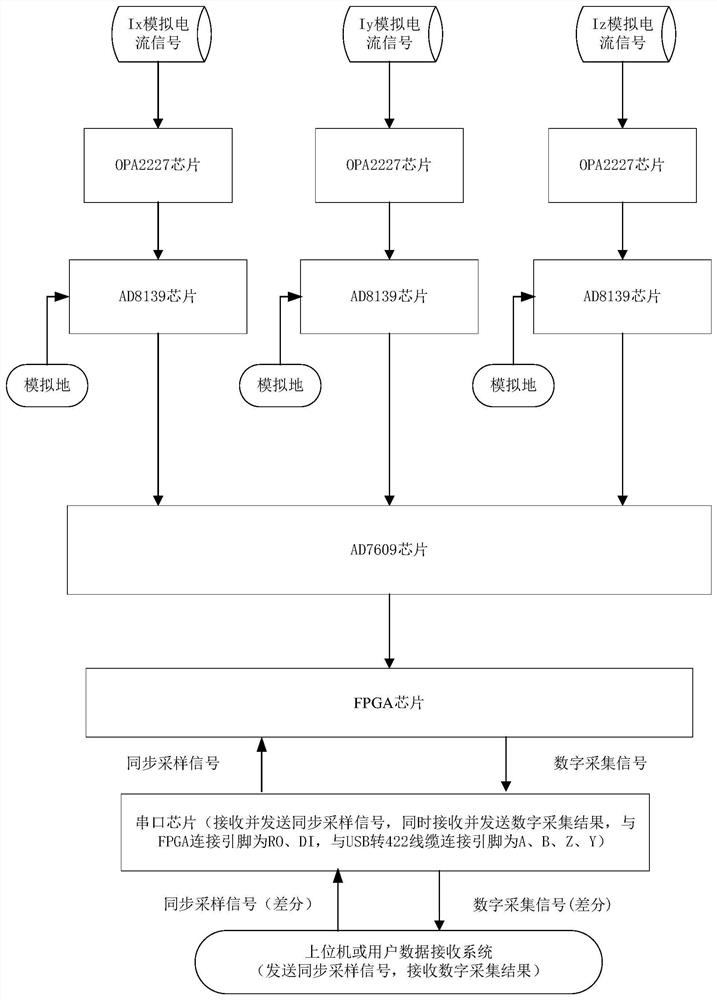

[0022] Such as figure 1 As shown, the system includes: FPGA (Field Programmable Gate Array, Field Programmable Gate Array) chip, OPA2227 (which is a dual-channel, high-precision, low-noise operational amplifier) chip, AD8139 (a low-noise, single-ended to differential / differential to differential, high-performance differential amplifier) chip, AD7609 (an eighteen-bit, eight-channel, true differential, synchronous sampling analog-to-digital converter) chip, serial port chip (a low- Power consumption, data transceiver providing ±15KV electrostatic protection, model adopts ADM3077E) and host computer.

[0023] The connection relationship of the system is as follows: thre...

Embodiment 2

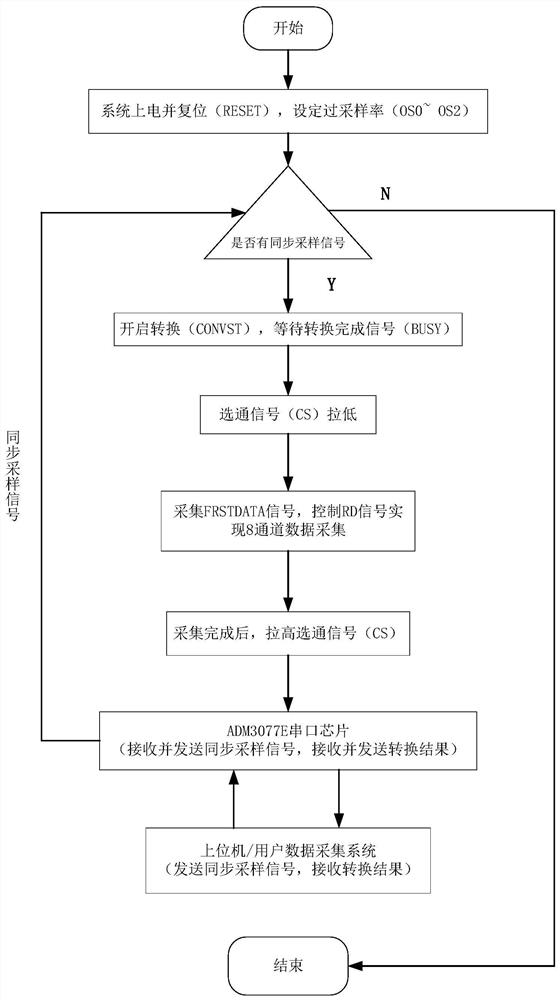

[0027] On the basis of Example 1, such as figure 2 As shown, the differential analog input range of parallel acquisition of AD7609 chip is ±5V, the logic driving voltage is 3.3V, and a single CONVST signal (CONVST A is connected to CONVST B) is controlled to realize eight-channel synchronous conversion, and the oversampling rate is set to 16 (OS [2:0] is 3'b100, high signal-to-noise ratio), adopts the way of separating CS and RD, and writes Verilog HDL program according to the parallel acquisition timing generated by AD7609 chip to realize the parallel acquisition of AD7609.

Embodiment 3

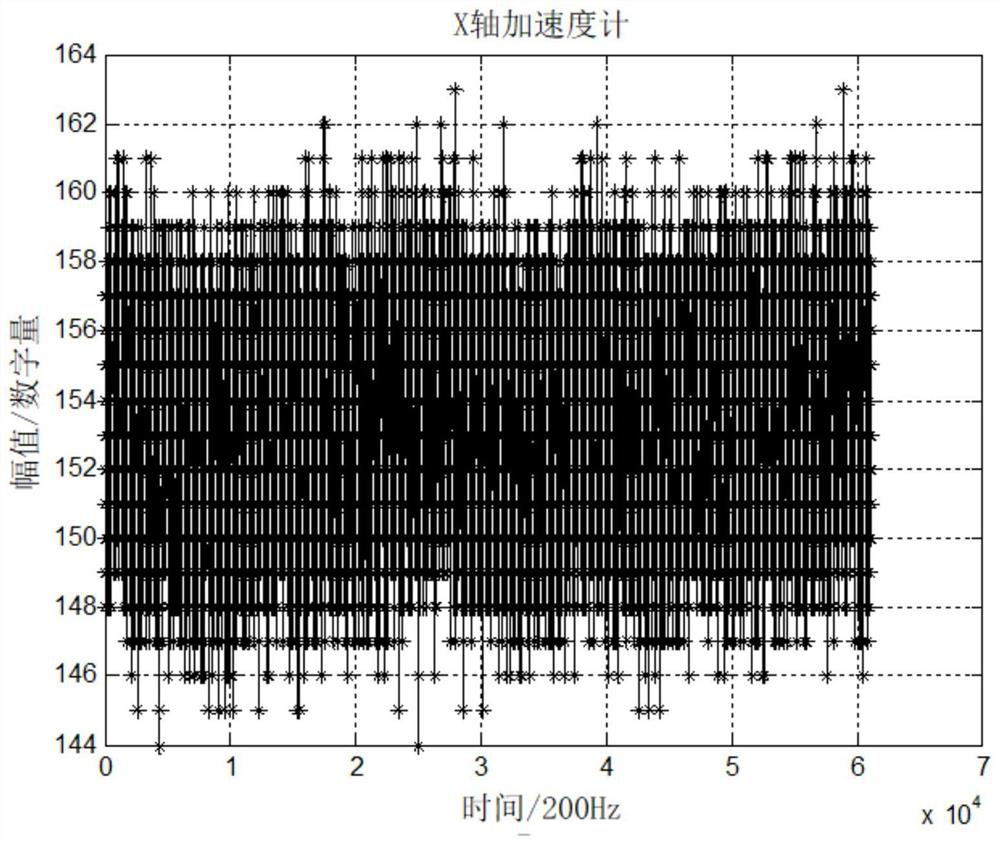

[0029]On the basis of embodiment 1 or 2, setting synchronous collection frequency is 200Hz, and collection time is 5 minutes and 10 seconds, and the axial direction of three-way accelerometer is placed in parallel with three-axis orthogonal coordinate system (X, Y, Z) respectively, The X-axis accelerometer and the Y-axis accelerometer are placed in the same horizontal plane, and the Z-axis accelerometer is in the same direction as the gravity; the collected three-way analog current signal and three-way analog ground signal are input into the system, and the digital acquisition collected by the upper computer is analyzed signal, recording raw data, such as Figures 3 to 5 As shown, the analog-to-digital conversion curves of the digital acquisition signals corresponding to the three-axis accelerometer are drawn respectively through the matlab drawing tool. The abscissa in the three figures is the number of collected data (time multiplied by the sampling frequency), and the ordina...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com