Resistive random access memory and preparation method thereof

A resistive memory, resistive variable technology, applied in semiconductor devices, electric solid state devices, electrical components, etc., can solve the problems of restricting the industrial application of resistive memory, uncontrollability, etc., to improve discreteness, improve consistency, The effect of broad application prospects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] Attached below Figure 2-11 , the specific embodiment of the present invention will be further described in detail.

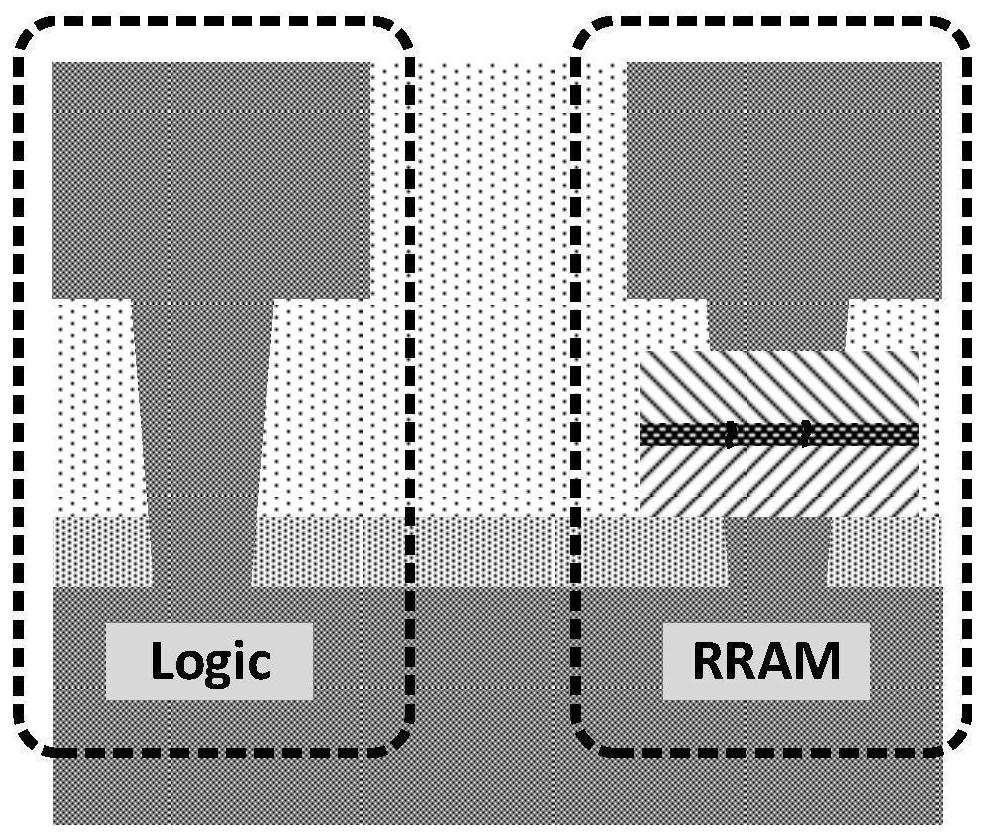

[0041] see first Figure 11 , Figure 11 Shown is a schematic cross-sectional view of a resistive memory product formed by the resistive memory manufacturing method proposed in the present invention. As shown in the figure, the resistive memory includes at least one resistive memory unit; it is characterized in that the resistive memory unit includes:

[0042] The first dielectric layer has a lower electrode contact hole inside, the lower electrode contact hole includes a linear lower electrode and an isolation dielectric layer, one side of the linear lower electrode is close to the side wall of the lower electrode contact hole, so The other side of the linear lower electrode is close to the isolation dielectric layer;

[0043] On the upper surface of the first dielectric layer, the oxide resistive pattern and the upper electrode are sequentially sta...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More