Shield gate trench MOSFET device with electrostatic protection capability and manufacturing method thereof

A technology of electrostatic protection and shielding grid, which is applied in semiconductor/solid-state device manufacturing, electric solid-state devices, electrical components, etc., can solve problems affecting device performance, adverse effects of devices, poor shielding effect, etc. Complexity, the effect of reducing steps

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] The specific implementation manner of the present invention will be described below in conjunction with the accompanying drawings.

[0046] The invention discloses a shielding gate trench MOSFET device with electrostatic protection capability and a manufacturing method thereof. Figure 5 ~ Figure 12 The steps of one embodiment of the fabrication method are shown. specific:

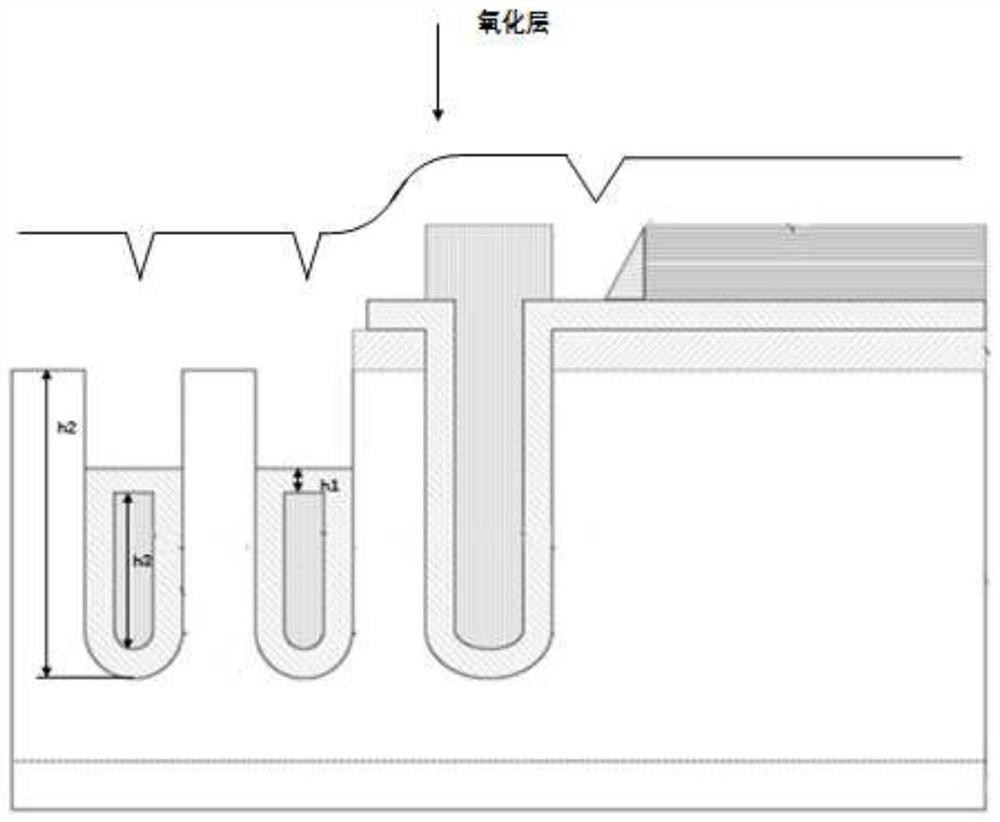

[0047] Figure 5 is a schematic diagram of step S1. Such as Figure 5 As shown, in step S1 , an N-type substrate 1 is provided, and an N-type epitaxial layer 2 is formed on the substrate 1 . The N-type epitaxial layer 2 is located on the N-type substrate 1 . A patterned mask layer is formed on the epitaxial layer 2 , and the upper surface of the epitaxial layer 2 is etched by a dry etching process to obtain the first trench 3 and the second trench 4 .

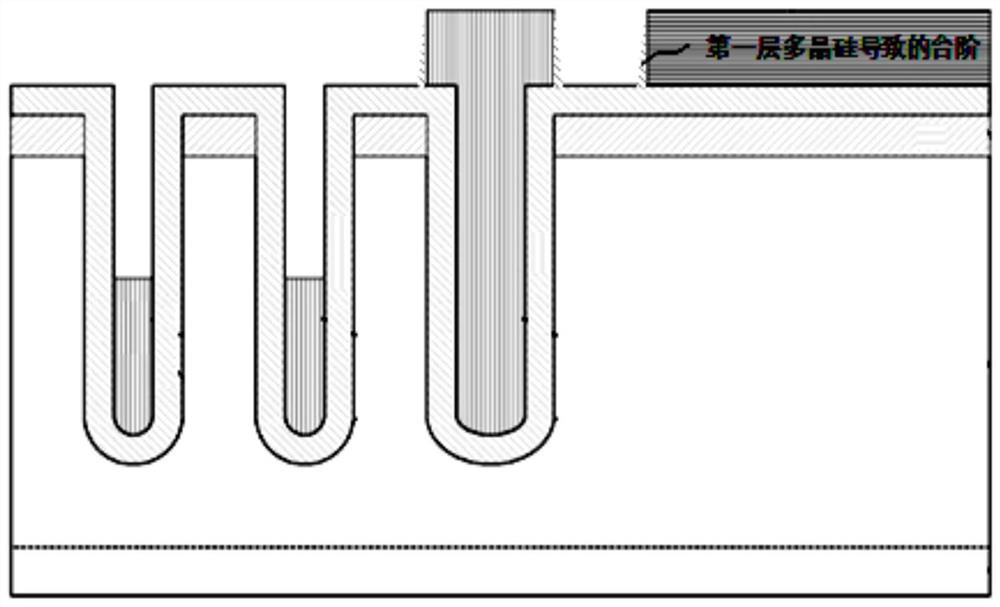

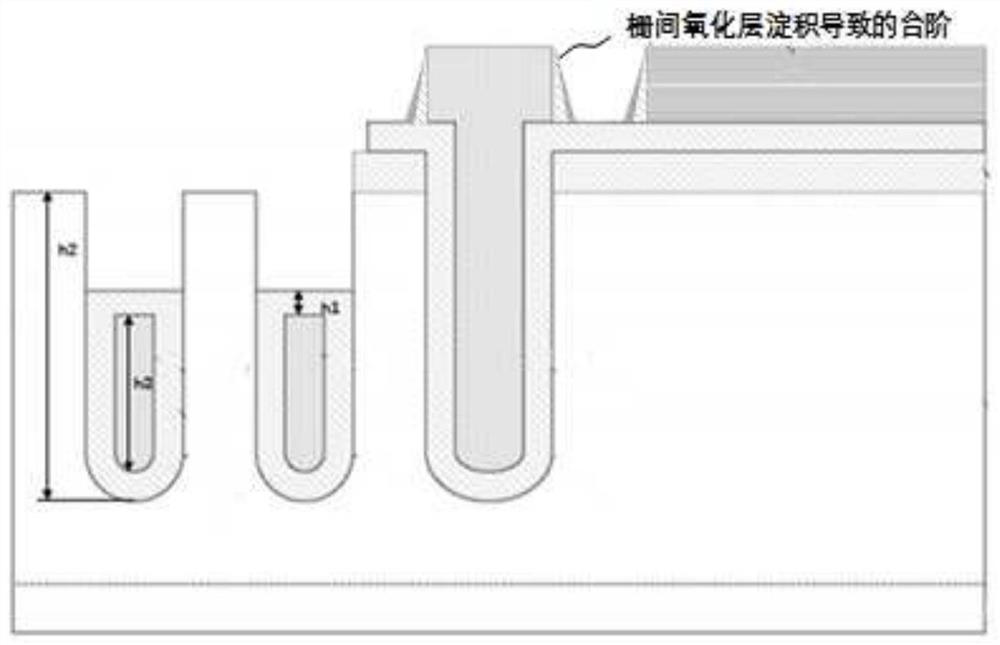

[0048] Step S2 is a step of depositing a first polysilicon layer to form a shielding gate. See step S2 Image 6 , Figure 7 shown.

[0049...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More