Formation method of NOR FLASH

A floating gate and nitride layer technology, applied in electrical components, electrical solid-state devices, circuits, etc., can solve the problems of reduced number, reduced uniformity of erasing, and reduced area.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

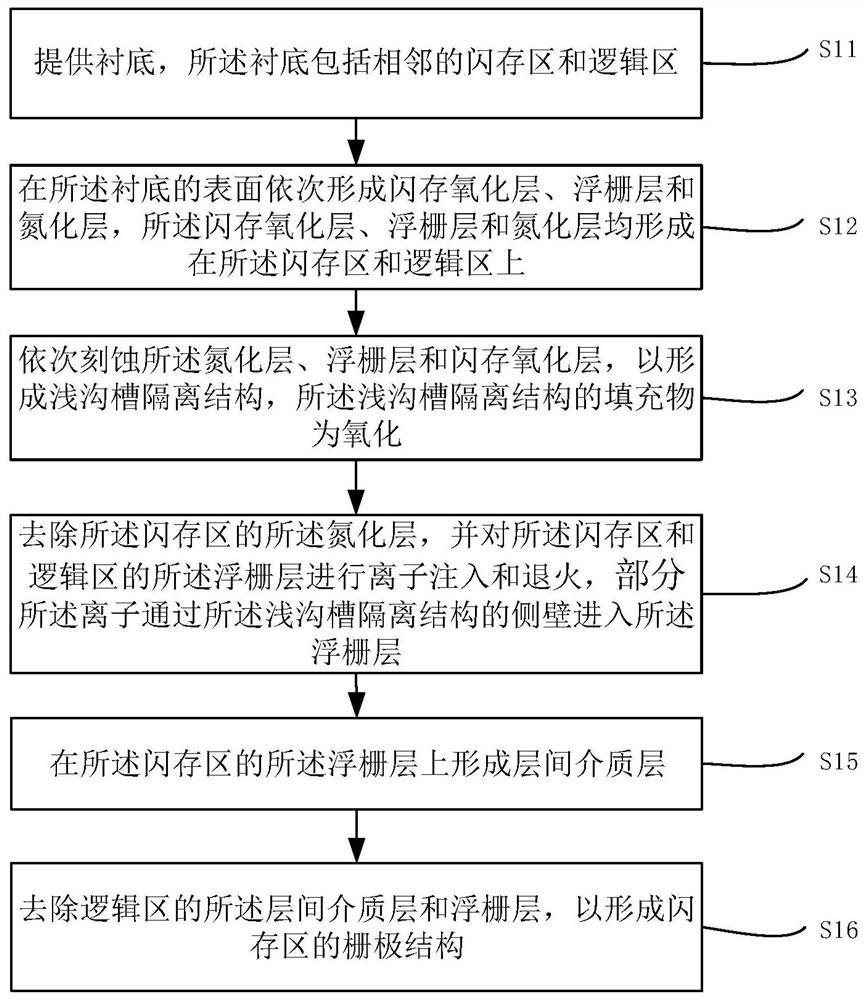

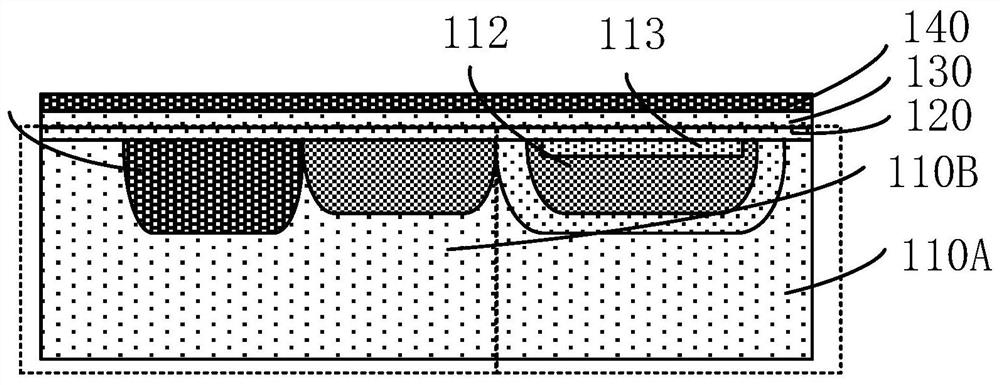

[0025] The specific implementation manner of the present invention will be described in more detail below with reference to schematic diagrams. The advantages and features of the present invention will be more apparent from the following description. It should be noted that all the drawings are in a very simplified form and use imprecise scales, and are only used to facilitate and clearly assist the purpose of illustrating the embodiments of the present invention.

[0026] Hereinafter, the terms "first", "second", etc. are used to distinguish between similar elements, and are not necessarily used to describe a specific order or chronological order. It is to be understood that these terms so used are interchangeable under appropriate circumstances. Similarly, if a method described herein includes a series of steps, the order in which these steps are presented is not necessarily the only order in which these steps can be performed, and some described steps may be omitted and / or...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More