Chip circuit function verification system, method, equipment and storage medium

A circuit function and verification system technology, which is applied in the fields of electrical digital data processing, computer-aided design, special data processing applications, etc., can solve the problems of heavy manual workload, deviation of software application scenarios, and long verification work cycle, etc., to promote Realize, improve time efficiency and avoid waste of human resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

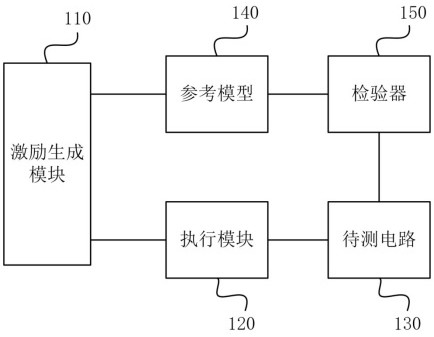

[0036] image 3 It is a schematic diagram of a chip circuit function verification system provided in Embodiment 1 of the present invention. The chip circuit function verification system provided in this embodiment is applicable to the situation of verifying the function of a chip circuit based on the application environment, and can be implemented by software and / or It can be realized by means of hardware, for example, it can include using Verilog language, VHDL (Veri-High-Speed Integrate Circuit Hardware Description Language, ultra-high-speed integrated circuit hardware description language), or a circuit netlist that can be used for simulation generated after compiling the two , Verilog codes or VHDL codes written in other languages, circuit netlists written in other languages with Verilog codes or VHDL codes as intermediate products, etc., can also be hardware circuits implemented based on hardware description languages or netlists.

[0037] Correspondingly, such as ...

Embodiment 2

[0064] Figure 5 It is a schematic diagram of a chip circuit function verification system provided by Embodiment 2 of the present invention. Such as Figure 5 As shown, on the basis of the above-mentioned embodiments, this embodiment specifies the internal structure of the incentive generating module, further refines the incentive generating module 110 into a software simulator 1101 and an automation script 1102, and the software simulator 1101 and the automation script 1102 Script 1102 communication connection.

[0065] Among them, the software simulator 1101 is used to generate chip software simulation results according to the software scene instructions and instruction flow format files, and input the instruction flow data in the chip software simulation results to the automation script 1102 .

[0066] Specifically, the software scenario instruction may be an instruction in a software application scenario of the circuit under test 130 . The instruction stream format file...

Embodiment 3

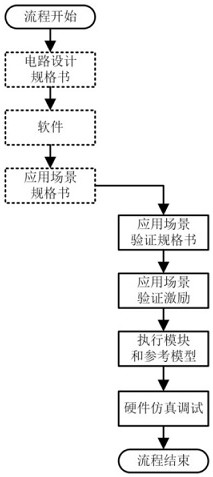

[0098] Figure 11 It is a flowchart of a chip circuit function verification method provided by Embodiment 3 of the present invention. This embodiment is applicable to the situation where the function of the chip circuit is verified based on the application environment. The method can be implemented by the chip circuit function provided by the embodiment of the present invention. verification system, which can be implemented by software and / or hardware. Correspondingly, such as Figure 11 As shown, the method includes the following operations:

[0099] S310. Obtain chip software simulation results through the stimulus generation module, generate target verification stimulus according to the chip software simulation result, and input the target verification stimulus to the execution module and the reference model.

[0100] S320. Perform parameter configuration of the circuit under test according to the target verification stimulus through the execution module, and generate a t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More