NMOS device manufacturing method for improving stress film coverage uniformity, and NMOS device thereof

A device manufacturing method and thin-film covering technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as reducing stress film stress, reducing stress film growth speed, and reducing stress transmission

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

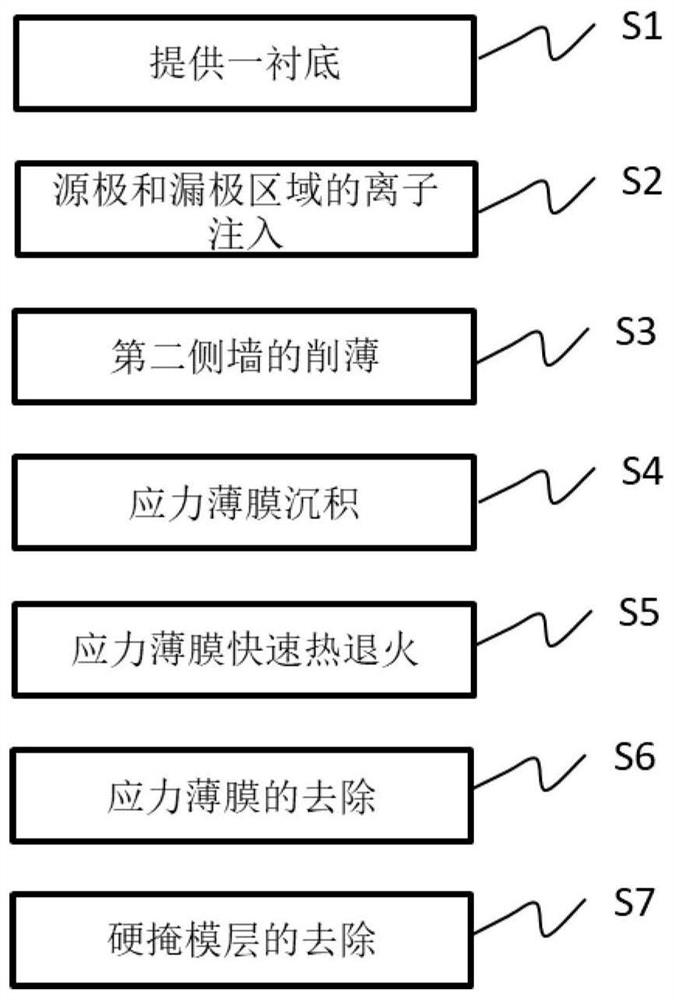

[0027] The NMOS device manufacturing method for improving stress film coverage uniformity of the present invention comprises the following steps:

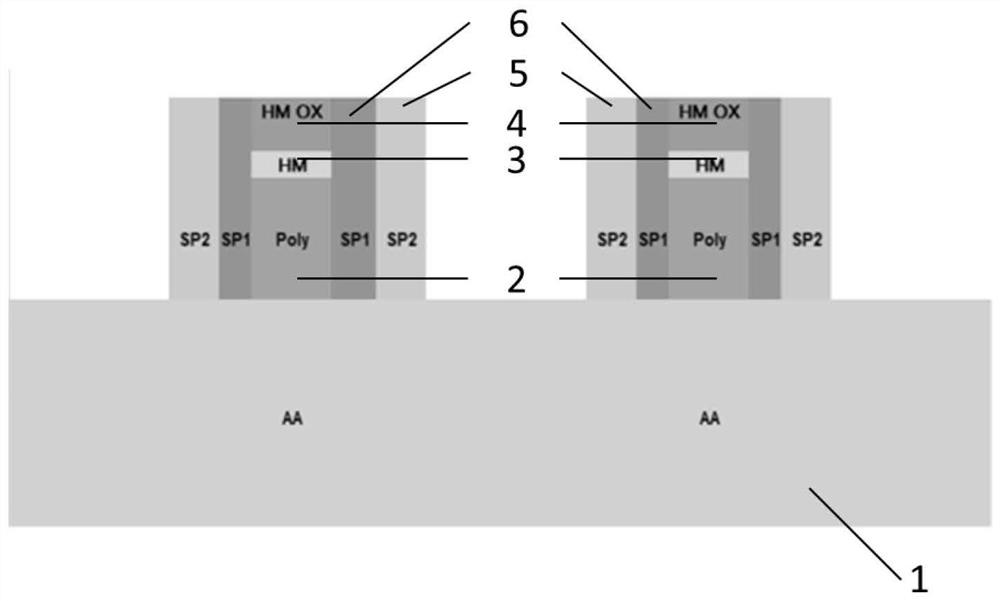

[0028] Step S1, such as image 3 A substrate 1 is provided, and at least two gates 2 are formed on the substrate 1, a first hard mask layer 3 and a second hard mask layer 4 are provided on each gate, and a first hard mask layer 4 is formed on both sides of each gate. One side wall 6 and the second side wall 5. The substrate also includes source and drain electrodes (not shown in the figure)

[0029] The process used in step S1 is a prior art process, and the following is only an exemplary description.

[0030] For example, each region is defined after the substrate is selected, and ion implantation is performed in the defined P well region, exemplarily high-energy boron ion implantation, to form a local P-type region. Rapid thermal annealing (RTP / RTA) after photoresist removal can reduce the diffusion of impurities.

[0031] Ga...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More