Preparation method of bipolar gating memristor and bipolar gating memristor

A memristor and gating technology, applied in the direction of electrical components, etc., can solve the problems such as the difficulty and complexity of process preparation, and achieve the effect of increasing the number of pulse erasing and writing, reducing the difference, and improving the holding capacity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

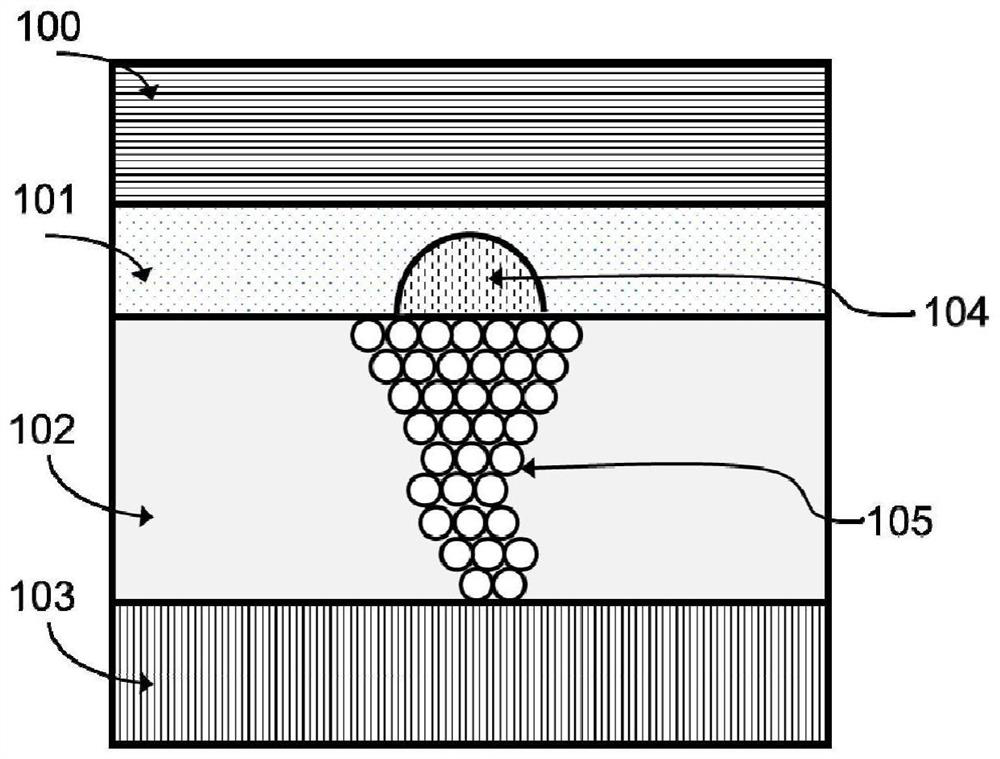

[0034] To this end, the present invention proposes a new type of memristive device structure with built-in bipolar gating and its preparation method. The device based on this reliable structure shows excellent overall performance improvement, such as free of large voltage initialization process, preparation at room temperature , simple structure, excellent performance in various operating modes, and no high-temperature annealing step. The cross-array stacking structure of the built-in bipolar gating memristor based on the present invention will provide a hardware foundation for the next generation of non-volatile storage, full memristive neural network architecture, and reconfigurable logic circuits.

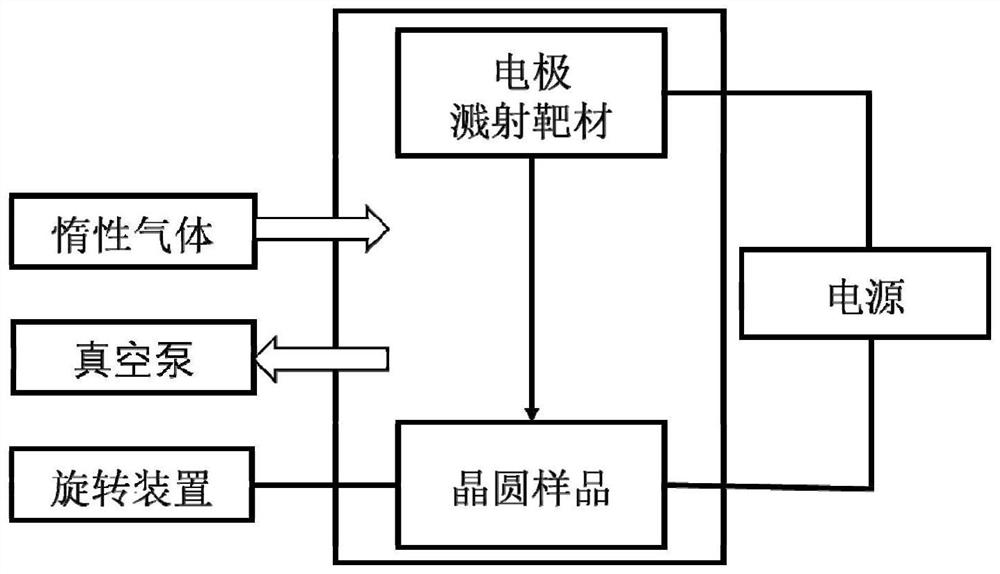

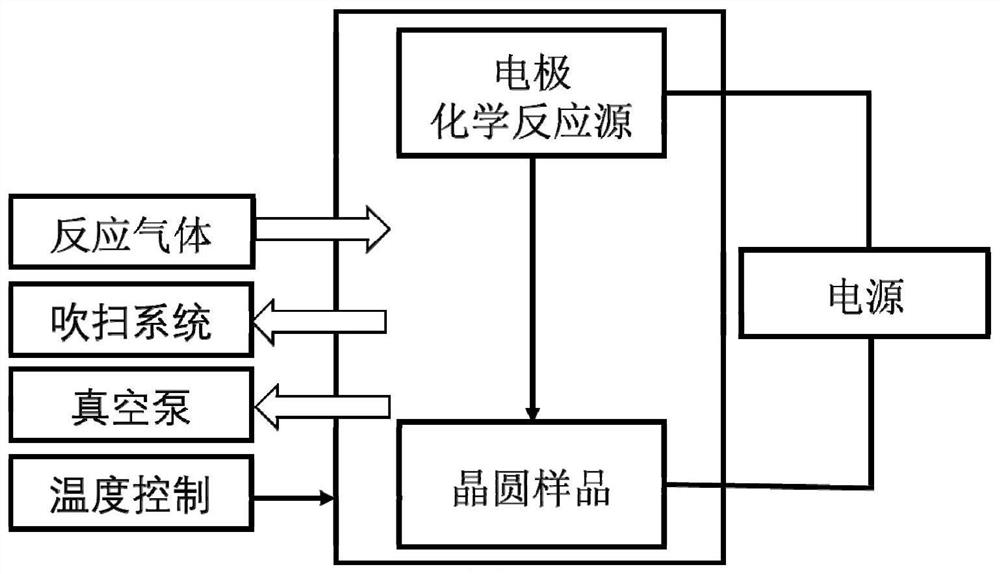

[0035] The present invention aims at the above-mentioned existing process preparation problems, and provides a gating memristor and its preparation method, which form excellent built-in bipolar gating characteristics through the spontaneous oxidation process of the upper electrod...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More