Method for extracting clock tree based on comprehensive netlist in chip design and application

A chip design and clock technology, applied in the field of clock tree extraction, can solve the problems of increasing iteration risk, delay time, increasing iteration time, etc., and achieve the effect of improving work efficiency and correctness, shortening verification cycle, and shortening iteration time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

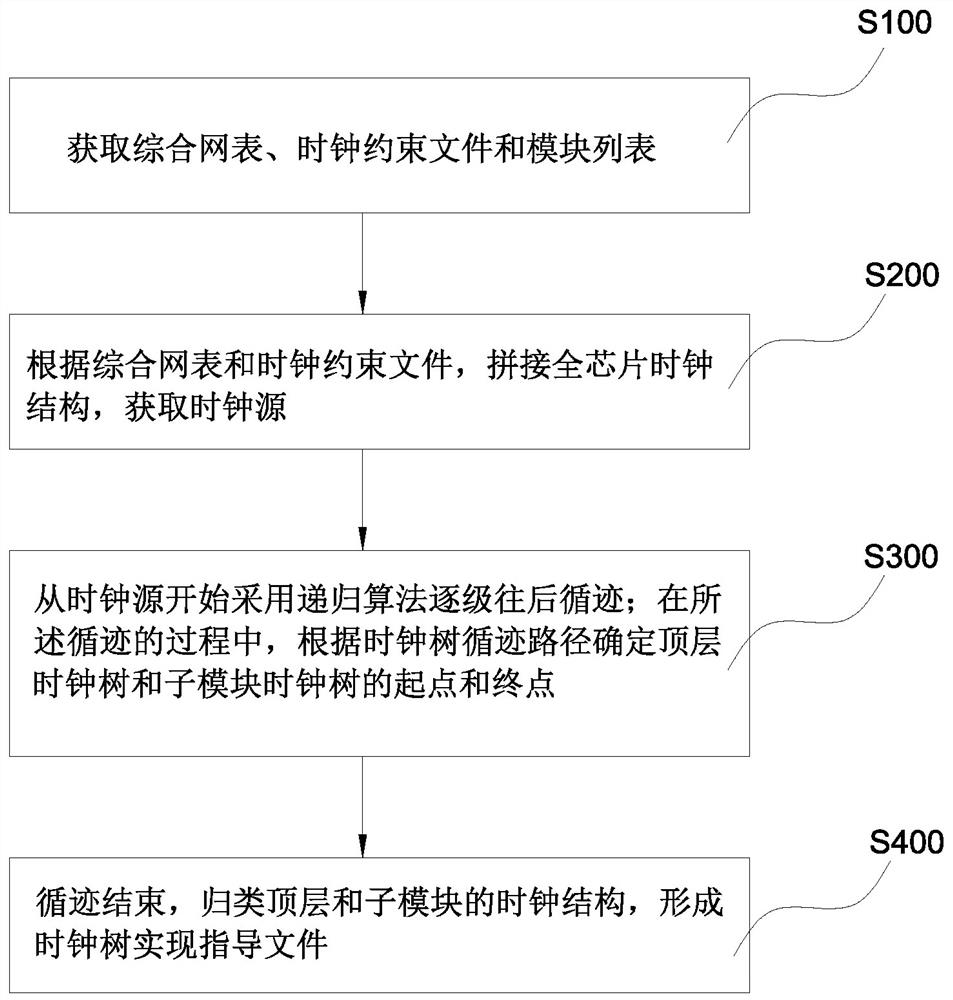

[0052] see figure 1 As shown, a method for extracting a clock tree based on a comprehensive netlist in chip design is provided.

[0053] The method comprises the steps of:

[0054] S100, acquiring a comprehensive netlist, a clock constraint file and a module list.

[0055] In the logic synthesis step of the chip design process, a logic synthesis netlist is generated, and the logic synthesis netlist records the connection relationship between logic modules in the chip. In this embodiment, in the logic synthesis step, the logic synthesis netlist information of the chip top layer and sub-modules, as well as the module information and clock constraint file information of the chip segmentation are obtained.

[0056] The module information of the chip segmentation preferably adopts a sub-module list.

[0057] S200, according to the comprehensive netlist and clock constraint file, stitches the clock structure of the whole chip, and obtains the clock source.

[0058] Specifically,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More