Single-layer MoS2-Si-based tunneling diode and preparation method thereof

A tunneling diode, mos2-si technology, applied in the field of single-layer MoS2-Si-based tunneling diodes and its preparation, can solve subthreshold slew rate and off-state characteristics deterioration, trap-assisted tunneling, poor device performance, etc. problems, achieve the effect of reducing interface defect density, high-performance heterogeneous integrated system, and alleviating thermal expansion coefficient mismatch

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] The present invention will be described in further detail below in conjunction with specific examples, but the embodiments of the present invention are not limited thereto.

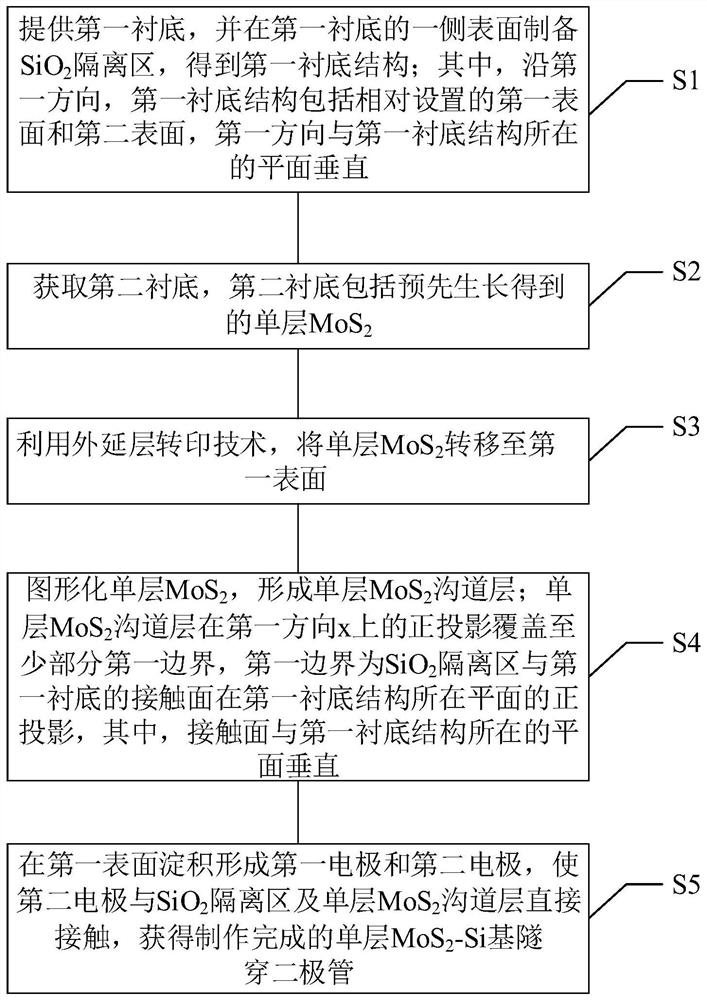

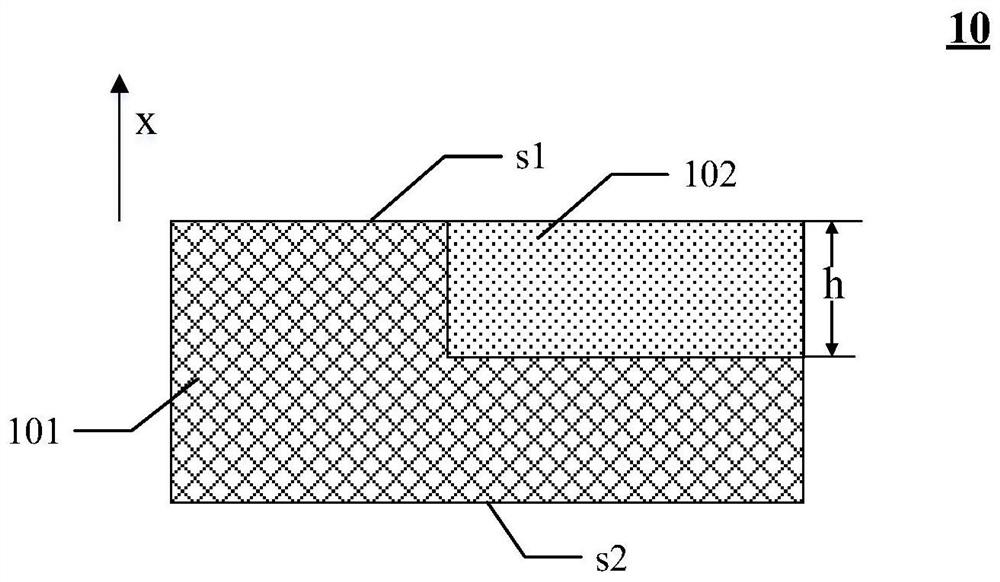

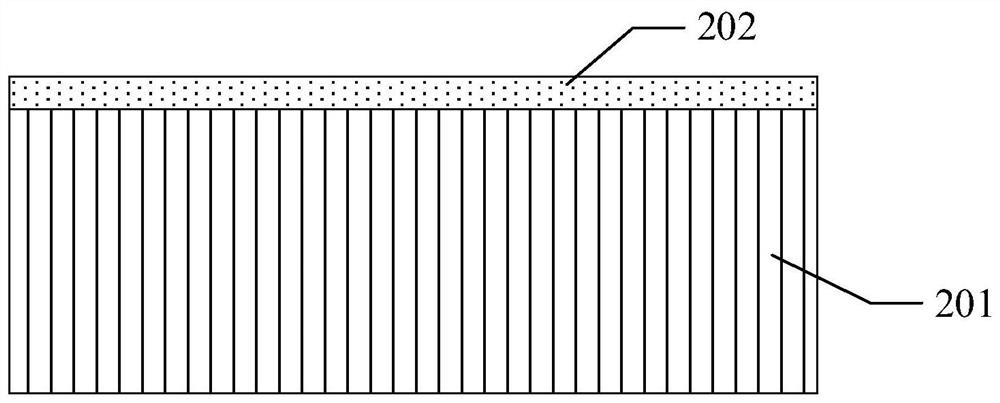

[0044] figure 1 It is the single-layer MoS provided by the embodiment of the present invention 2 - a schematic flow chart of the preparation method of Si-based tunneling diodes, Figure 2-6 It is the preparation of monolayer MoS provided by the embodiment of the present invention 2 -Schematic diagram of the process for Si-based tunneling diodes, Figure 7 It is the single-layer MoS provided by the embodiment of the present invention 2 -Schematic diagram of the structure of a Si-based tunneling diode. See Figure 1-7 , the present invention provides a single-layer MoS 2 -The preparation method of Si-based tunneling diode, comprising:

[0045] S1, providing a first substrate 101, and preparing SiO on one side surface of the first substrate 101 2 The isolation region 102 is used to obtain the ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com