Operational amplifier circuit offset voltage calibration method, device thereof and system

A technology of operational amplifier circuit and offset voltage, applied in improving amplifiers to reduce temperature/power supply voltage changes, improving amplifiers to reduce nonlinear distortion, improving amplifier input/output impedance, etc., can solve the compromise between compensation accuracy and area , a large number of voltage divider resistors, offset voltage elimination and other issues, to achieve the effect of reducing the number, improving linearity, and reducing the occupied area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

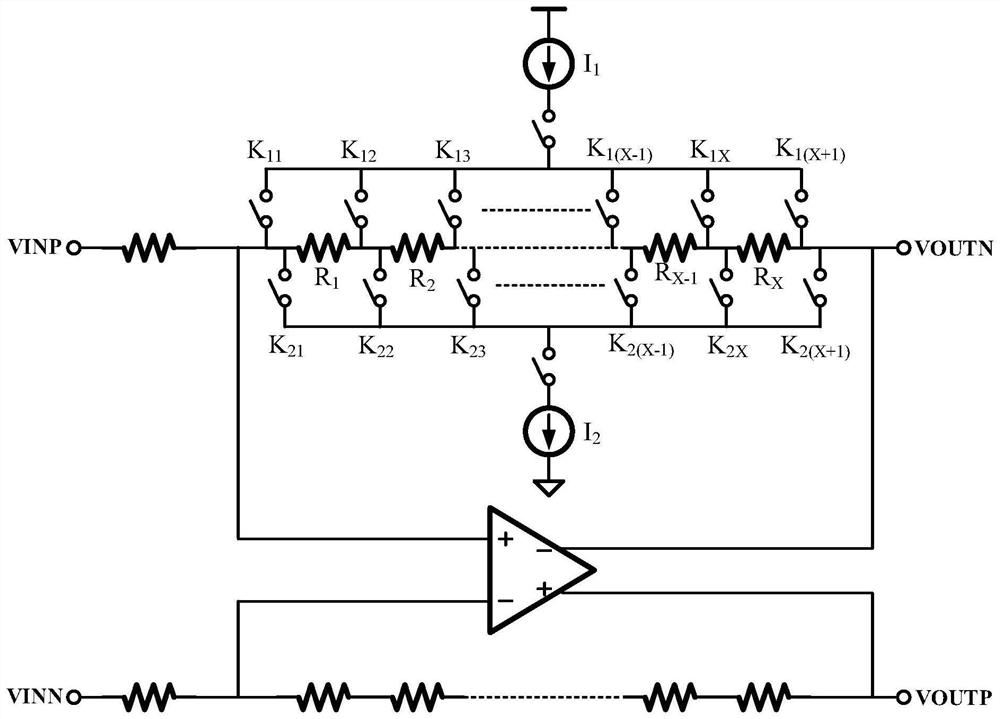

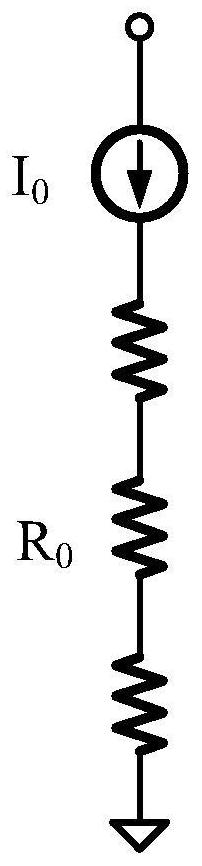

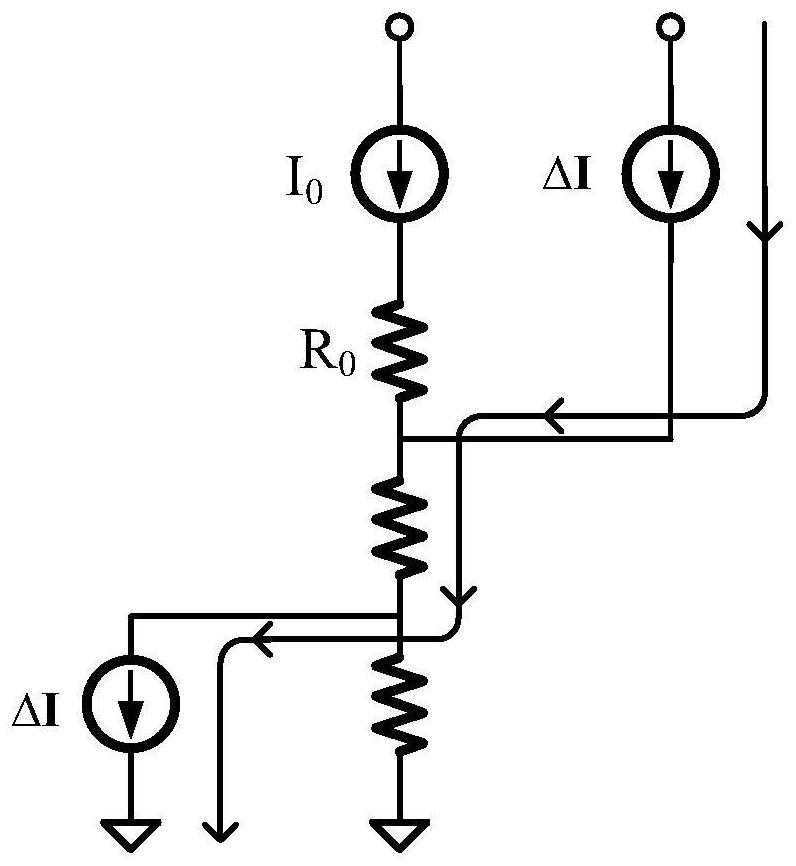

[0060] figure 1 A circuit diagram of a compensation circuit provided in the embodiment of the present application; figure 2 Simplified circuit schematic diagram without calibration; image 3 It is a simplified circuit schematic diagram after calibration; Figure 4 It is a flow chart of a method for calibrating the offset voltage of an operational amplifier circuit provided by an embodiment of the present application.

[0061] In the method for calibrating the offset voltage of the operational amplifier circuit provided in the embodiment of the present application, the compensation circuit includes a current calibration circuit and a resistance calibration circuit; wherein, the first terminal of the resistance calibration circuit is connected to the positive input terminal of the target amplifier in the amplifying circuit to be compensated connected, the second terminal of the resistance calibration circuit is connected with the negative output terminal of the target amplifi...

Embodiment 2

[0084] According to the gain requirement, the amplifying circuit to be compensated is usually composed of multiple operational amplifiers. Connecting the compensation circuit to different operational amplifiers will produce different compensation effects. Therefore, on the basis of the above-mentioned embodiments, the method for calibrating the offset voltage of the operational amplifier circuit provided by the embodiments of the present application further includes:

[0085] According to the actual parameters corresponding to each operational amplifier in the amplifying circuit to be compensated, the operational amplifier with the smallest offset voltage after being connected to the compensation circuit for compensation under the preset test environment is determined as the target operational amplifier.

[0086] In a specific implementation, the actual parameters may specifically include: input common-mode voltage, input common-mode range, output common-mode voltage, output co...

Embodiment 3

[0090] Figure 5 A block flow diagram of a method for calibrating the offset voltage of an operational amplifier circuit provided by the embodiment of the present application; Figure 6 A circuit block diagram of the logic judgment of a method for calibrating the offset voltage of an operational amplifier circuit provided by the embodiment of the present application; Figure 7 An overall offset voltage calibration distribution diagram provided for the embodiment of the present application; Figure 8 It is a schematic diagram of compensation circuit control of a method for calibrating the offset voltage of an operational amplifier circuit provided by the embodiment of the present application.

[0091] On the basis of the above-mentioned embodiments, the embodiments of the present application provide a method for calibrating the offset voltage of an operational amplifier circuit suitable for practical applications. Such as Figure 5 As shown, in order to facilitate the batch ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More