Interface circuit, data transmission circuit and memory

A technology of data transmission circuit and interface circuit, which is applied in the field of data transmission circuit, memory and interface circuit, can solve the problems of DRAM performance to be improved, and achieve the effects of superior structural performance, improved matching degree, and reduced clock path

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] It can be seen from the background art that the performance of the DRAM in the prior art still needs to be improved.

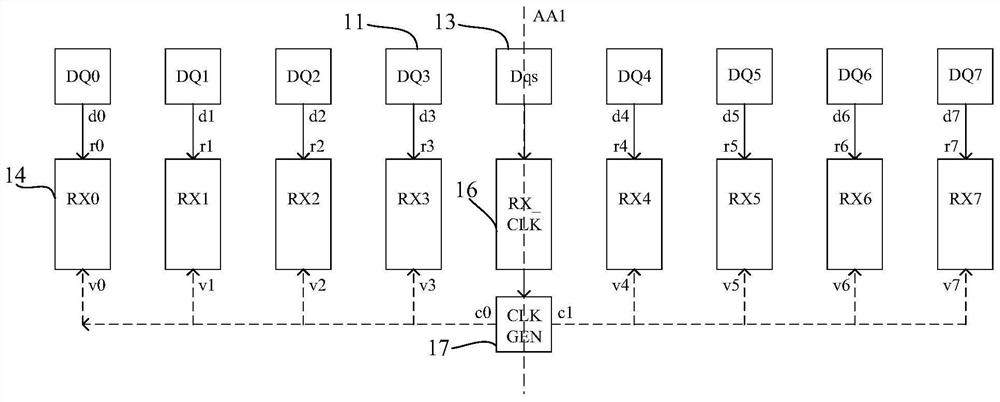

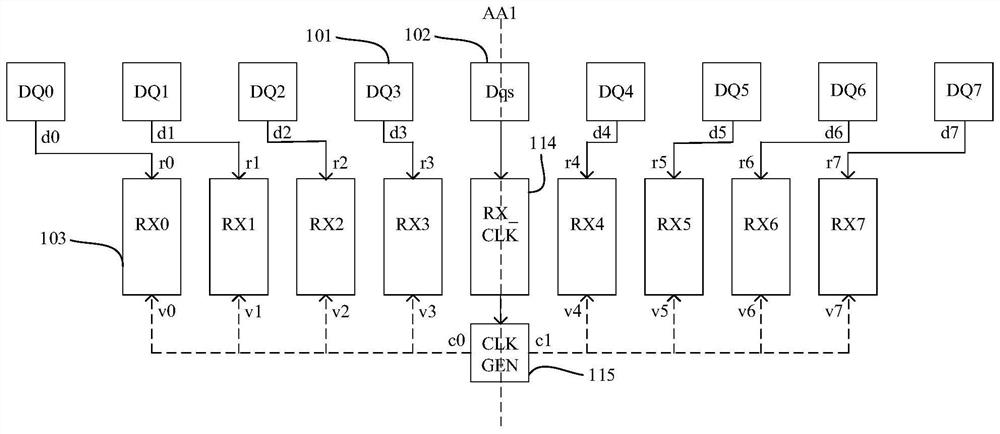

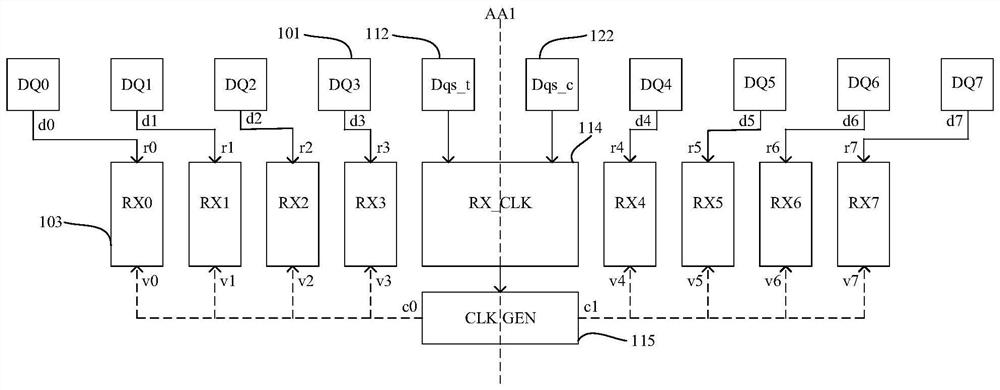

[0039]In the memory, the write data sampling signal (Dqs signal or Wck signal) is used as the clock for writing data; during the write operation, the edge (rising edge and falling edge) of the Dqs or Wck signal should be in timing with the data signal (DQ signal ) (substantially aligned at the center may also be allowed for timing margins). The transmission path of the DQ signal is defined as the data path, and the length of the data path will affect the time when the edge of the DQ signal reaches the device port (such as the data port of the register). The transmission path of the Dqs or Wck signal is defined as the clock path, and the length of the clock path will affect Affects when the Dqs or Wck signal arrives at a device port (such as the clock port of a register), and the difference between the data path of the DQ signal and the clock path of the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com