Vertically stacked complementary field effect transistor and preparation method thereof

A technology of field effect transistors and vertical stacking, applied in transistors, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve the design of low mobility of p-type transistors, low energy consumption of flat panel display drive circuits, working speed, complementary logic circuits, etc. Limitation and other issues to achieve the effect of overcoming the short channel effect, low power consumption, and ultra-low power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] In order to make the content of the present invention easier to understand, the technical solutions of the present invention will be further described below in conjunction with the accompanying drawings through specific embodiments, but the following embodiments are only examples of the present invention and are not intended to It represents the protection scope of rights defined by the present invention, and the protection scope of rights of the present invention shall be determined by the claims.

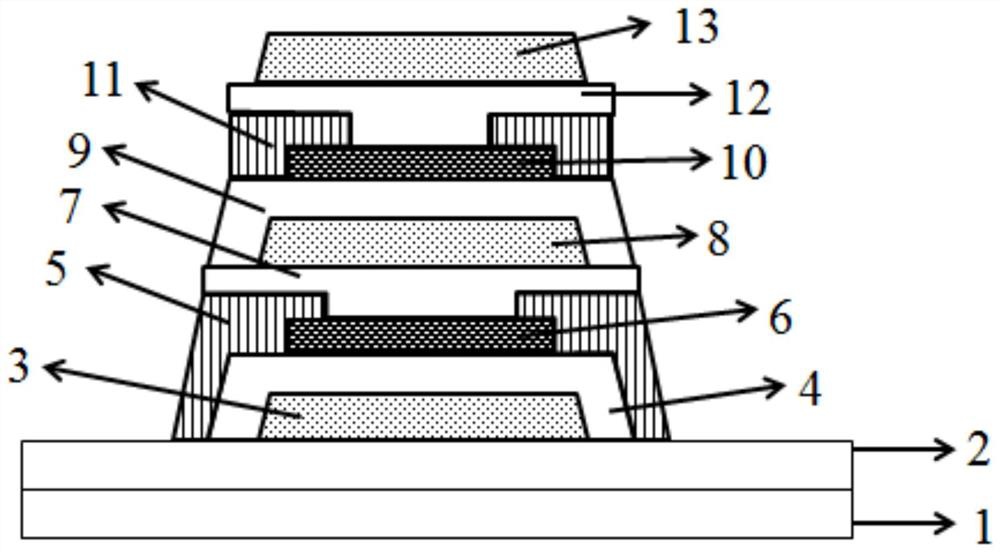

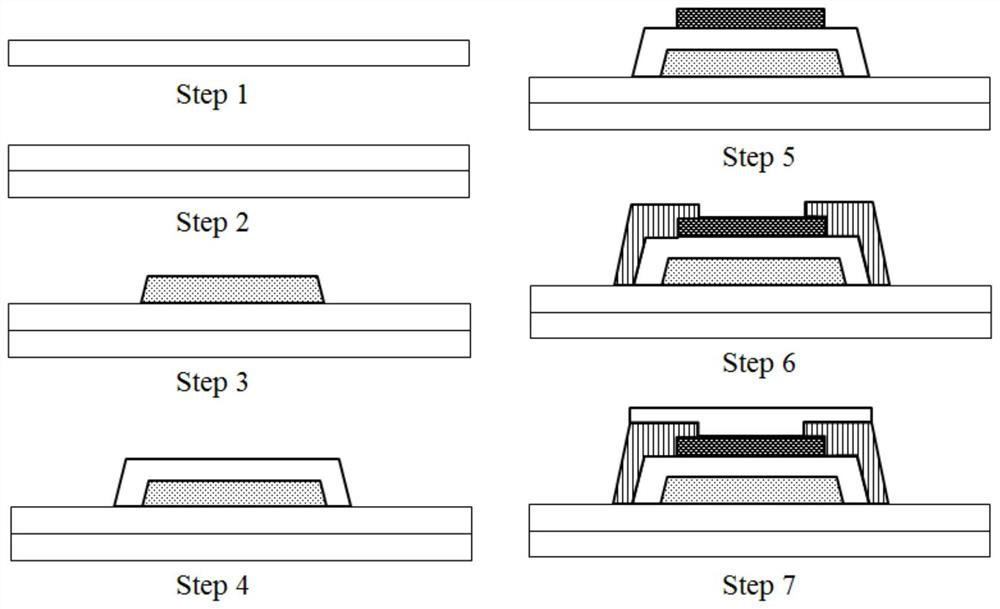

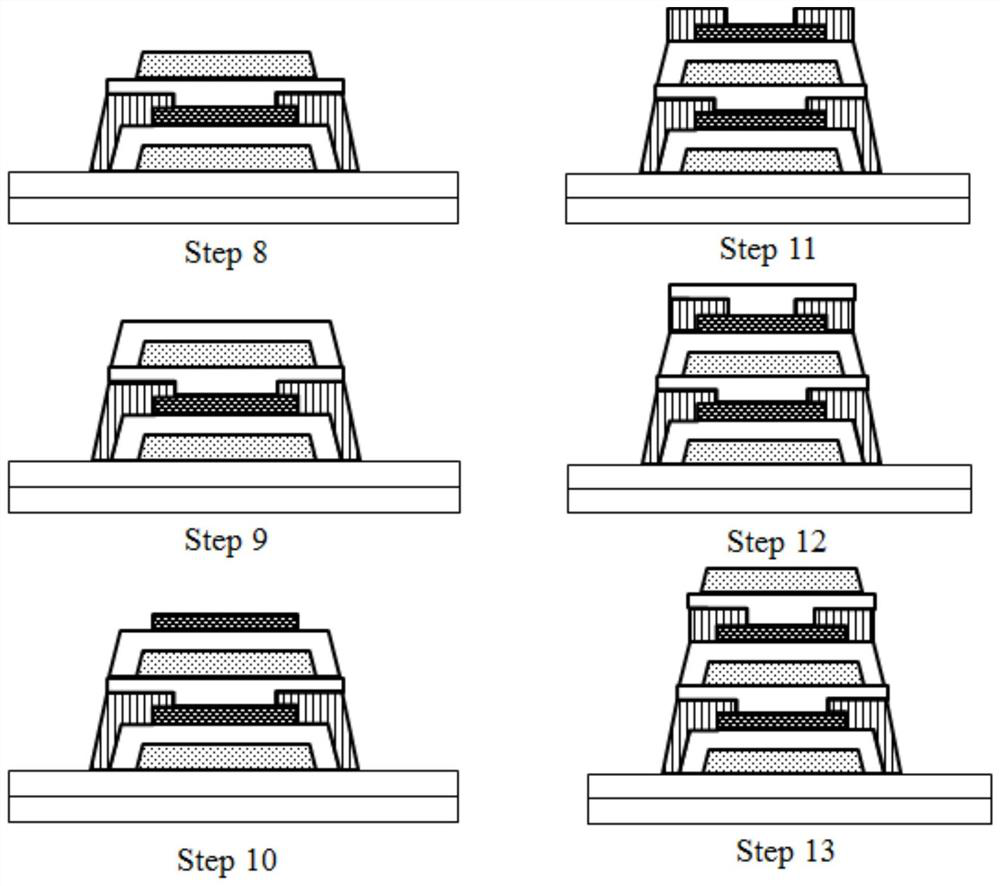

[0030] The preparation of ITO FET see figure 1 and figure 2 :

[0031] The first step: the substrate 1 is Si(111), and the particles, organic matter, oxides, etc. on the substrate are cleaned by a standard RCA cleaning process. After cleaning, the high-purity nitrogen gas is blown dry for use.

[0032]Second step: at first with hydrofluoric acid: the solution of deionized water=1:4 (volume ratio) cleans Si (111) substrate 1, to remove the SiO of surface 2 , and then use...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com