Semiconductor structure and forming method thereof

A semiconductor and isolation structure technology, which is applied in the field of semiconductor structure and its formation, can solve the problems of increased production pressure and cost, poor uniformity of MOS tubes, and devices that cannot meet the requirements, so as to reduce the size of devices, avoid electric field peaks, and improve shock resistance. The effect of breakdown voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The following description provides specific application scenarios and requirements of the present application, and the objectives are to enable those skilled in the art to manufacture and use the contents of this application. Various local modifications to the disclosed embodiments will be apparent to those skilled in the art, and the general principles defined herein can be applied to other embodiments without departing from the spirit and scope of the present application. application. Therefore, the present application is not limited to the embodiment shown, but is the widest range consistent with the claims.

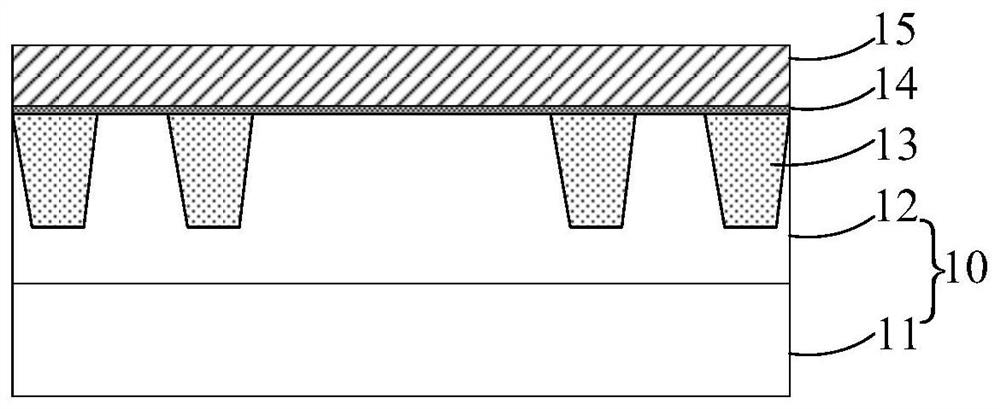

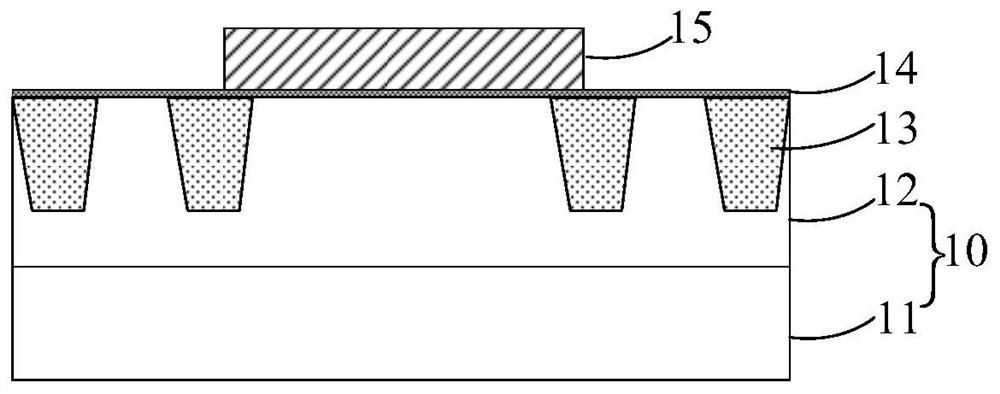

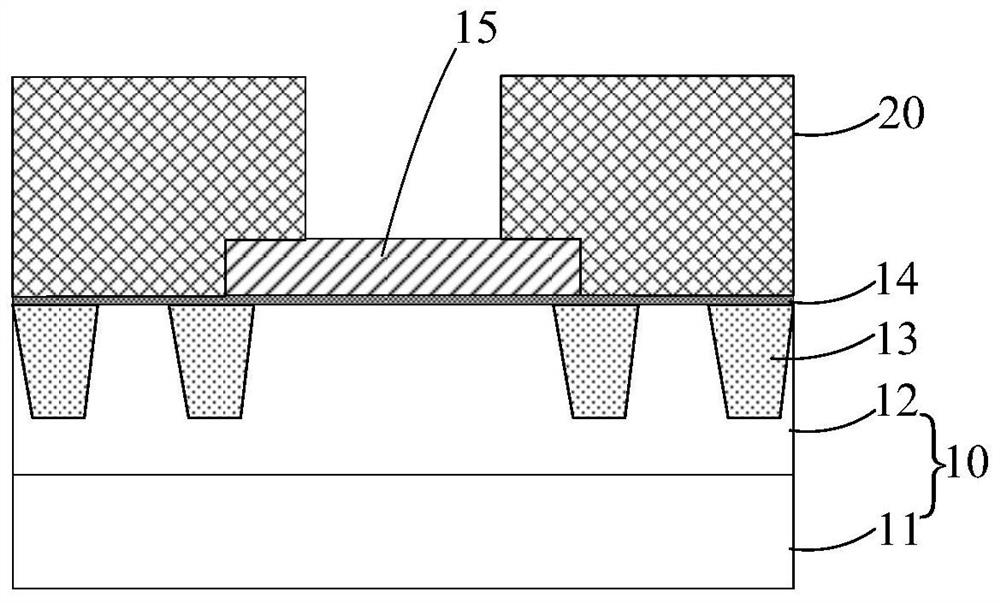

[0027] refer to figure 1 A conventional process that forms an LDMOS device includes providing a substrate 10 comprising a deep well region 11 and a drift region 12. An isolation structure 13 having a plurality of spaced distributions is formed in the drift region 12. The gate dielectric layer 14 and the gate layer 15 are sequentially deposited on the surface of the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More