Low-power-consumption rapid dynamic comparator

A dynamic comparator, low-power technology, applied in the field of microelectronics, can solve problems such as comparator power consumption offset delay, affecting ADC performance characteristics, etc., to achieve the effect of reducing dynamic power consumption and improving comparison accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

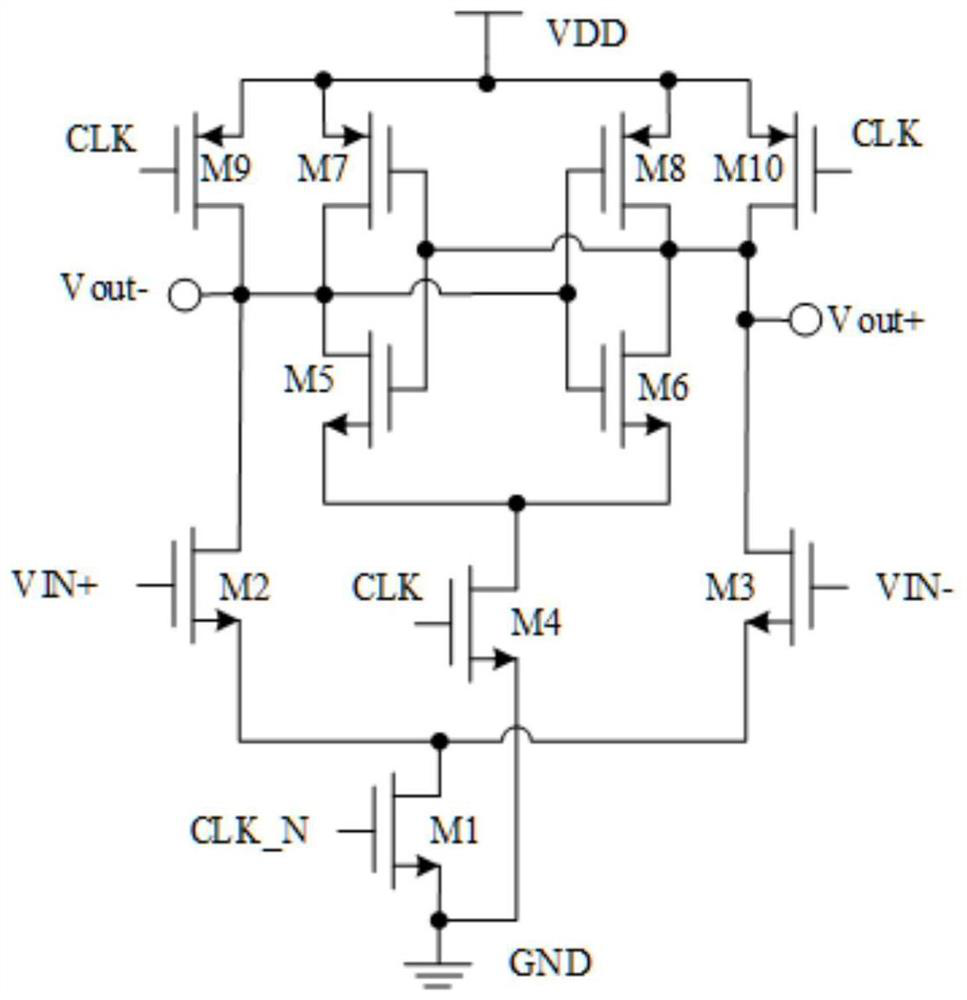

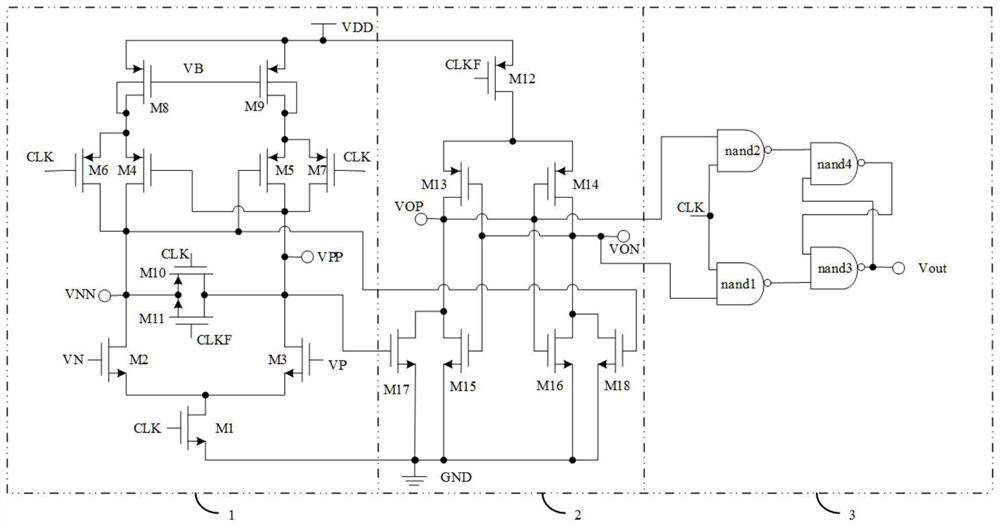

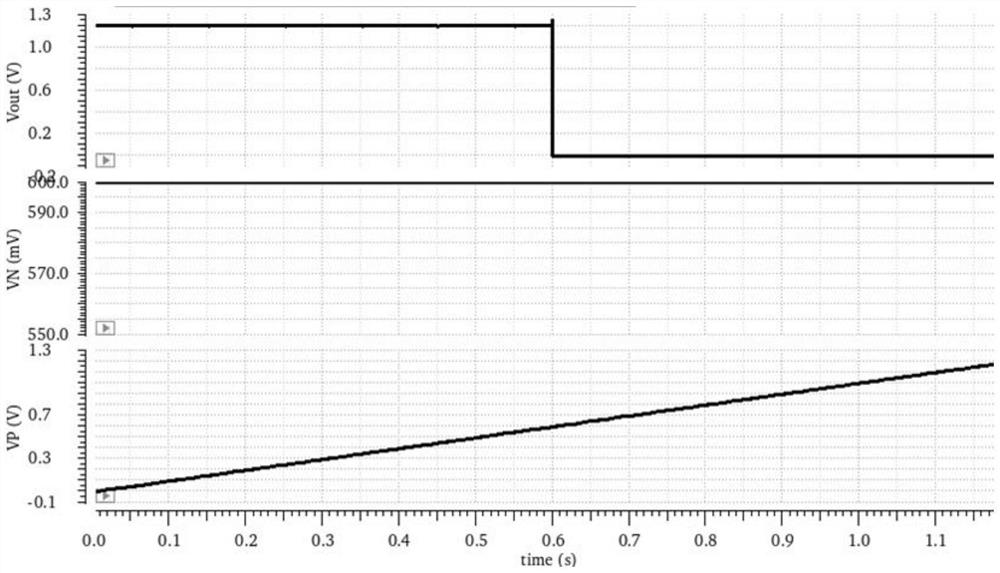

[0023] A kind of low-consumption fast dynamic comparator, it comprises: pre-amplifier 1, comparison circuit 2 and latch 3, wherein the signal output end of said pre-amplifier 1 is connected to the signal input end of said comparison circuit 2, and said comparison circuit The signal output terminal of 2 is connected to the signal input terminal of the latch 3; the pre-amplifier 1 pre-amplifies the input signal of the input terminal VN and the input terminal VP and outputs the signal at the output terminal VNN and the output terminal VPP, the said The comparison circuit 2 dynamically compares the signals of the output terminal VNN and the output terminal VPP of the pre-amplifier 1 and provides an input signal for the latch 3, and the latch 3 receives the output signal of the comparison circuit 2 and The latch is realized under the action of the clock signal CLK, thereby realizing a low-consumption fast dynamic comparator.

[0024] As a preferred technical solution, such as fig...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com