Filter fan-out packaging structure and manufacturing method thereof

A technology of packaging structure and manufacturing method, applied in impedance network, electrical components and other directions, can solve the problems affecting yield, strict flatness requirements of substrate and sealing cover, high split rate, etc., to improve yield and reliability, The effect of avoiding the influence of photolithography offset and enhancing the molding resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0050] refer to Figures 1a-1h , the embodiment of the present application proposes a method for manufacturing a filter fan-out packaging structure, including the following steps:

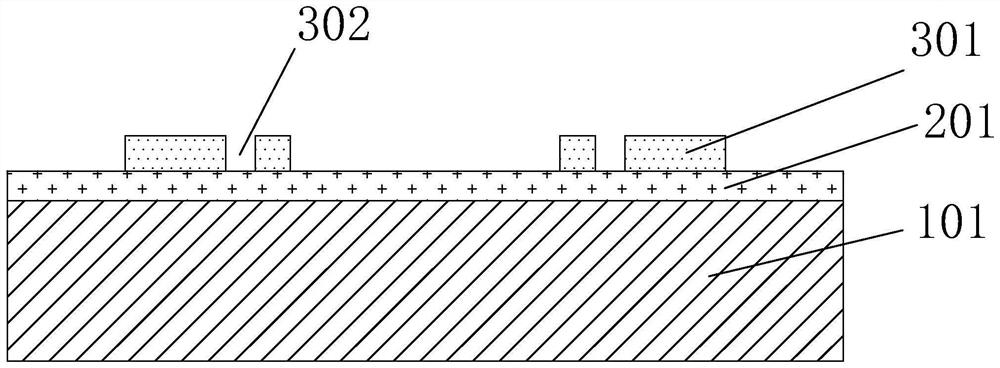

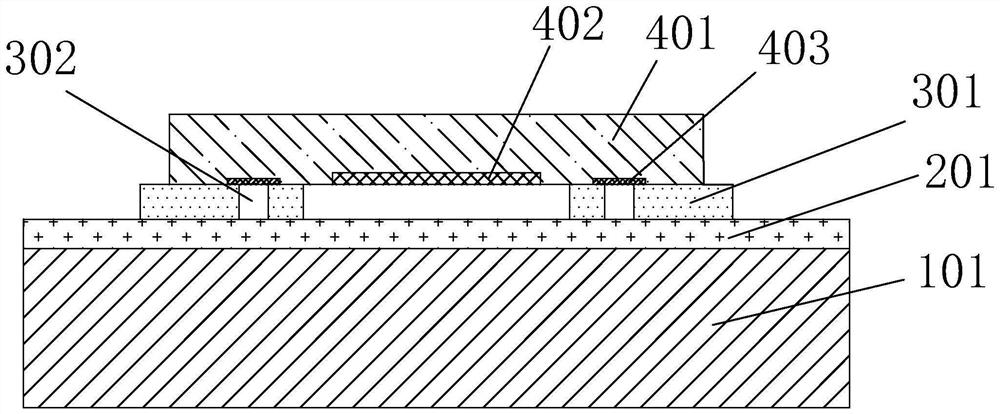

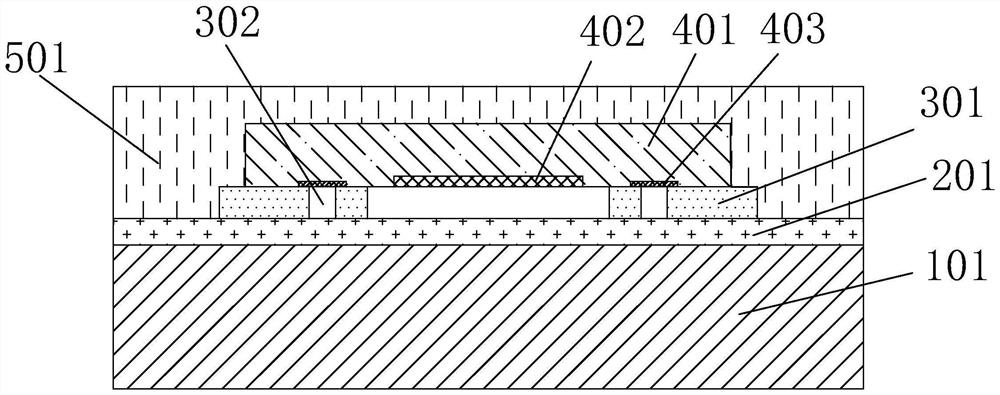

[0051] (1) Reference Figure 1a , providing a carrier wafer 101, the surface of the carrier wafer 101 is covered with an adhesive layer 201 with a thickness of about 100um, the material of the adhesive layer 201 is a thermal foaming film, and the thickness of the adhesive layer 201 is made to be about 5- The barrier layer 301 is 50um. The material of the barrier layer 301 is bondable photoresist or dry film. The barrier layer 301 is patterned to form the second through hole 302. The patterning process includes a photolithography process. By setting the second through hole 302 on the barrier layer 301 to form an alignment structure, the position of the second through hole 302 corresponds to the pad of the filter chip, so that when the filter chip is aligned on the carrier wafer 101 The second throu...

Embodiment 2

[0059] refer to Figure 2a-2e , the embodiment of the present application proposes a method for manufacturing a filter fan-out packaging structure, including the following steps:

[0060] (1) Reference Figure 2a , provide a carrier wafer 111, the surface of the carrier wafer 111 is covered with an adhesive layer 211 with a thickness of about 100um, the material of the adhesive layer 211 is a thermal foaming film, and the thickness of the adhesive layer 211 is 25-50um The barrier layer 311 is made of a bondable photoresist or dry film, and the barrier layer 311 is patterned to form the second through hole 312. The patterning process includes a photolithography process. The alignment structure is formed by setting the second through hole 312 on the barrier layer 311. The position of the second through hole 312 corresponds to the pad of the filter chip 411 on which the first spacer layer 414 has been formed, so that the filter chip is aligned. The second through hole 312 is lo...

Embodiment 3

[0068] refer to Figures 3a-3i , the embodiment of the present application proposes a method for manufacturing a filter fan-out packaging structure, including the following steps:

[0069] (1) Reference Figures 3a-3c Provide a carrier wafer 121, the surface of the carrier wafer 121 is covered with an adhesive layer 221 with a thickness of about 100um, the material of the adhesive layer 221 is a thermal foam film, and the position corresponding to the pad on the adhesive layer 211 is set There is an alignment block 322, and a barrier layer 321 with a thickness of 25-50um is made around the alignment block 322 above the adhesive layer 221. The barrier layer 321 is first made on the adhesive layer 221 and covers the alignment block 322, The barrier layer 321 is planarized so that the surface of the barrier layer 321 is flush with the surface of the alignment block 322 . Specifically, the material of the barrier layer 321 is photoresist, molding material or dry film, and the al...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More