Board-level system-level packaging method and packaging structure

A system-level packaging and board-level technology, which is applied to components of TV systems, manufacturing microstructure devices, and processing microstructure devices, etc., to achieve the effects of high packaging efficiency, improved packaging efficiency, and simple process flow

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] Existing system-in-package approaches still have great challenges. Specifically, taking flip-chip as an example, the existing system-level packaging method has the following disadvantages: 1. The process is complicated, resulting in low packaging efficiency; 2. Each chip needs to be soldered on the solder balls in sequence, and the packaging efficiency is low; 3. . It is necessary to use the welding process to realize the electrical connection between the chip and the circuit board, which is not compatible with the process in the front part of the packaging; 4. When a large pressure is accidentally applied during the process of dipping the flux, it is easy to cause the circuit board to crack.

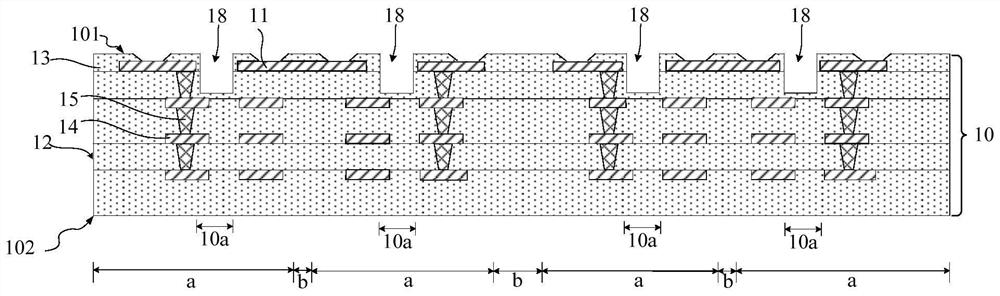

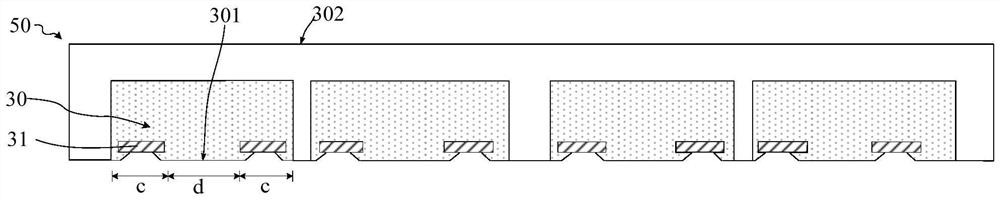

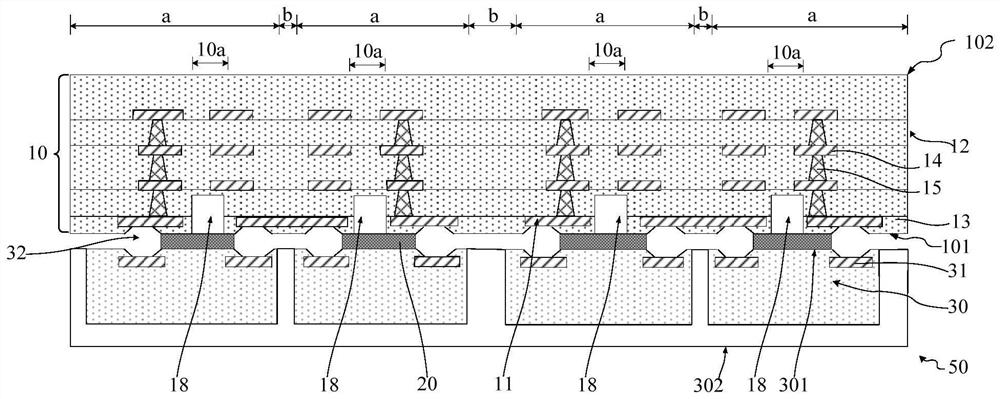

[0017] In order to solve the technical problem, an embodiment of the present invention provides a board-level system-in-package method, including: providing a circuit board including a first surface and a second surface opposite to each other, the circuit board including a bonding...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| height | aaaaa | aaaaa |

| area | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More