Functional chip for 3D chip

A chip and functional technology, applied in the field of functional chips, can solve the problems of large resistance parasitic parameters and capacitance parasitic parameters, long manufacturing cycle, large chip area, etc., to reduce resistance parasitic parameters and capacitance parasitic parameters, reduce production costs, The effect of reducing the area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment 1

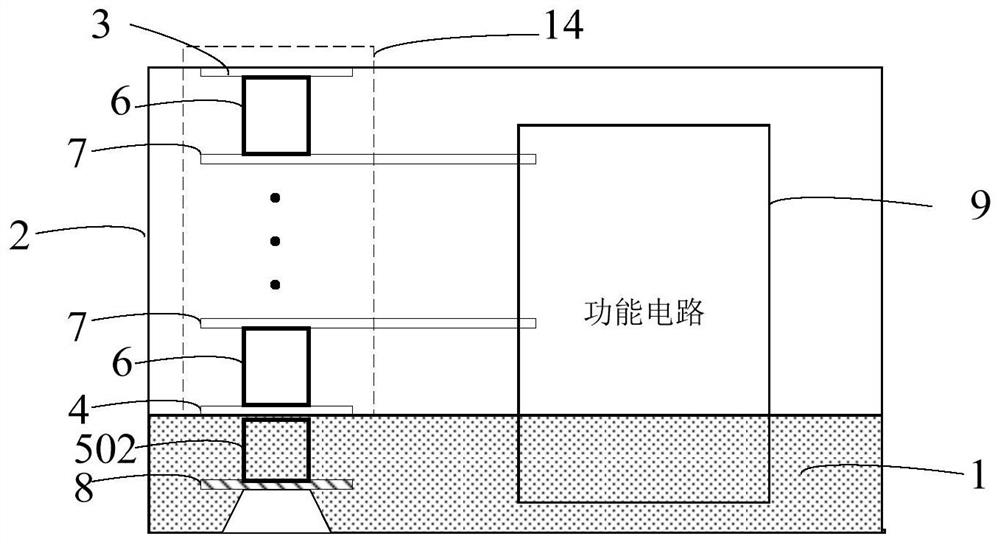

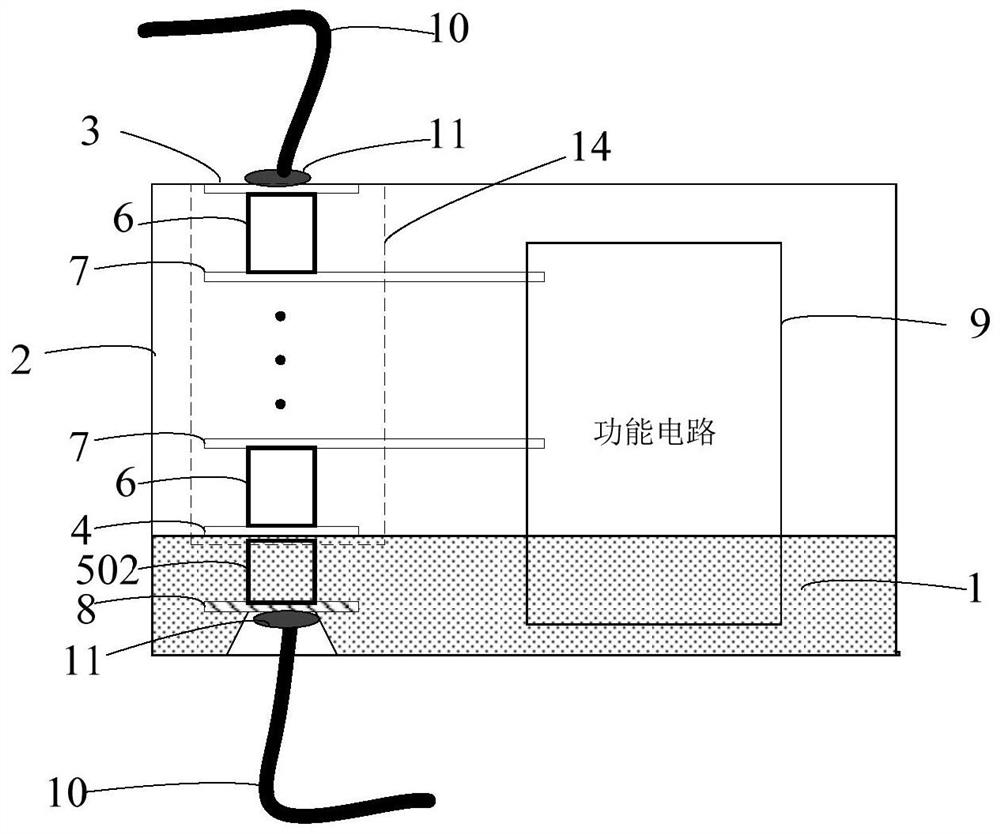

[0161] like figure 2 and image 3 As shown, an embodiment of the present invention provides a functional chip for a 3D chip, including: a substrate layer 1, a metal layer 2, a metal layer through hole component 14, a substrate through hole 5, a substrate conductor member 8, and functional circuit 9.

[0162] The metal layer through-hole component 14 includes: a first conductor part 3 , a second conductor part 4 , a conductor connection hole 6 and an on-chip conductor part 7 .

[0163] Wherein, the metal layer 2 includes a first surface and a second surface arranged opposite to each other, the second surface of the metal layer 2 is arranged on the substrate layer 1; the first conductor part 3 is formed on the first surface of the metal layer 2; the second conductor part 4 is formed on the second surface of the metal layer 2; the substrate through hole 5 is opened on the substrate layer 1, and is connected to the second conductor part 4 of the metal layer 2; the conductor con...

specific Embodiment 2

[0178] like figure 2 and image 3 As shown, on the basis of the specific embodiment 1, improvements or expansions can be made in the conductor connection holes 6 .

[0179] Since the conductor connection holes 6 are usually metal in-chip of a chip and through holes thereof, the conductor connection holes 6 can be connected to the internal circuit as the functional circuit 9 .

[0180] E.g, Figure 4 The functional circuit 9 can process 3D signals (passing through the chip) by connecting certain functional units through metal wires in the chip.

[0181] Functional units can act in the following ways:

[0182] 1. The switching circuit can be added to increase the choice;

[0183] 2. The drive function module can be added;

[0184] 3. The parallel-serial (serial-parallel) conversion function can be added;

[0185] 4. The function of computing with internal signals can be added.

[0186] For switching circuits:

[0187] The core idea of the switching circuit is that the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More