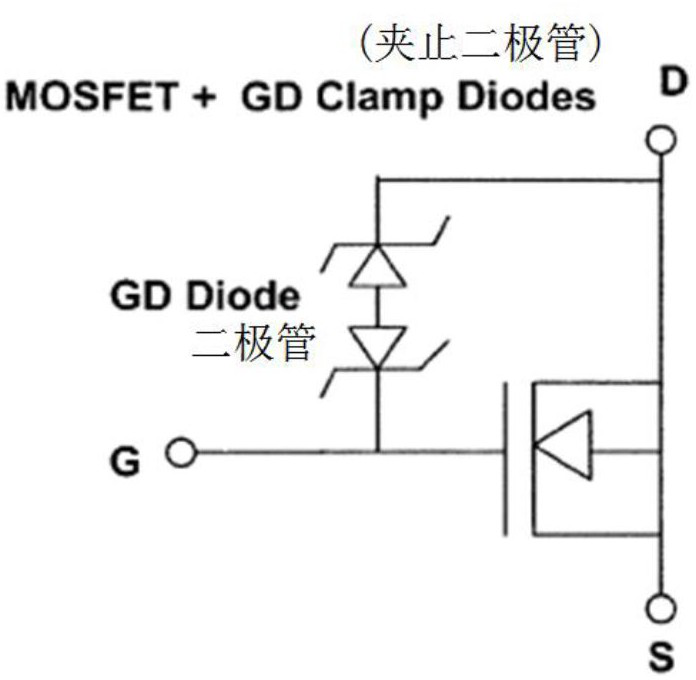

Gate drawing end clamping structure of planar power MOSFET (Metal-Oxide-Semiconductor Field Effect Transistor) device

A planar, high-power technology, applied in the direction of semiconductor devices, electrical components, circuits, etc., can solve problems such as insufficient, reverse collapse voltage influence, etc., to improve the ability of avalanche withstand current and avalanche withstand voltage, high withstand voltage, and ensure reliability The effect of resistance and pressure resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0034] like Figure 9 As shown, a planar power MOSFET device with a gate-drain clamping structure, comprising:

[0035] N-type epitaxial layer 1, a first P-well region 2 and a second P-well region 5 are formed in the N-type epitaxial layer 1, and the first P-well region 2 and the second P-well region 5 are integrally connected, wherein , the first P-well region 2 is located in the terminal region, the second P-well region 5 is located in the active region, the distribution material of the first P-well region 2 is boron, and the overall concentration of boron is 10 13 cm -2 level, the distribution material of the second P-well region 5 is boron, and the overall concentration of boron is 10 15 cm -2 grade;

[0036] Field oxide layer 3, the field oxide layer 3 is located on the upper surface of the N-type epitaxial layer 1 in the terminal region, and the thickness of the field oxide layer 3 is 1.0-2.5 μm;

[0037] A gate oxide layer 3-1, the gate oxide layer 3-1 is located ...

Embodiment 2

[0053] The gate and drain end clamping structure in Embodiment 2 is the same as that in Embodiment 1, and the structure of its terminal area is a VLD structure, such as Figure 10 As shown, a first P-well region 2 is formed in the N-type epitaxial layer 1, and the bottom edge of the first P-well region 2 is a multi-arc structure.

Embodiment 3

[0055] The gate and drain end clamping structure in Embodiment 3 is the same as that in Embodiment 1, and the structure of the terminal area is a dummy ring structure, such as Figure 11 As shown, several spaced first P-well regions 2 are formed in the N-type epitaxial layer.

[0056] The gate-drain clamping structure of the present invention is suitable for any existing power metal oxide semi-field effect transistor, as long as the polysilicon layer 4 is continuously surrounded from the inner gate metal layer 7-2 to the other end and the outer The ring-drain metal layer 7-1 is connected, and the polysilicon layer 4 is designed so that a plurality of N-type polysilicon layers 4-2 and a plurality of P-type polysilicon layers 4-1 are continuously interleaved with each other.

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More