In-situ metal barrier deposition of sputter etching on interconnect structure

An etching and metal layer technology, applied in the direction of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve problems such as damage and wafer damage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

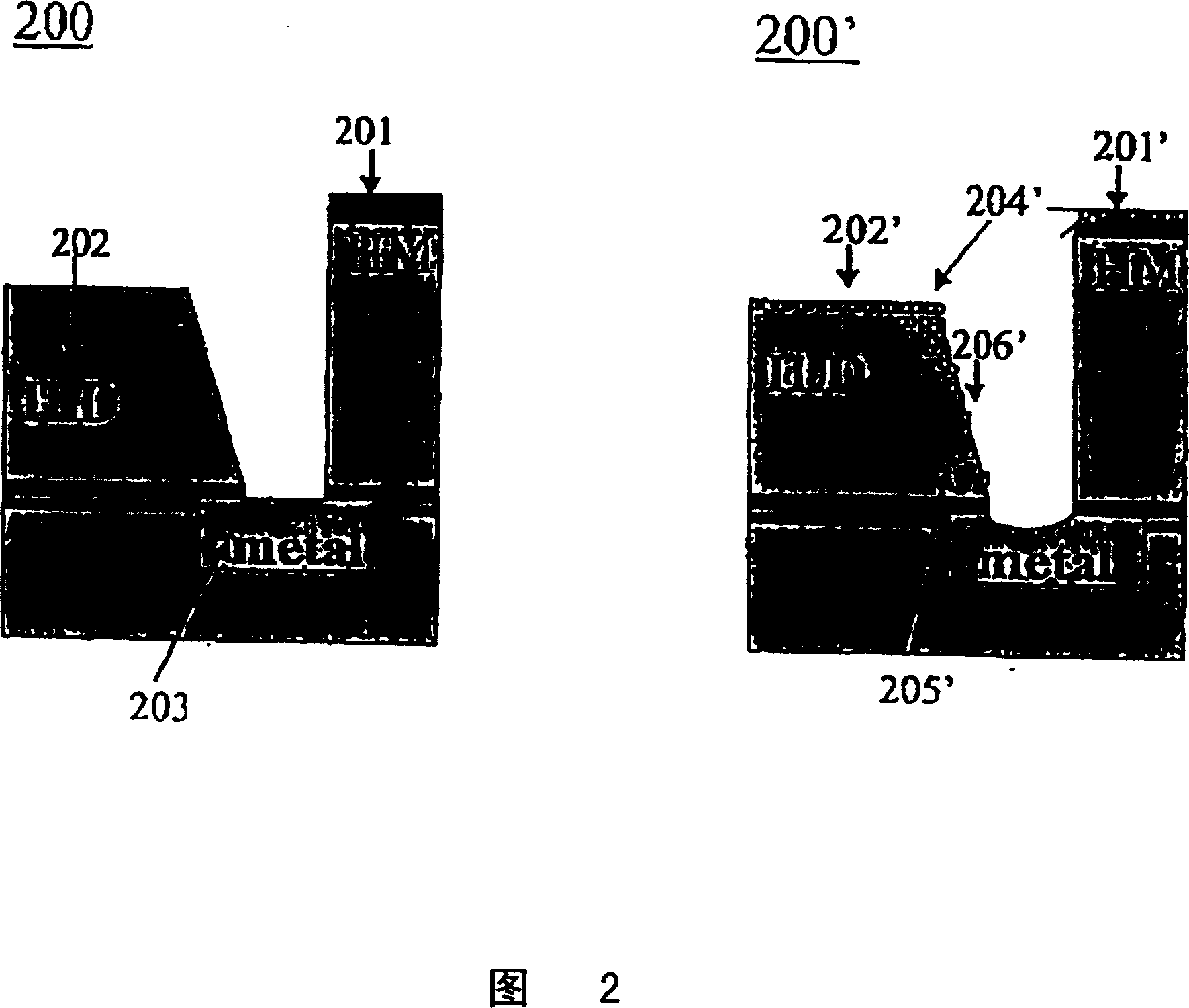

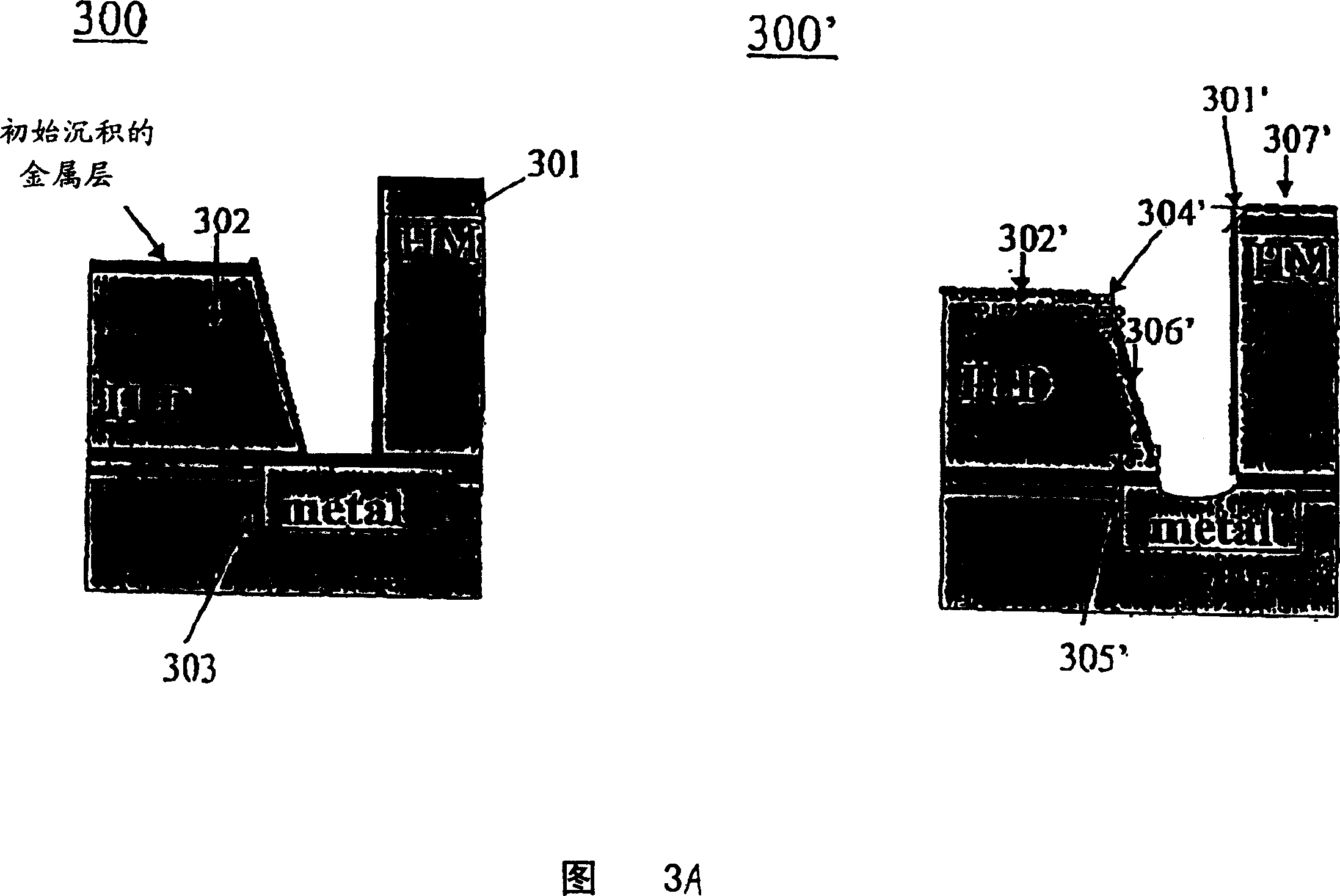

[0038] In accordance with embodiments of the present invention, gas sputtering cleaning procedures are provided to be performed on a patterned wafer that avoids or minimizes damage to the hard mask or to the IDL without compromising the etch profile Significant changes or spilled metal underneath onto the IDL.

[0039] In addition, an embodiment of the present invention provides a semiconductor device manufacturing method that advantageously utilizes a single deposition chamber.

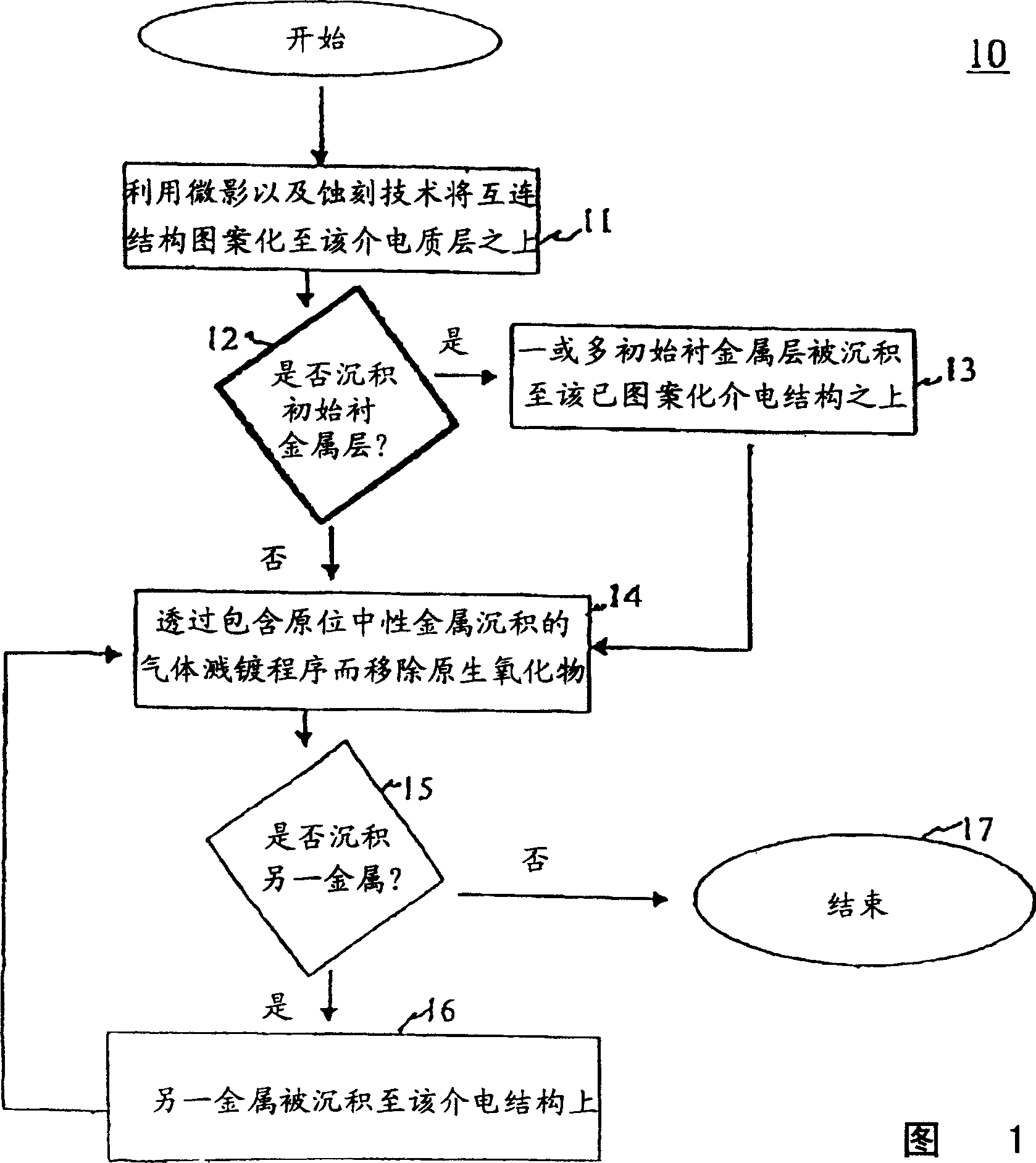

[0040] As shown in flow diagram 10 in Fig. 1, the process begins with a semiconductor device (wafer) (not shown) having a dielectric layer on which micro An interconnect structure etched by lithography or etching techniques 11, such lithography and etching are well known in the art, the wafer is placed in a deposition chamber (not shown).

[0041] Then, it is determined whether the initial metal layer is to be deposited 12, if no initial metal layer is required, then the wafer can be placed in the d...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More