Cmbined circuit equipment checking method based on satisfiability

A testing method and combined circuit technology, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve complex problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

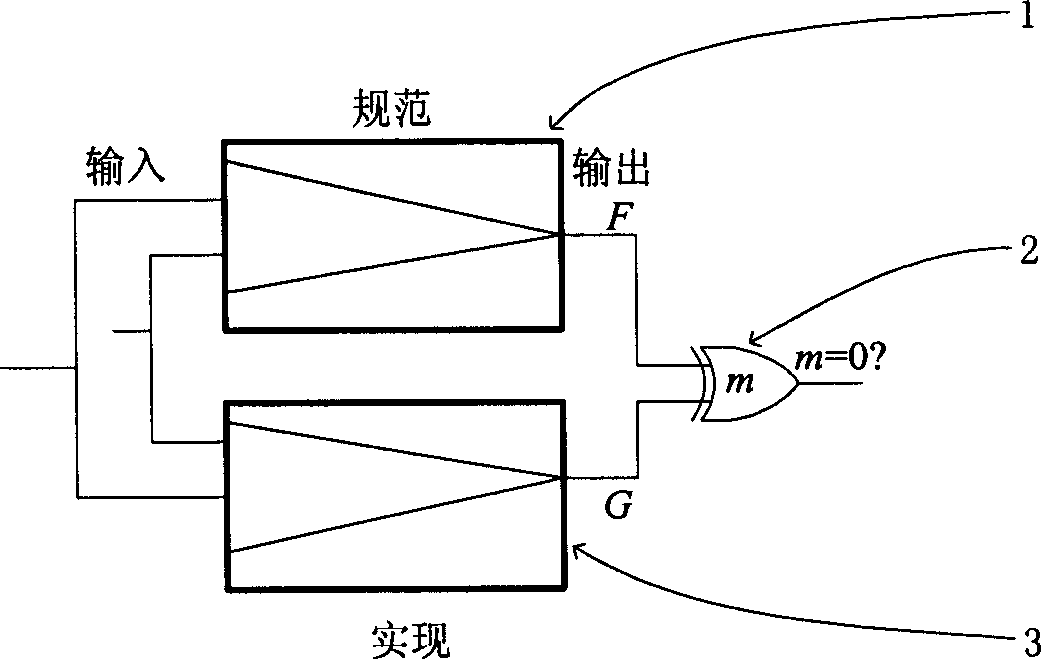

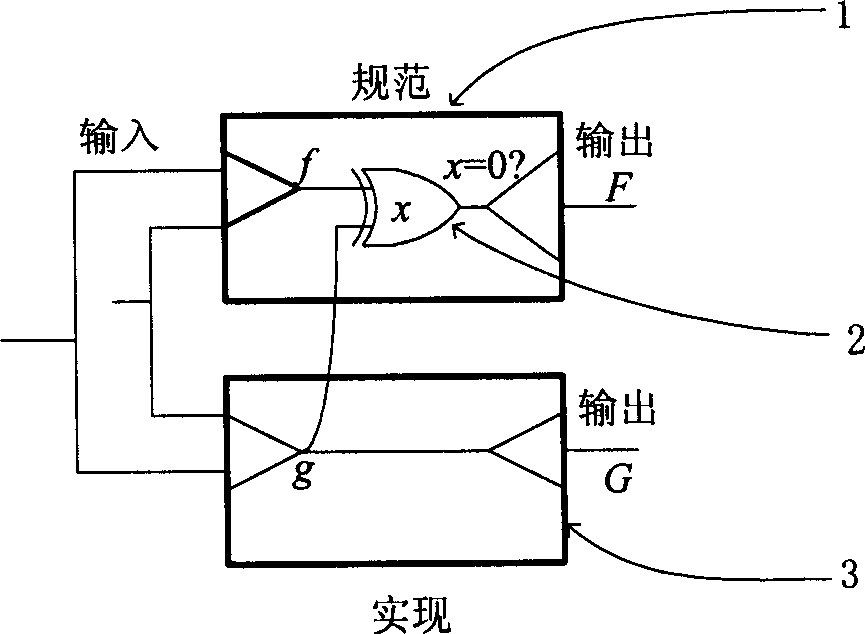

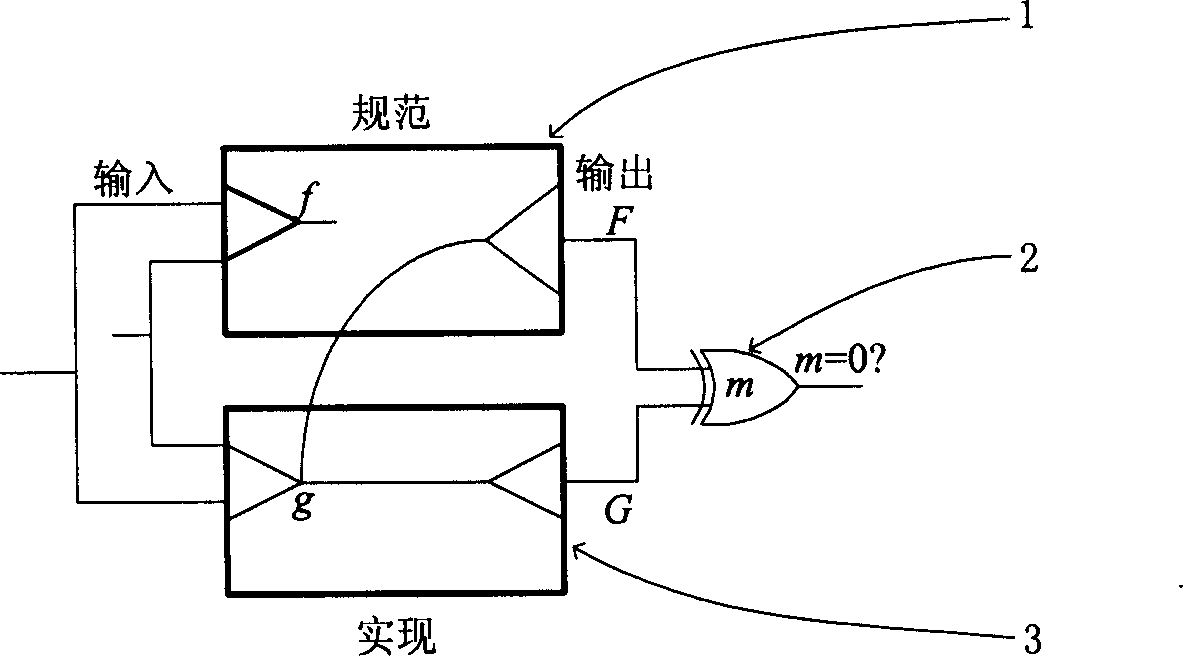

[0025] The meanings of each label in the accompanying drawings are as follows:

[0026] 1: The corresponding box represents the design specification circuit.

[0027] 2: XOR gate.

[0028] 3: The corresponding box represents the implementation circuit.

[0029] 4: AND gate.

[0030] 5: OR gate.

[0031] 6: NOT gate.

[0032] In addition, with Figure 4 Among them, S1, S2, S3, S4, and S5 respectively correspond to the five steps in the technical invention scheme.

[0033] attached figure 1 Among them, (1) represents the design specification circuit. (3) represents the implementation circuit. In order to verify the equivalence of two corresponding signals, it is only necessary to connect the two signals to an XOR gate (2), and then prove that the output of the XOR gate is fixed at 0, and the fault cannot be tested. It is worth noting that when using the satisfiability algorithm to verify, it is not necessary to realize this physical connection, but only to construct the c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More