Low leakage heterojunction vertical transistors and high performance devices thereof

A technology of field effect transistors and vertical channels, which is applied in the direction of transistors, semiconductor devices, semiconductor/solid-state device manufacturing, etc., and can solve problems such as short channel effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

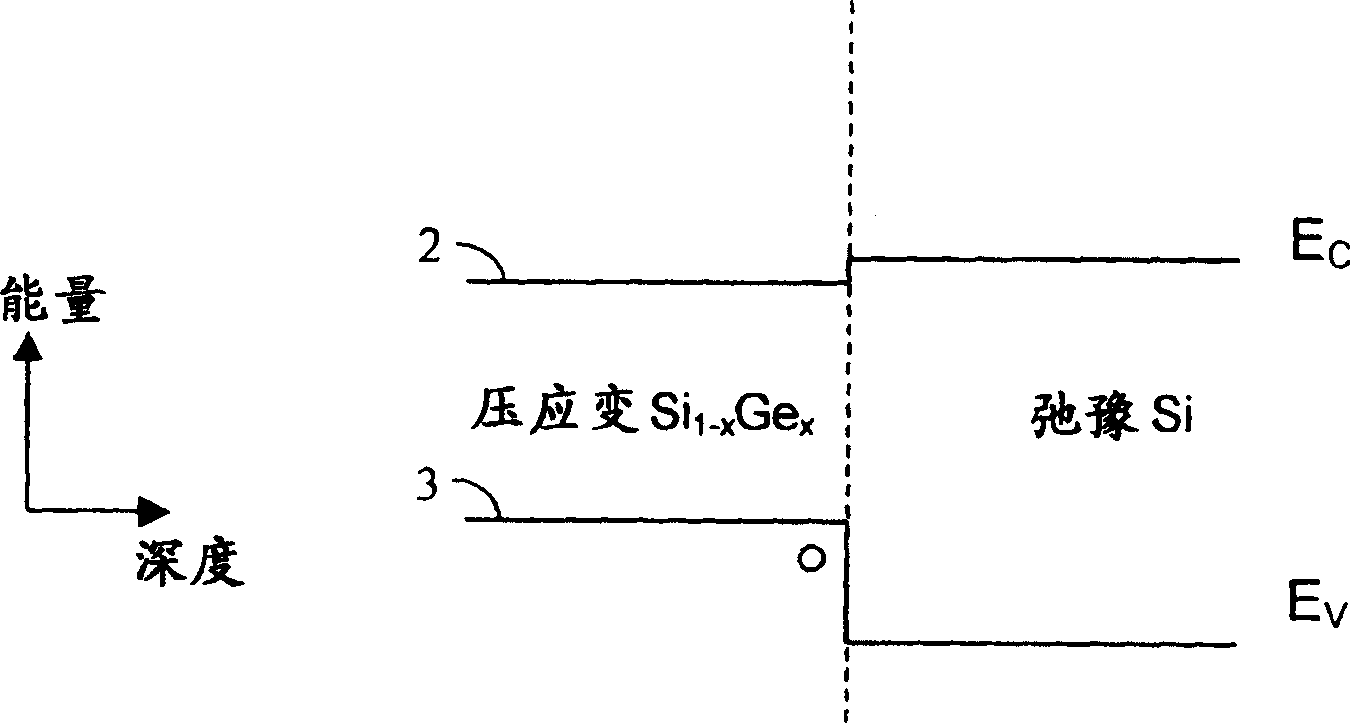

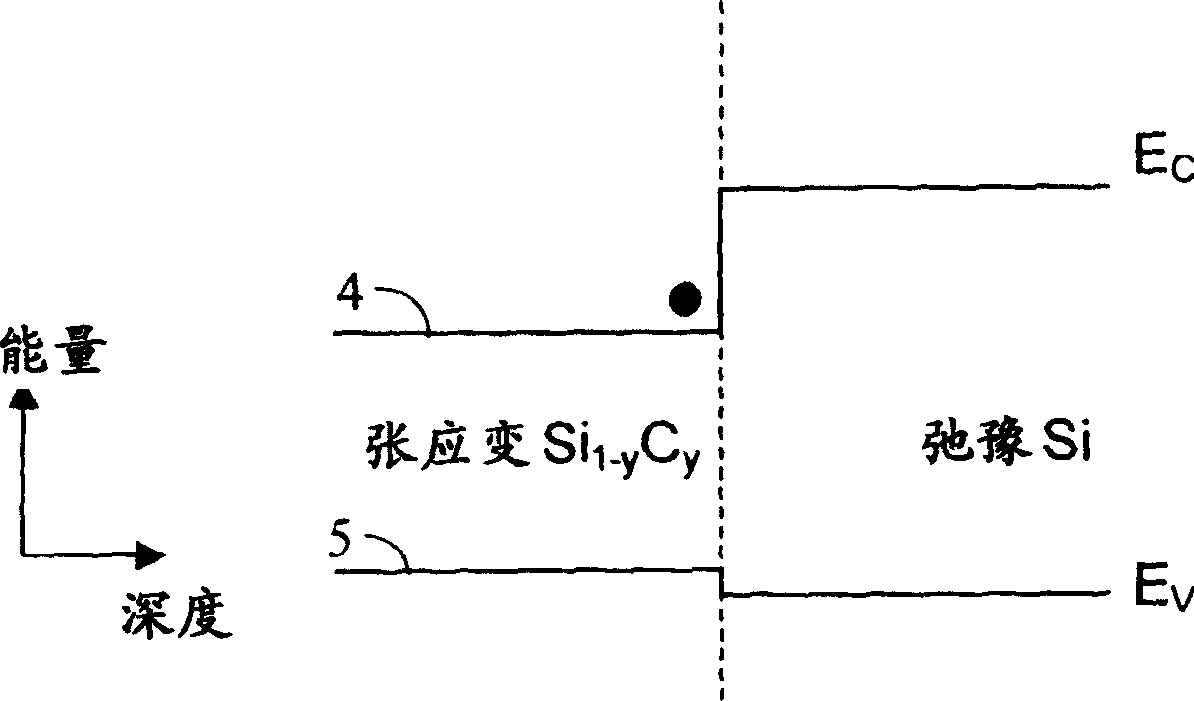

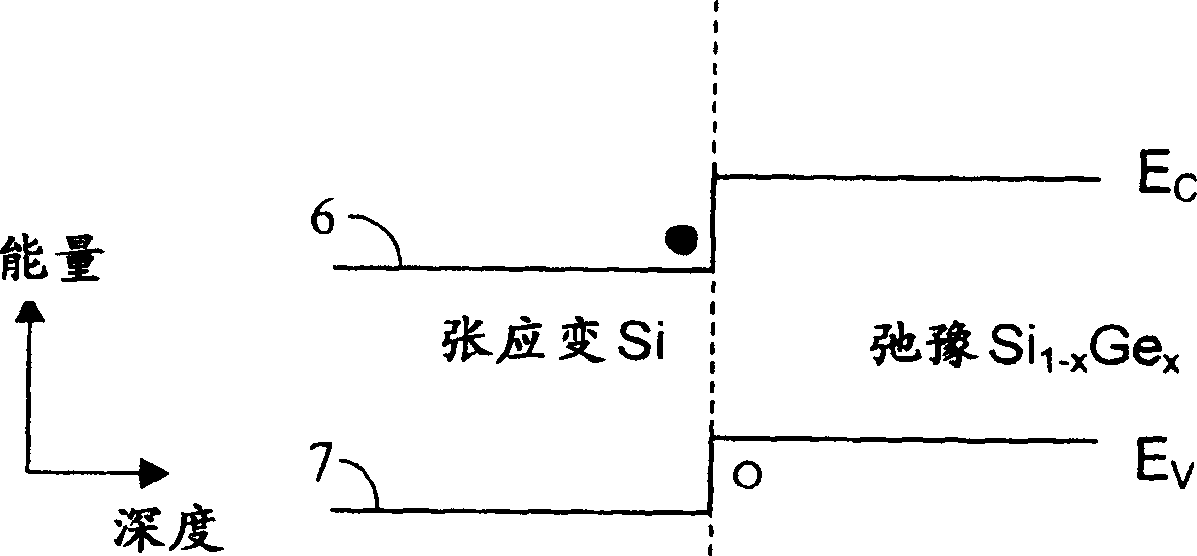

[0029] The lattice constants of carbon, silicon, and germanium are 3.567 angstroms, 5.431 angstroms, and 5.646 angstroms, respectively. In pseudomorphic SiC on relaxed Si, or pseudomorphic Si on relaxed SiGe or Ge substrates, there is biaxial tensile strain, which means that in pseudomorphic materials, in the growth plane (surface) the lattice The constant is larger and the lattice constant is smaller along the growth direction (perpendicular to the surface). On the other hand, in pseudomorphic SiGe on relaxed Si, or pseudocrystalline Ge on relaxed SiGe, there is compressive strain, which means that in pseudomorphic materials, the lattice constant is much lower in the growth plane (surface). Small and larger along the growth direction (perpendicular to the surface) lattice constant. The addition of small amounts of carbon (figure 1 The conduction and valence bands of compressively strained SiGe or SiGe(C) on relaxed silicon are shown by curves 2 and 3, respectively. The hole...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More