Strained FinFET CMOS device structures

A device structure, semiconductor technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, transistors, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0015] The invention aims to provide a novel FinFET semiconductor device structure and a manufacturing method thereof. A preferred final structure according to the invention is shown in Figure 16 , 17 middle.

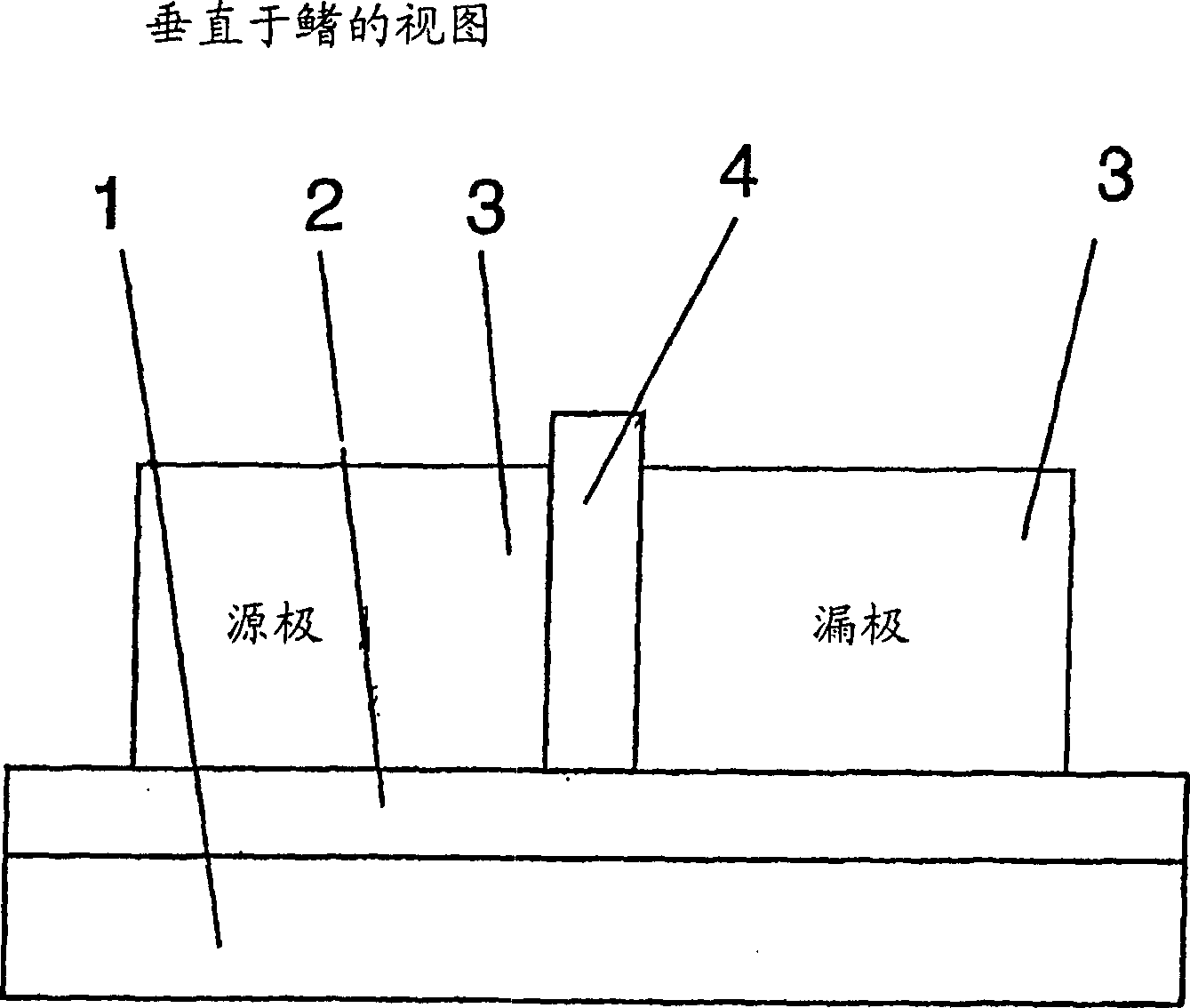

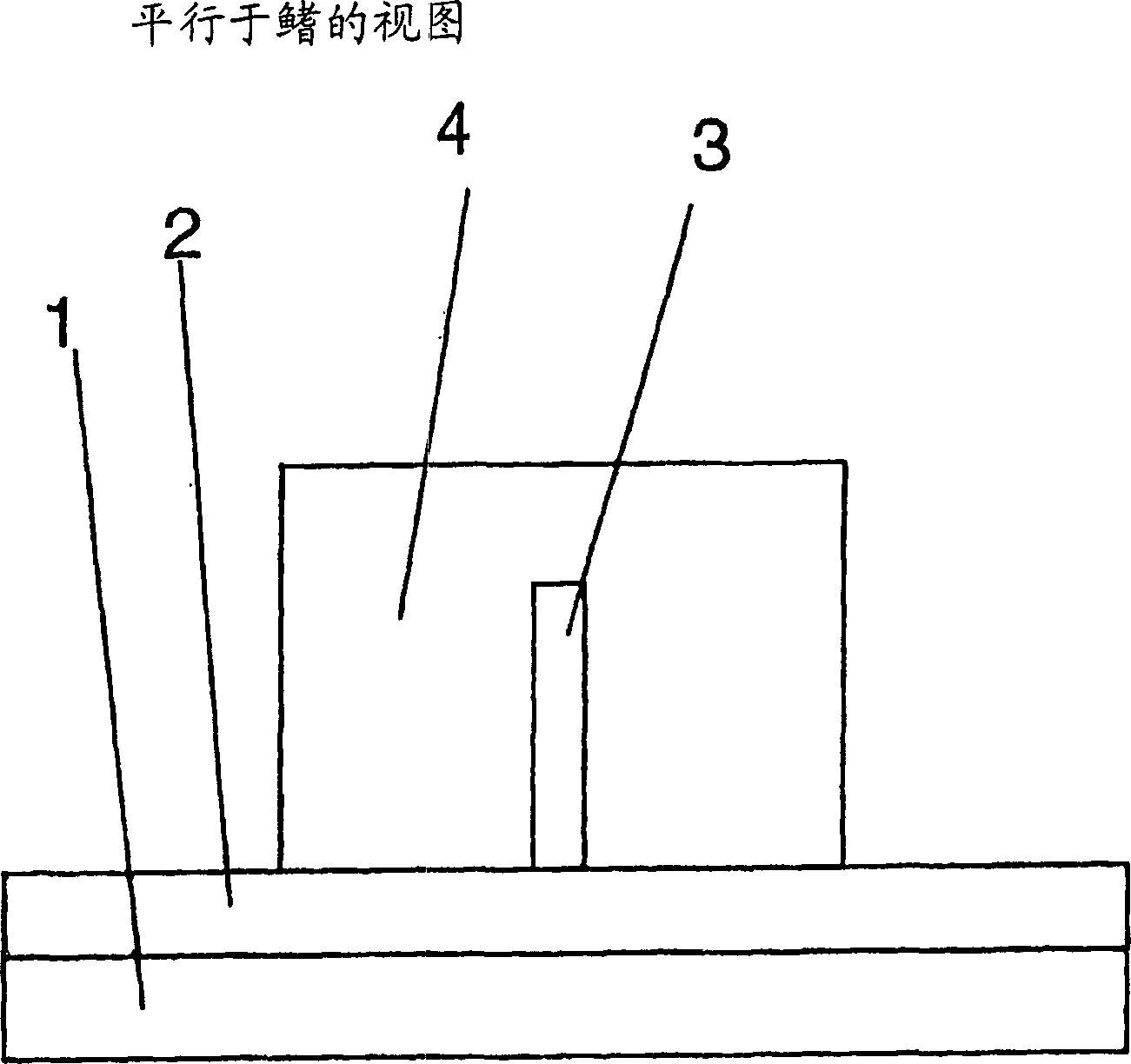

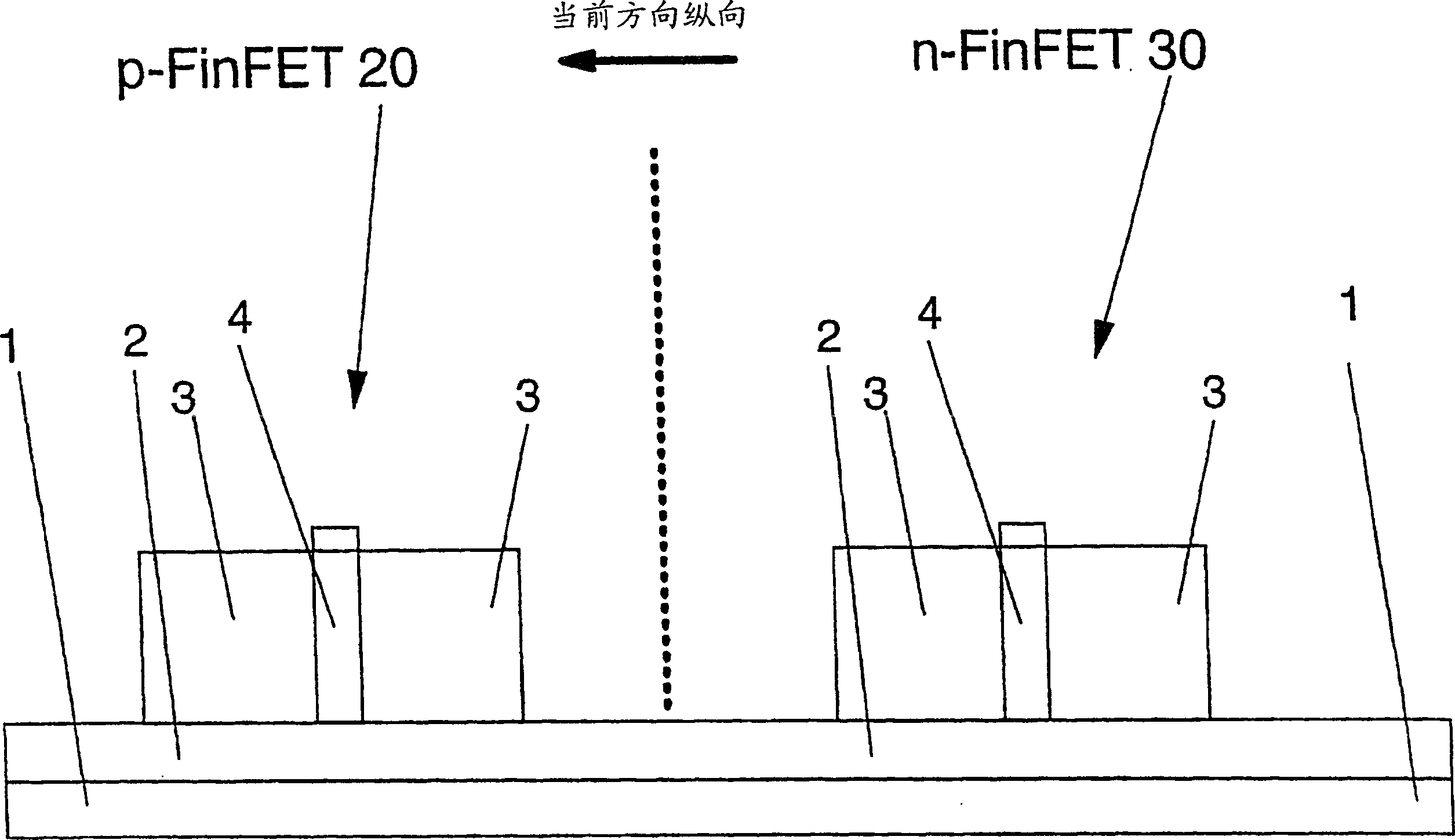

[0016] Referring now to the remaining figures, in particular Figures 1 to 3, a known FinFET device (Figures 1, 2) and device structure (Figure 3) is shown.

[0017] First, standard or conventional FinFET device fabrication processes are performed: patterning and etching fins; forming gate dielectric and conductors, sidewall spacers (not shown); doping source / drains; and salicide ( salicide). After salicide, the gate sidewall spacers are removed to facilitate the processing that will induce strain in the fins according to the present invention.

[0018] More specifically, as described with reference to FIG. 3 , for example, an SOI wafer is provided. The SOI wafer consists of a SiO 2 The substrate 1 under the buried layer 2 is shown in FIG. 3 . In SiO 2 Above the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More