Voltage level conversion circuit

A technology for transforming circuits and voltage levels, which is applied in logic circuit connection/interface layout, electrical components, electronic switches, etc. It can solve problems such as low threshold value, difficult to withstand high-voltage series transistors, and obstacles to miniaturization of low-power transistors. , to achieve the effect of high speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

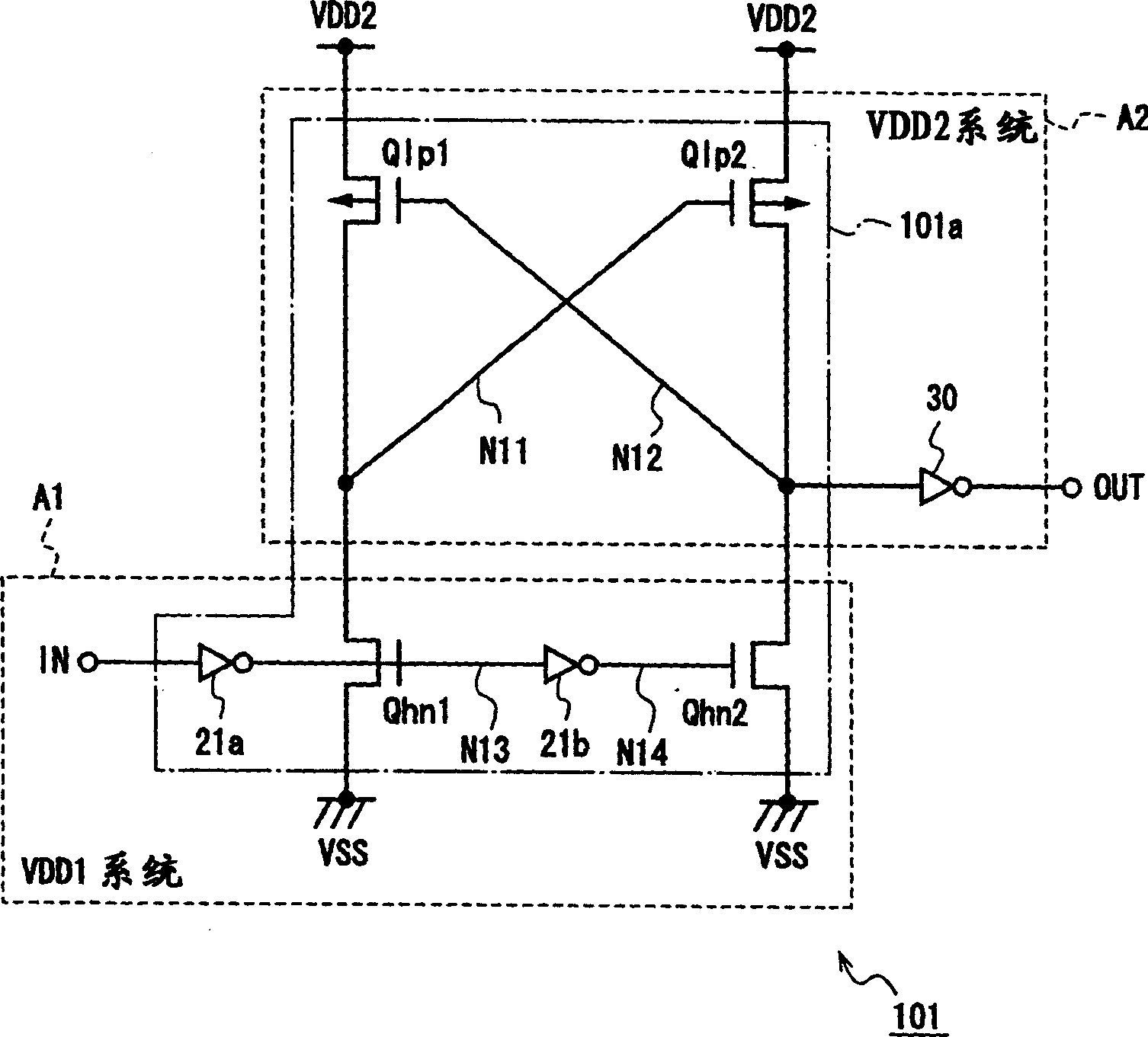

[0046] figure 1 It is a circuit diagram illustrating a voltage level conversion circuit according to Embodiment 1 of the present invention.

[0047] The voltage level conversion circuit 101 of the first embodiment converts an input signal having a logic voltage level of a high power supply voltage system (VDD1 system) into an output signal having a logic voltage level of a low power supply voltage system (VDD2 system) output circuit. This voltage level conversion circuit 101 is composed of a high-voltage resistant N-channel MOS transistor and a low-voltage resistant P-channel MOS transistor whose threshold value is lower than that of the transistor, and has a system of inputting VDD1 only to the gate of the high-voltage resistant N-channel MOS transistor. The input signal level shifter outputs the input signal level-shifted by the level shifter to a circuit driven by a low power supply voltage, so that the power supply voltage of the VDD2 system can be lowered.

[0048] f...

Embodiment approach 2

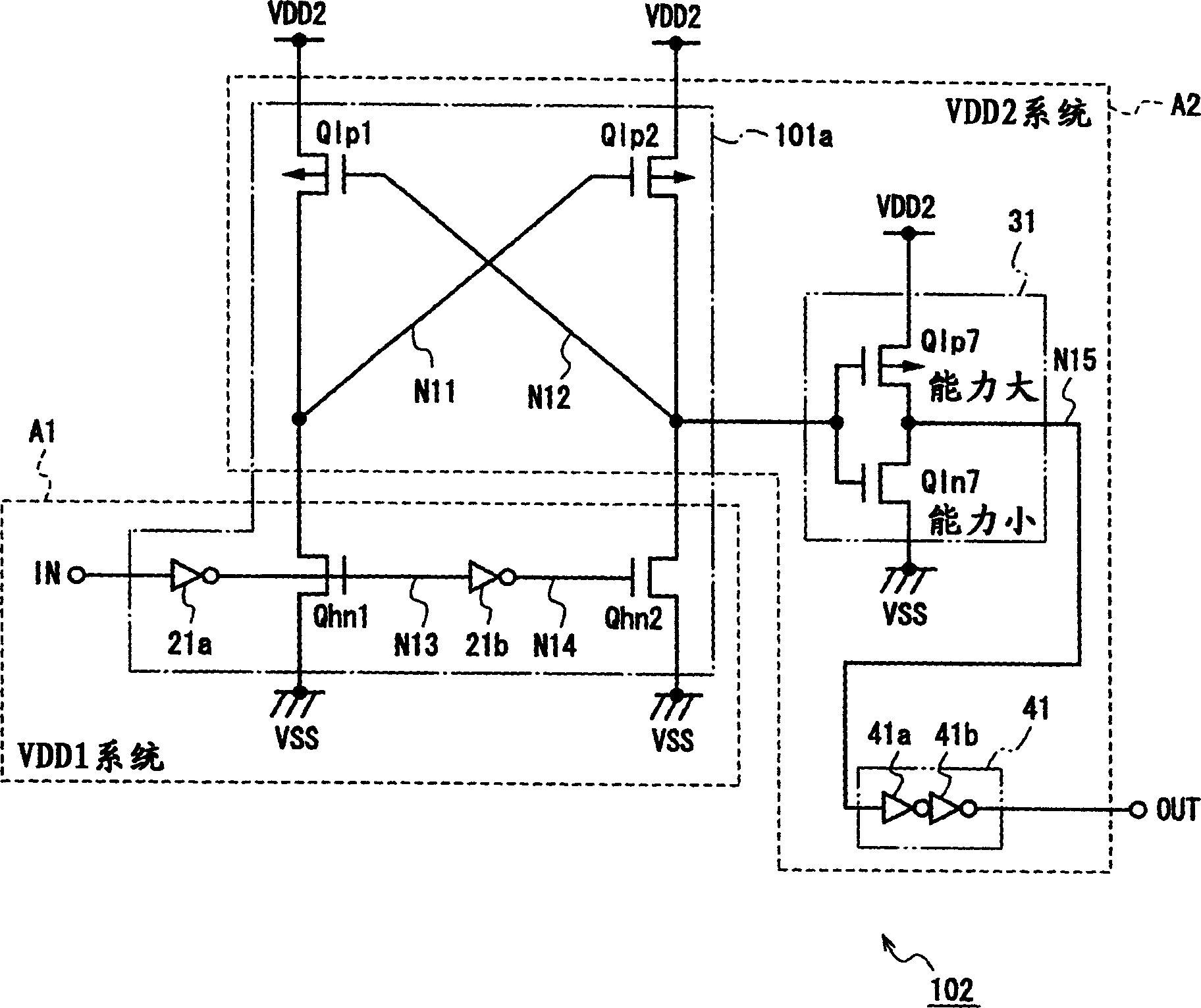

[0059] figure 2 It is a circuit diagram illustrating a voltage level conversion circuit according to Embodiment 2 of the present invention.

[0060] The voltage level conversion circuit 102 of the second embodiment has a negation circuit 31 for adjusting the balance of transistor capabilities in the level conversion unit 101a instead of the negation circuit 30 of the voltage level conversion circuit of the first embodiment. The output circuit 41 outputs the output signal of the negation circuit 31.

[0061] figure 2 Among them, the voltage level conversion circuit 102 has a level conversion unit 101a having the same configuration as that of the first embodiment, a negation circuit 31 for inverting a signal output from the level conversion unit 101a, and a “NEGAT” output to the negation circuit 31. The output circuit 41 that outputs the "signal after waveform shaping. The negation circuit 31 is composed of a third P-channel MOS transistor Q1p7 and a third N-channel MOS tra...

Embodiment approach 3

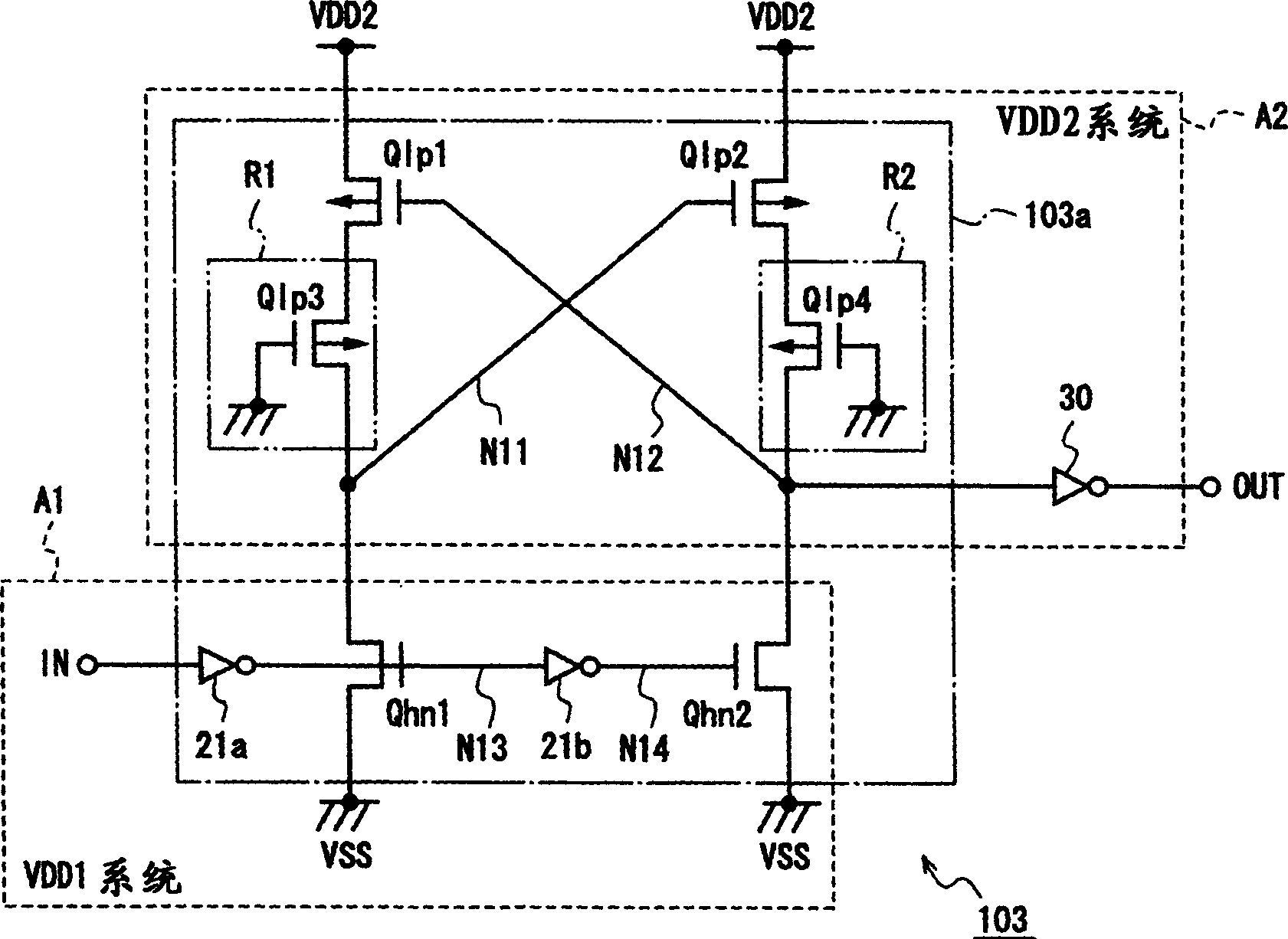

[0071] image 3 It is a circuit diagram illustrating a voltage level conversion circuit according to Embodiment 3 of the present invention.

[0072] The voltage level conversion circuit 103 of the third embodiment includes a level conversion unit 103a instead of the level conversion unit 101a of the voltage level conversion circuit of the first embodiment.

[0073] The level conversion unit 103a of the voltage level conversion circuit according to the third embodiment is configured by inserting a resistor R1 between the first connection node N11 of the level conversion unit 101a of the first embodiment and the first P-channel MOS transistor Q1p1. A resistor R2 is inserted between the second connection node N12 of the level conversion unit 101a and the second P-channel MOS transistor Q1p2.

[0074] Here, resistor R1 is composed of P-channel MOS transistor Q1p3 connected in series between first connection node N11 and first P-channel MOS transistor Q1p1, and having a gate conne...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More