A vertical dual diffused MOS power device protected by polysilicon ESD structure

A technology of oxide semiconductor and vertical double diffusion, which is applied in semiconductor devices, semiconductor/solid-state device parts, electric solid-state devices, etc. High-level problems, to achieve the effect of preventing damage, improving ESD resistance, and avoiding failure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027]By adopting the polysilicon ESD protection structure of the invention, an anti-ESD VDMOS power device with excellent performance can be obtained. It can be applied to common power devices such as double diffused field effect transistors, insulated gate bipolar power transistors, and electrostatic induction transistors. Irradiation-hardened VDMOS devices protected by polysilicon ESD structures can be used in aerospace, nuclear environments and other fields that require high device performance. With the development of semiconductor technology, more anti-ESD power devices with high reliability and easier operability can be produced by adopting the invention.

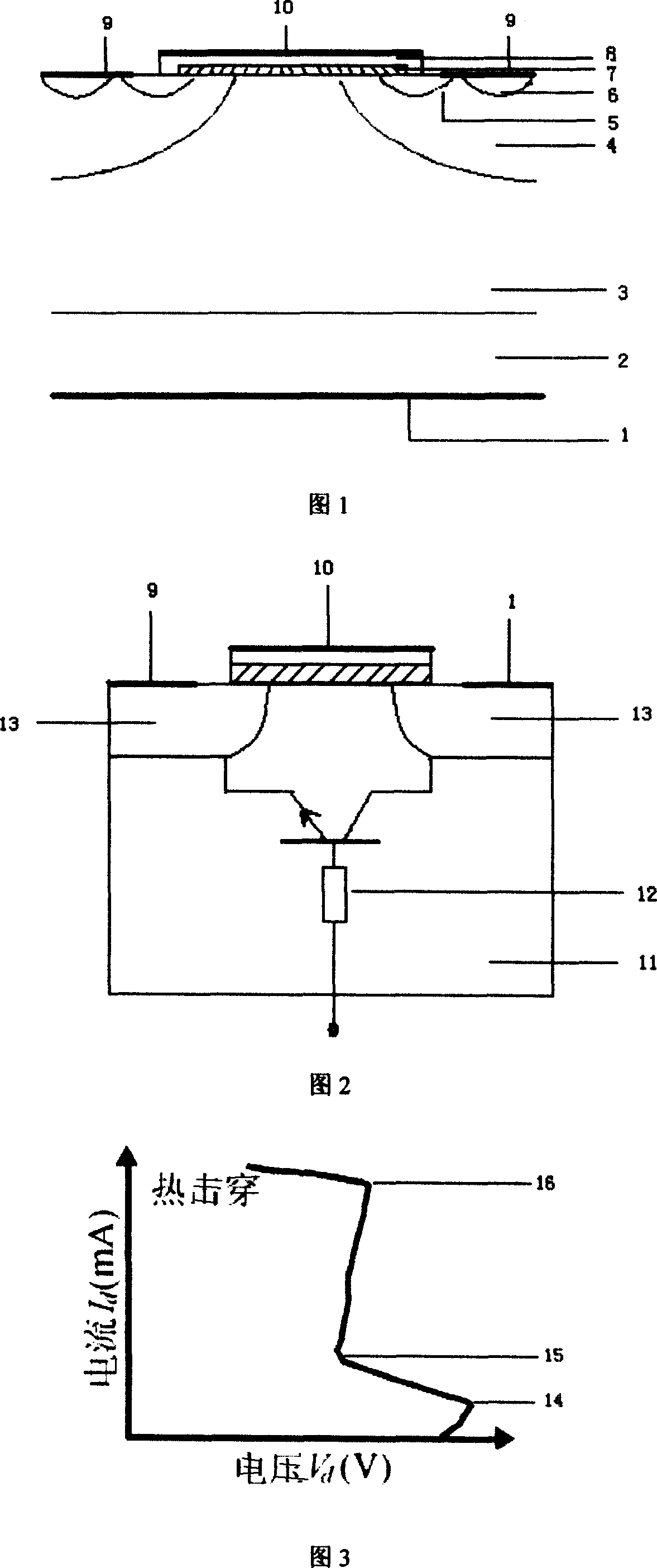

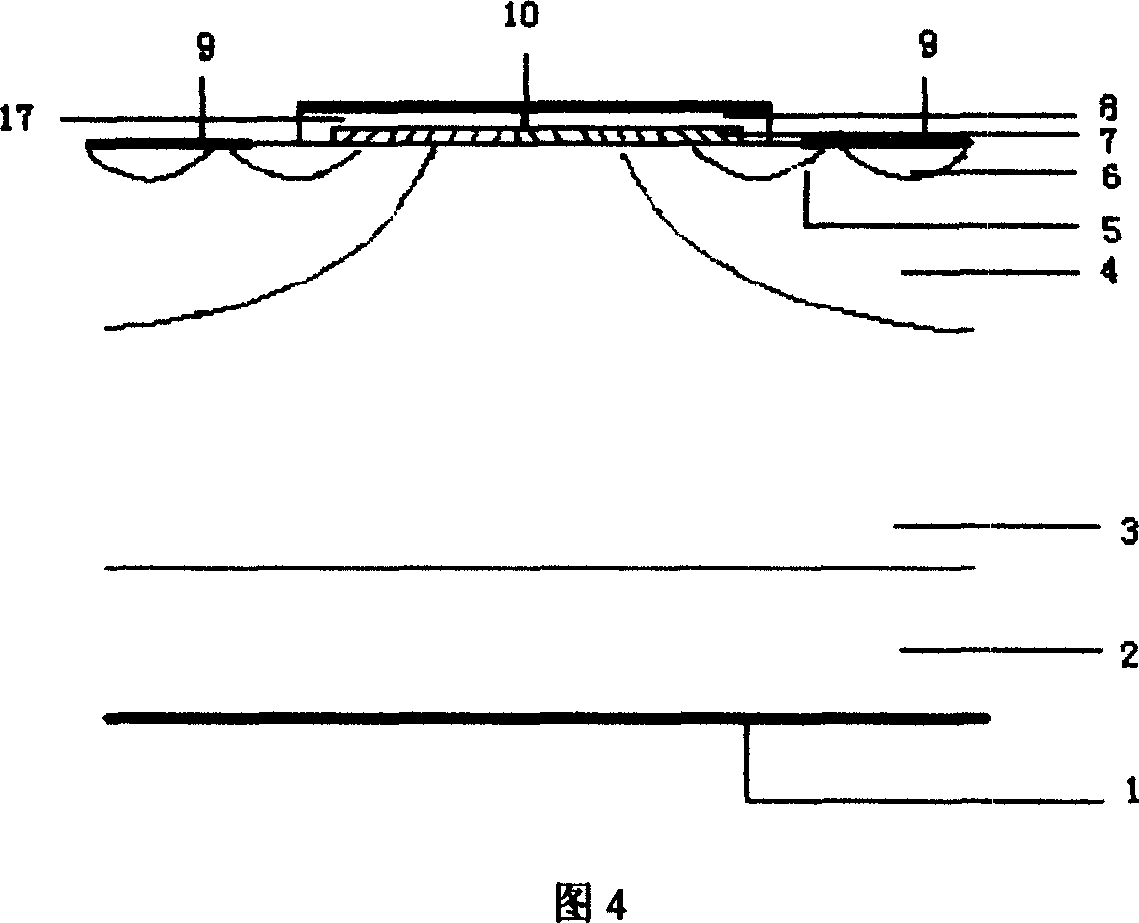

[0028] The VDMOS power device that introduces polysilicon ESD structure protection, as shown in Figure 4, includes the drain 1, n + (or p + ) substrate area 2, n - (or p - ) epitaxial layer 3, p (or n) region 4, n + (or p + ) zone 5, p + (or n + ) region 6, silicon dioxide layer 7, n (or p) doped polysilicon l...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com