Adhesion between dielectric materials

a dielectric material and adhesive technology, applied in the direction of ceramic layered products, transportation and packaging, chemistry apparatus and processes, etc., can solve the problems of affecting the switching speed of transistors, affecting the performance and reliability of chips, and poor yield at assembly and packaging

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

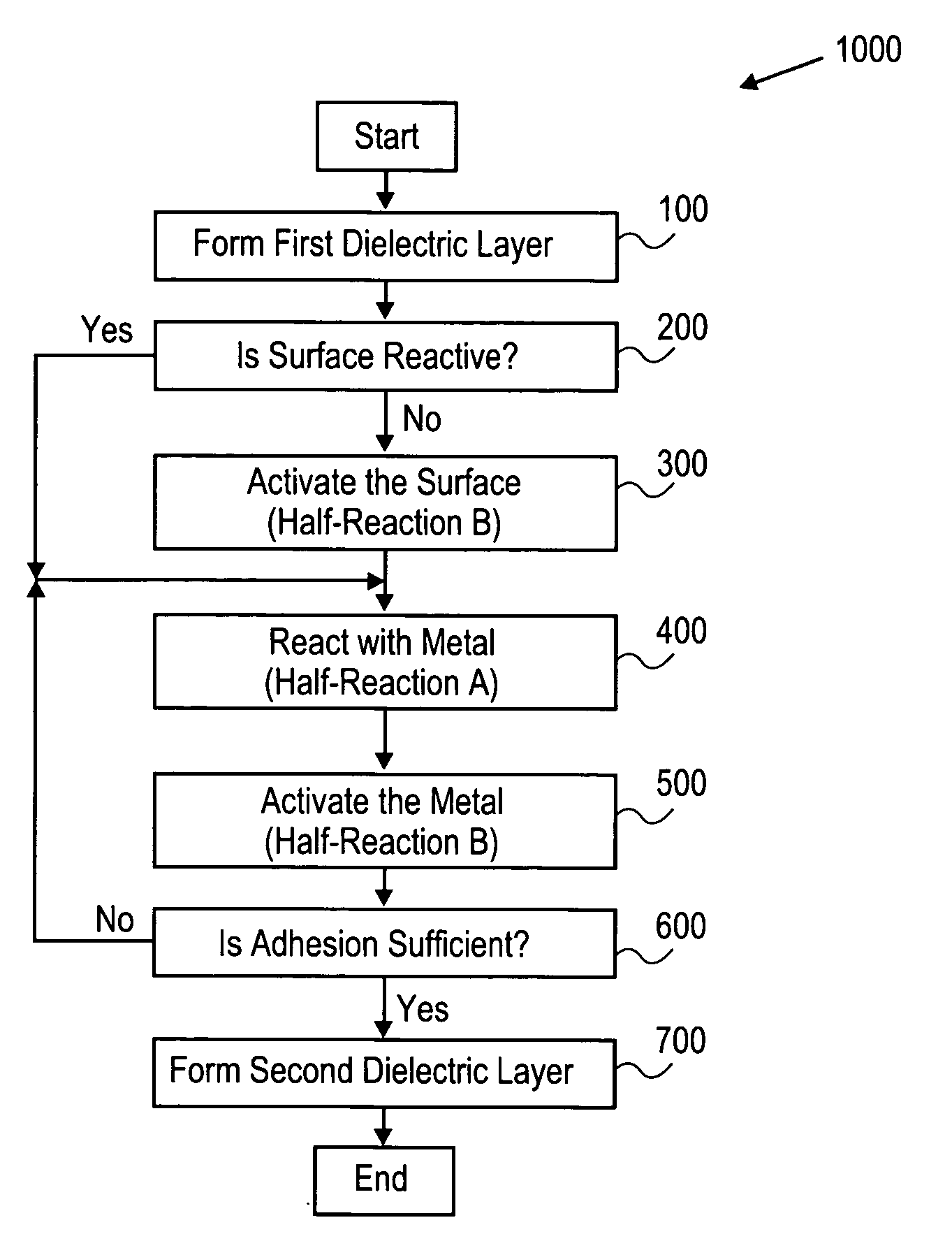

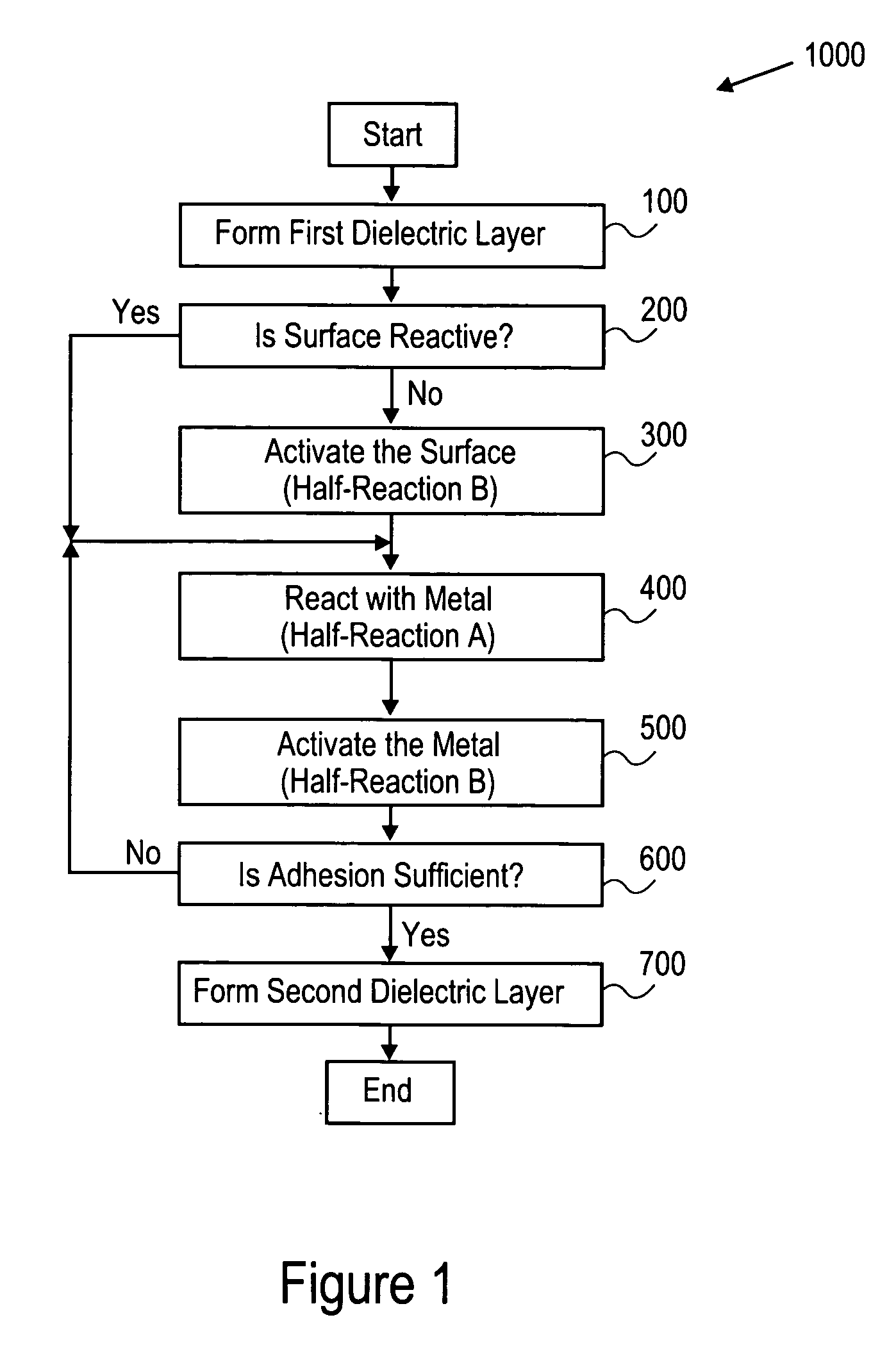

Method used

Image

Examples

first embodiment

[0127] In the present invention, the CMP process involves three polishes. Each polish includes optimization of the polish rates and the polish selectivity by using a different combination of slurry, pad, and polish tool parameters. The first polish removes most of the overburden of the conductor layer 700. The second polish planarizes the remaining conductor layer 700 and the portion of the seed layer 650 that is located over the barrier layer 630. The polish rate of the conductor layer 700 in the first polish and the second polish may be selected from a range of about 900-13,000 Angstroms per minute. The third polish removes the portion of the barrier layer 630 that is located over the upper surface 547 of the ILD 300.

[0128] The polish rate of the barrier layer 630 may be selected from a range of about 100-1,000 Angstroms per minute. In an embodiment of the present invention, the polish of the barrier layer 630 may be highly selective relative to the ILD 300. A selective process pr...

second embodiment

[0130] In the present invention, the CMP process involves two polishes. The first polish removes all of the overburden of the conductor layer 700 and planarizes the conductor layer 700 and the portion of the seed layer 650 that is located over the barrier layer 630. The second polish removes the portion of the barrier layer 630 over the upper surface 547 of the ILD 300.

third embodiment

[0131] In the present invention, the CMP process involves one polish to remove all of the overburden of the conductor layer 700, as well as the portions of the seed layer 630 and the barrier layer 650 that are located over the ILD 300.

[0132] The material and mechanical properties of the ILD 300 must be sufficient to prevent any deformation, fracture, or delamination of the ILD 300 during the CMP process that is used to planarize the conductor layer 700. Otherwise, electrical shorts and other polish-induced defects may occur, thus degrading yield.

[0133] The mechanical strength of the ILD 300 depends on the mechanical strength of the bulk material forming the ILD 300. If the ILD 300 is porous, the mechanical strength of the ILD 300 also depends on the porosity and the pore size, shape, and distribution. Young's modulus of elasticity is a measurement of mechanical strength of a material. In a first embodiment, the ILD 300 is porous with a Young's modulus of elasticity of about 3 GigaPa...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| temperature | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More